独立网桥测试方法

文献发布时间:2023-06-19 11:39:06

技术领域

本发明涉及一种测试方法,尤其涉及一种能对存储装置执行读写测试能力的独立网桥测试方法。

背景技术

当前业界对固态硬盘(SSD)执行读写测试(Bur-in Test)的方式,都需要与计算机主机进行通信连接,同时搭配接口网桥作为通信接口的转换,例如计算机主机的USB接口与SSD的SATA接口或PCIE接口之间的转换。此时,计算机主机才能对SSD执行读写的测试。一般而言,计算机主机在执行读写测试时,乃是先产生测试数据,接着将测试数据经由USB接口发送至接口网桥,然后再经由SATA接口或PCIE接口发送至SSD。同样的,计算机主机要对SSD读取数据时,需先产生读取指令,并经由USB接口发送至接口网桥,然后再经由SATA接口或PCIE接口发送至SSD。当SSD收到读取指令后,将接收到的数据经由SATA接口或PCIE接口发送至接口网桥,再经由USB接口发送至计算机主机。

然而,设置计算机主机不仅会提高测试的成本,占用测试的空间,更增加往返通信延迟时间(round-trip delay time)。因此,如何提供一种在不需要计算机主机的环境之下,直接对SSD进行读写测试,将是本案所要着重的问题与解决的重点。

发明内容

有鉴于此,本发明实施例提供一种独立网桥测试方法,适用于独立网桥装置,独立网桥装置耦接于存储装置,独立网桥装置包括网桥控制器,存储装置包括装置控制器及耦接至装置控制器的装置内存,独立网桥测试方法包括,网桥控制器产生握手测试信号,并将握手测试信号发送至装置控制器;装置控制器根据握手测试信号,以产生确认测试信号,并将确认测试信号发送至网桥控制器;网桥控制器根据确认测试信号,以产生测试数据,并发送写入指令至装置控制器,以将测试数据写入至装置内存;以及网桥控制器发送读取指令至装置控制器,以读取装置内存的存储数据。

在本发明的一实施例中,独立网桥测试方法还包括,网桥控制器根据测试数据与存储数据,执行数据比对以产生测试报告,并将测试报告及错误记录存储至存储装置的装置内存。

在本发明的一实施例中,独立网桥装置还包括网桥内存,网桥内存耦接至网桥控制器,并用以存储测试数据,测试数据为随机读写数据模板或连续读写数据模板。

在本发明的一实施例中,独立网桥装置耦接至主机装置的主机通信接口,在装置控制器根据握手测试信号,以产生确认测试信号,并将确认测试信号发送至网桥控制器的步骤后,还包括网桥控制器在预定时间内,判断是否与主机装置建立通信连接;以及若否,则允许网桥控制器对存储装置执行测试。

在本发明的一实施例中,独立网桥装置还包括耦接至网桥控制器的网桥通信接口,存储装置还包括耦接至装置控制器的装置通信接口,在网桥控制器根据确认测试信号,以产生测试数据,并发送写入指令至装置控制器,以将测试数据写入至装置内存的步骤中,还包括网桥控制器根据写入指令,将测试数据经由网桥通信接口与装置通信接口,写入至装置内存。

在本发明的一实施例中,在网桥控制器发送读取指令至装置控制器,以读取装置内存的存储数据的步骤中,还包括装置控制器根据读取指令,将存储数据经由装置通信接口与网桥通信接口发送至独立网桥装置。

本发明实施例所提供的独立网桥测试方法,借由网桥控制器直接与存储装置建立通信连接,自行产生测试数据,以对存储装置进行读写的测试,借此提供一种在不需要计算机主机的环境之下,而能直接对存储装置执行读写的测试。不仅大大地降低测试的成本以及节省测试的空间,更大幅度地减少往返通信的延迟时间,亦即减少测试的时间。

上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

图1是依照本发明实施例所绘示的独立网桥测试方法的系统架构示意图。

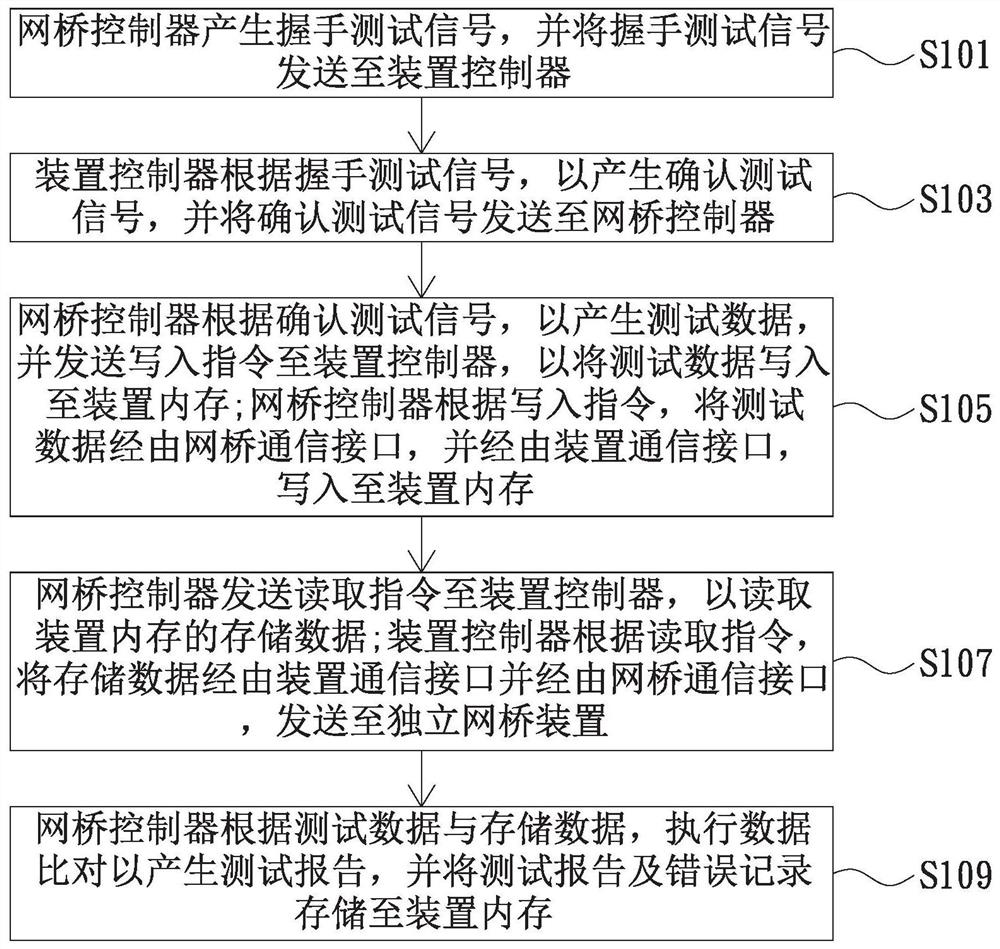

图2是依照本发明实施例所绘示的独立网桥测试方法的流程示意图。

图3是依照本发明另一实施例所绘示的独立网桥测试方法的系统架构示意图。

图4是依照本发明另一实施例所绘示的独立网桥测试方法的流程示意图。

具体实施方式

本发明实施例所提供的独立网桥测试方法,其可应用于诸如SSD或其他内部使用到非易失性内存的存储产品。非易失性内存例如可以是闪存(Flash)。

请参阅图1,图1是依照本发明实施例所绘示的独立网桥测试方法的系统架构示意图。独立网桥测试方法的系统架构1包括独立网桥装置10与存储装置20,并且独立网桥装置10耦接至存储装置20。独立网桥装置10包括网桥控制器110、网桥内存120与网桥通信接口130,其中网桥控制器110耦接至网桥内存120与网桥通信接口130。存储装置20包括装置控制器210、装置内存220与装置通信接口230,其中装置控制器210耦接至装置内存220与装置通信接口230。这里所提到的网桥控制器110可以是单芯片微控制器,例如8051。网桥内存120可以是挥发性内存,例如ROM。网桥通信接口130可以是SATA传输接口、PCIe总线接口或其它可传输数据的接口。另外,装置控制器210可以是单芯片微控制器,例如SSD控制器。装置内存220可以是非易失性内存,例如NAND Flash。装置通信接口230可以是SATA传输接口或PCIe总线接口等通信接口。

图2是依照本发明实施例所绘示的独立网桥测试方法的流程示意图。本发明实施例的独立网桥测试方法可以包括以下步骤。在步骤S101中,网桥控制器110产生握手(handshaking)测试信号,并将握手测试信号发送至装置控制器210,以提出与存储装置20建立通信连接的请求。

接着,在步骤S103中,装置控制器210根据接收的握手测试信号,以产生确认测试信号,并将确认测试信号发送至网桥控制器110,借此建立独立网桥装置10与存储装置20之间的通信连接。这里所提到的确认测试信号包括确认接受独立网桥装置10所请求的通信连接,提供装置内存220的规格数据例如是当前已安装的内存容量。

然后,在步骤S105中,网桥控制器110根据确认测试信号,以自行产生测试数据,并发送写入指令至装置控制器210,以将测试数据写入至装置内存220,借此进行读写测试的写入部分。这里所提到的测试数据可以是根据装置内存220的规格数据(例如内存容量),所产生的读写数据模板,例如随机读写数据模板或连续读写数据模板,而测试数据可以存储至网桥内存120。此外,在步骤S105中,还包括网桥控制器110根据写入指令,将测试数据经由网桥通信接口130,并经由装置通信接口230,然后写入至装置内存220。由于测试数据只需要经过两个通信接口而不需要经过三个通信接口(公知技术的系统架构)。借此,大幅度地减少往程通信的延迟时间,亦即减少测试的时间。

之后,在步骤S107中,网桥控制器110发送读取指令至装置控制器210,以读取装置内存220中的存储数据,借此进行读写测试的读取部分。这里所提到的存储数据乃是指在步骤S105中所写入的测试资料。此外,在步骤S107中,还包括装置控制器210根据接收到的读取指令,将装置内存220中的存储数据经由装置通信接口230,接着经由网桥通信接口130,然后发送至独立网桥装置10。由于测试数据只需要经过两个通信接口而不需要经过三个通信接口(公知技术的系统架构)。借此,大幅度地减少返程通信的延迟时间,亦即减少测试的时间。

接着,在步骤S109中,网桥控制器110根据测试数据与接收到的存储数据,执行数据比对以产生测试报告或去检查错误纪录,并将测试报告及错误记录存储至存储装置20的装置内存220或者存储装置20的其它内存中。借此提供一种在不需要计算机主机的环境之下,而直接对存储装置20执行读写的测试。不仅大大地降低测试的成本以及节省测试的空间,更大幅度地减少往返通信的延迟时间,亦即减少测试的时间。另外,对于完全没有瑕疵的装置内存220而言,存储数据应所述是完全等于在步骤S105中所写入的测试数据,或网桥控制器110的错误纪录没有任何错误。反之,对于有一些瑕疵的装置内存220而言,存储数据将不完全等于在步骤S105中所写入的测试数据,或网桥控制器110的错误纪录中有任何错误。此外,这里所提到的测试报告,将实际反应装置内存220的瑕疵程度。

图3是依照本发明另一实施例所绘示的独立网桥测试方法的系统架构示意图。需要说明的是,独立网桥测试方法的系统架构2为独立网桥测试方法的系统架构1所延伸的系统架构。有关系统架构及测试方法的相关说明已于前述实施例所详加叙述,在此不再赘述,仅作重点概述。独立网桥测试方法的系统架构2包括独立网桥装置10、存储装置20与主机装置30,并且独立网桥装置10耦接至存储装置20与主机装置30,其中主机装置30包括主机通信接口310,且主机通信接口310耦接于独立网桥装置10。这里所提到的主机装置30可以具有读写测试能力及通信连接能力的电子产品,例如计算机。

图4是依照本发明另一实施例所绘示的独立网桥测试方法的流程示意图。在步骤S103后,还包括步骤S201。在步骤S201中,网桥控制器110在预定时间内,判断是否与主机装置30建立通信连接。这里所提到的预定时间可以例如是30秒、60秒或90秒等短暂的时间。然后,在步骤S203中,若否(亦即未与主机装置30建立通信连接),则允许网桥控制器110对存储装置20执行读写测试。这里所提到的读写测试,乃是前述实施例所详加叙述的步骤S105至步骤S109,在此不再赘述。

综上所述,本发明实施例所提供的独立网桥测试方法,借由网桥控制器直接与存储装置建立通信连接,自行产生测试数据,以对存储装置进行读写的测试,借此提供一种在不需要计算机主机的环境之下,而能直接对存储装置执行读写的测试。不仅大大地降低测试的成本以及节省测试的空间,更大幅度地减少往程与返程通信的延迟时间,亦即减少测试的时间。

以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的方法及技术内容作出些许的更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

- 独立网桥测试方法

- 基于双AP独立网桥的物联网配网方法及系统