超低相位噪声时钟缓冲器

文献发布时间:2023-06-19 11:45:49

技术领域

本发明涉及集成电路技术领域,具体是涉及一种超低相位噪声时钟缓冲器。

背景技术

具有wifi和定位功能的设备中,需要用到高精度的同步时钟。高精度的晶振自身没有驱动能力,需要通过时钟缓冲器将时钟信号进行缓冲增加驱动能力。而时钟信号在缓冲过程中,会产生相位噪声,从而给设备提供的时钟精度出现偏差。目前的技术一般通过锁相环来构成,但是该方案实现的相位噪声在-60dBc/Hz左右,相位噪声降仍然较高。

发明内容

本发明要解决的技术问题是提供一种超低相位噪声时钟缓冲器,使其能够将相位噪声降低到-100dBc/Hz以下,甚至-120dBc/Hz以下。

为解决上述技术问题,本发明的超低相位噪声时钟缓冲器,包括耦合电容、第一倒相器、第一信号选择器、整形驱动电路和信号通道组;耦合电容用于对输入信号进行耦合;第一倒相器包括PMOS管和NMOS管,构成第一倒相器的PMOS管和NMOS管的沟道长度不低于特征尺寸的5倍;整形驱动电路用于对输入信号进行整形,并增强驱动能力;信号通道组包括若干组信号通道,信号通道用于产生经缓冲放大后的输出时钟信号。

耦合电容的第一端连接于时钟信号输入端,耦合电容的第二端分别连接于第一倒相器的输入端和第一信号选择器的输出端;第一倒相器的输出端分别连接于整形驱动电路的输入端和第一信号选择器的第一输入端,第一信号选择器的选择信号输入端输入使能信号,第一信号选择器的第二输入端输入第零参考信号;当电路处于正常工作状态,即使能信号有效时,通过第一信号选择器使第一倒相器的输入端和输出端相连;当电路处于关闭状态,第一倒相器的输入端输入第零参考信号,第零参考信号只能为高电平或者地;整形驱动电路的输出端连接于信号通道组的信号输入端,输出时钟信号从信号通道组的若干信号通道的输出端输出。

优选的,每组信号通道包括第四倒相器、第二信号选择器和缓冲器;第四倒相器的输入端连接于信号通道组的输入端,第四倒相器的输出端连接于第二信号选择器的第一输入端,第二信号选择器的输出端连接于缓冲器的输入端,第二信号选择器的选择信号输入端输入输出选择信号,第二信号选择器的第二输入端输入第一参考信号,输出时钟信号从缓冲器的输出端输出。

优选的,缓冲器包括至少一个缓冲单元,缓冲单元包括第一PMOS管、第二PMOS管、第三PMOS管、第一NMOS管、第二NMOS管、第三NMOS管、第一电阻和第二电阻;缓冲单元信号输入端分别连接于第一PMOS管的G极、第二PMOS管的G极、第一NMOS管的G极和第二NMOS管的G极;缓冲单元电压输入端分别连接于第一PMOS管的S极、第二PMOS管的S极和第三PMOS管的S极,第二高电平信号从缓冲单元电压输入端输入;第一PMOS管的D极连接于第一电阻的第一端;第一NMOS管的D极分别连接于第一电阻的第二端和第三NMOS管的G极,第一NMOS管的S极接地;第二PMOS管的D极分别连接于第三PMOS管的G极和第二电阻的第一端;第二NMOS管的D极连接于第二电阻的第二端,第二NMOS管的S极接地;第三NMOS管的S极接地;缓冲单元信号输出端分别连接于第三PMOS管的D极和第三NMOS管的D极。

优选的,第三PMOS管为推挽结构的PMOS驱动管,第三NMOS管为推挽结构的NMOS驱动管。

优选的,第二高电平信号的电压值等于整体供电电压的电压值。

优选的,整形驱动电路包括整形电路和驱动电路,整形电路的输入端连接于整形驱动电路的输入端,整形电路的输出端连接于驱动电路的输入端,驱动电路的输出端连接于整形驱动电路的输出端。

优选的,整形电路包括第二倒相器,第二倒相器的输入端连接于整形电路的输入端,第二倒相器的输出端连接于整形电路的输出端;第二倒相器包括PMOS管和NMOS管,构成第二倒相器的PMOS管的沟道长度和构成第一倒相器的PMOS管的沟道长度相同,构成第二倒相器的NMOS管的沟道长度和构成第一倒相器的NMOS管的沟道长度相同。

优选的,驱动电路由一个第三倒相器构成或者由至少两个第三倒相器串联构成。

优选的,第零参考信号为高电平信号或者低电平信号。

优选的,第一参考信号V1为高电平或者地,信号通道组2包括N组信号通道21,N为大于等于1的整数,每组信号通道21的第二信号选择器SS2的选择信号输入端输入的输出选择信号SEL彼此之间相同或不同。

本发明的有益效果在于:通过对整体的结构和缓冲器的单元结构进行设计,能够将相位噪声降低到-100dBc/Hz以下,甚至-120dBc/Hz以下。

附图说明

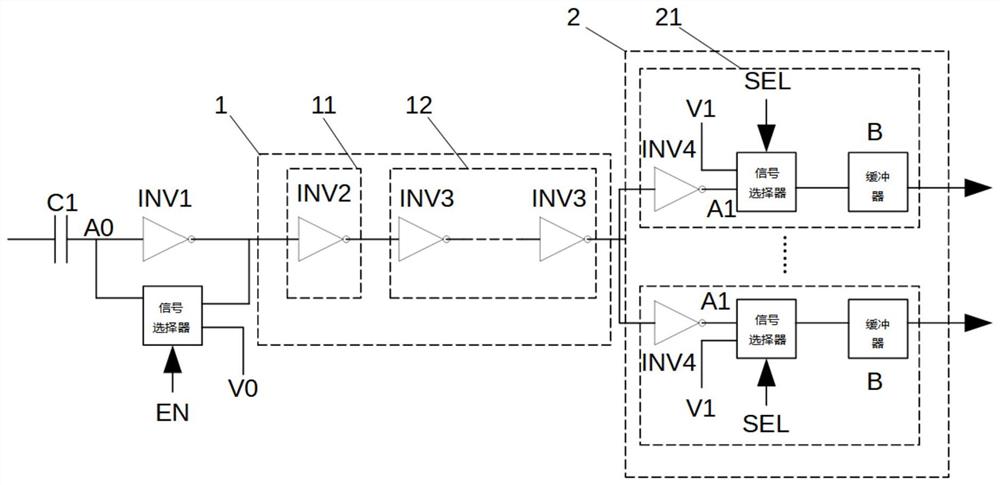

图1为本发明整体的电路结构图。

图2为本发明的缓冲单元的电路结构图。

图3为本发明在实验一中示波器输出的相位噪声的波形图。

图4为本发明在实验二中示波器输出的相位噪声的波形图。

图5为本发明在实验三中示波器输出的相位噪声的波形图。

图6为本发明在实验四中示波器输出的相位噪声的波形图。

具体实施方式

以下结合实施例和附图对本发明做进一步描述。

实施例:

如图1和图2所示,本发明的超低相位噪声时钟缓冲器,包括耦合电容C1、第一倒相器INV1、第一信号选择器SS1、整形驱动电路1和信号通道组2;耦合电容C1用于对输入信号进行耦合;第一倒相器INV1包括PMOS管和NMOS管,构成第一倒相器INV1的PMOS管和NMOS管的沟道长度不低于特征尺寸的5倍;整形驱动电路1用于对输入信号进行整形,并增强驱动能力;信号通道组2包括若干组信号通道21,信号通道21用于产生经缓冲放大后的输出时钟信号。

耦合电容C1的第一端连接于时钟信号输入端,耦合电容C1的第二端分别连接于第一倒相器INV1的输入端和第一信号选择器SS1的输出端;第一倒相器INV1的输出端分别连接于整形驱动电路1的输入端和第一信号选择器SS1的第一输入端,第一信号选择器SS1的选择信号输入端输入使能信号EN,第一信号选择器SS1的第二输入端输入第零参考信号V0;整形驱动电路1的输出端连接于信号通道组2的信号输入端,输出时钟信号从信号通道组2的若干信号通道21的输出端输出。

具体的,每组信号通道21包括第四倒相器INV4、第二信号选择器SS2和缓冲器B;第四倒相器INV4的输入端连接于信号通道组2的输入端,第四倒相器INV4的输出端连接于第二信号选择器SS2的第一输入端,第二信号选择器SS2的输出端连接于缓冲器B的输入端,第二信号选择器SS2的选择信号输入端输入输出选择信号SEL,第二信号选择器SS2的第二输入端输入第一参考信号V1,输出时钟信号从缓冲器B的输出端输出。

具体的,缓冲器B包括至少一个缓冲单元,缓冲单元包括第一PMOS管P1、第二PMOS管P2、第三PMOS管P3、第一NMOS管N1、第二NMOS管N2、第三NMOS管N3、第一电阻R1和第二电阻R2;缓冲单元信号输入端分别连接于第一PMOS管P1的G极、第二PMOS管P2的G极、第一NMOS管N1的G极和第二NMOS管N2的G极;缓冲单元电压输入端分别连接于第一PMOS管P1的S极、第二PMOS管P2的S极和第三PMOS管P3的S极,第二高电平信号VH2从缓冲单元电压输入端输入;第一PMOS管P1的D极连接于第一电阻R1的第一端;第一NMOS管N1的D极分别连接于第一电阻R1的第二端和第三NMOS管N3的G极,第一NMOS管N1的S极接地;第二PMOS管P2的D极分别连接于第三PMOS管P3的G极和第二电阻R2的第一端;第二NMOS管N2的D极连接于第二电阻R2的第二端,第二NMOS管N2的S极接地;第三NMOS管N3的S极接地;缓冲单元信号输出端分别连接于第三PMOS管P3的D极和第三NMOS管N3的D极。

具体的,第三PMOS管P3为推挽结构的PMOS驱动管,第三NMOS管N3为推挽结构的NMOS驱动管。

具体的,第二高电平信号VH2的电压值等于整体供电电压的电压值。

具体的,整形驱动电路1包括整形电路11和驱动电路12,整形电路11的输入端连接于整形驱动电路1的输入端,整形电路11的输出端连接于驱动电路12的输入端,驱动电路12的输出端连接于整形驱动电路1的输出端。

具体的,整形电路11包括第二倒相器INV2,第二倒相器INV2的输入端连接于整形电路11的输入端,第二倒相器INV2的输出端连接于整形电路11的输出端;第二倒相器INV2包括PMOS管和NMOS管,构成第二倒相器INV2的PMOS管的沟道长度和构成第一倒相器INV1的PMOS管的沟道长度相同,构成第二倒相器INV2的NMOS管的沟道长度和构成第一倒相器INV1的NMOS管的沟道长度相同。

具体的,驱动电路12由一个第三倒相器INV3构成或者由至少两个第三倒相器INV3串联构成。

具体的,第零参考信号V0为高电平信号或者低电平信号。

具体的,第一参考信号V1为高电平或者地,信号通道组2包括N组信号通道21,N为大于等于1的整数,每组信号通道21的第二信号选择器SS2的选择信号输入端输入的输出选择信号SEL彼此之间相同或不同,即能够根据需求选择信号通道21全部工作或者部分工作。

本发明的原理:时钟信号输入端的输入信号为外部时钟信号或者晶振信号,耦合电容C1对输入信号进行耦合到点A0。

在本实施例中,使能信号EN和输出选择信号SEL为选择信号,第零参考信号V0和第一参考信号V1为参考信号,第一信号选择器SS1和第二信号选择器SS2为信号选择器。当电路工作时,通过信号选择器选择通路上的信号;当不工作时,通过信号选择器选择参考信号。

当电路处于工作状态,即使能信号EN有效时,第一信号选择器SS1将第一倒相器INV1的输入端和输出端短接。要求第一倒相器INV1在输入输出短路状态时,确保其输入输出的电压值约为1/2的整体供电电压的电压值,其作用是产生电压值为1/2的整体供电电压的电压值的偏置电压;当电路处于关闭状态,即使能信号EN无效时,第一信号选择器SS1将第一倒相器INV1的输入端输入第零参考信号V0,第零参考信号V0只能为高电平或者地。

整形驱动电路1包括整形电路11和驱动电路12,整形电路11的作用主要是对输入信号进行整形,从而产生方波或者接近于方波的输出信号,驱动电路12的作用主要是增强驱动能力。

信号整形电路1输出的信号根据要求,送到信号通道组2的信号通道21中。信号整形电路1输出的信号经过第四倒相器INV4后,产生第一输出信号A1。当输出选择信号SEL有效时,第一输出信号A1通过第二信号选择器SS2送到缓冲器B的输入端,经过缓冲放大后,产生输出时钟信号。

根据本实施例进行制作并进行相关实验,实验一和实验二的实验设备相同,实验三和实验四的实验设备相同。

如图3所示,图3为实验一中示波器输出的相位噪声的波形图。输入信号的频率为26MHz。1KHz的相位噪声为-141.63dBc/Hz,10KHz的相位噪声为-150.25dBc/Hz,100KHz的相位噪声为-152.41dBc/Hz,1MHz的相位噪声为-159.53dBc/Hz。上述四个采样点的相位噪声均在-120dBc/Hz以下。相位噪声是从能量角度来说的,指单位带宽内的功率与总信号功率的比,单位是dBc/Hz。单位带宽,是指偏离理想频点的单位带宽。

如图4所示,图4为实验二中示波器输出的相位噪声的波形图。输入信号的频率为52MHz。1KHz的相位噪声为-135.29dBc/Hz,10KHz的相位噪声为-146.37dBc/Hz,100KHz的相位噪声为-150.12dBc/Hz,1MHz的相位噪声为-156.92dBc/Hz。上述四个采样点的相位噪声均在-120dBc/Hz以下。

如图5所示,图5为实验三中示波器输出的相位噪声的波形图。输入信号的频率为26MHz。100Hz的相位噪声为-130.27dBc/Hz,1KHZ的相位噪声为-138.55dBc/Hz,10KHZ的相位噪声为-140.47dBc/Hz,100KHZ的相位噪声为-140.99dBc/Hz。上述四个采样点的相位噪声均在-120dBc/Hz以下。

如图6所示,图6为实验四中示波器输出的相位噪声的波形图。输入信号的频率为52MHz。100Hz的相位噪声为-129.08dBc/Hz,1KHZ的相位噪声为-136.65dBc/Hz,10KHZ的相位噪声为-137.35dBc/Hz,100KHZ的相位噪声为-137.3dBc/Hz。上述四个采样点的相位噪声均在-120dBc/Hz以下。

在多种实验设备上进行大量实验后,本发明保守来说,能够将相位噪声降低到-100dBc/Hz以下,更普遍的是,能够将相位噪声降低到-120dBc/Hz以下。

- 超低相位噪声时钟缓冲器

- 用于超低相位噪声振荡器的幅度噪声降低系统和方法