一种基于纠错的高速数据存取方法及装置

文献发布时间:2023-06-19 11:45:49

技术领域

本发明涉及数据存储技术领域,具体涉及一种基于纠错的高速数据存取方法及装置。

背景技术

随着固态存储技术的发展,各种高速固态闪存应用在各种仪器设备中作为数据的存储介质,由于固态存储器件多为NAND FLASH,由于生产工艺等问题导致其在生产及使用过程中无法避免的出现部分存储单元无法正常使用的情况即出现坏块。固态存储出厂后产生的坏块一般可以通过初始化扫描,存储空间映射等方式将无法使用的部分剔除出去,但使用过程中出现的坏块则需要通过ECC校验等方式对内存进行错误检查,并将检查出的坏块列入存储空间映射管理中,并对存储空间进行重新映射,这部分工作一般由文件系统进行管理。在一些嵌入式高速应用场景中,由于超高的数据吞吐量(GByte/s),一般文件系统已经无法使用。

现有数据存取一般分为有文件系统和无文件系统两种:

1、有文件系统的方法一般使用带操作系统(linux系统)的嵌入式核心处理器对外围固态存储器件进行管理,这种方法具有操作方便,可靠性高的优点,但由于并行处理能力等限制,无法支持超高速读写带宽要求的使用场景。

2、无文件系统的方法可以采用以FPGA为核心处理单元的方案,直接驱动外挂存储器件,这种方法具有高并发处理能力,具有超高速读写带宽的优势,但对于存储的坏块问题需要通过比较复杂的初始化,动态坏块检查,存储空间映射等方案来处理,并且管理复杂程度随挂载存储单元个数的增加而增加。

发明内容

针对上述现有技术存在的问题,本发明提供了一种基于纠错的高速数据存取方法及装置,能够在保证数据吞吐量满足超高速读写带宽要求的同时确保数据可靠性,该技术方案如下:

第一方面,提供了一种基于纠错的高速数据存取方法,应用于对flash固态存储器件的读写控制,包括:

写数据时:所有原始数据根据一个存储单元大小进行分组,获取第一预设数量组原始数据作为一段,对于一段原始数据,从每一组抽取一位(bit)形成一组待编码数据,基于一组待编码数据生成一组纠错编码数据,直至每一组原始数据的所有位均进行纠错编码过程;

将一组待编码数据和对应的一组纠错编码数据逐位写入第三数量的逻辑单元(LUN)中,每个逻辑单元写入一位数据;

读数据时,从每个逻辑单元中读取数据,并经过解码纠错获取原始数据。

在一种可能的实现方式中,所述对读取的数据进行错误检测并纠错之后,还包括:

对于逻辑单元中出现错误数据位的存储单元,增加一次异常存储记录;

监控同一个存储单元异常存储记录次数是否大于预设阈值;

若是,对数据存储空间的物理地址和逻辑地址的映射表生成更新请求;

在空闲状态下基于所述更新请求进行映射表更新。

在一种可能的实现方式中,一个所述逻辑单元(LUN)对应一个片选使能信号输入端实现对每个逻辑单元读写过程的单独控制。

在一种可能的实现方式中,在所述将一组待编码数据和对应的一组纠错编码数据逐位写入第三数量的逻辑单元(LUN)以及读取数据时,通过控制所述第三数量的逻辑单元(LUN)的同时启用以提高数据读写速度。

在一种可能的实现方式中,所述纠错编码过程采用汉明码编码算法。

在一种可能的实现方式中,所述逻辑单元位于flash固态存储器件的FLASH颗粒中,所述flash固态存储器件包括8个FLASH颗粒,一个FLASH颗粒包括4个逻辑单元。

第二方面,提供了一种基于纠错的高速数据存取装置,包括:

原始数据单元纠错编码单元,用于将所有原始数据根据一个存储单元大小进行分组,获取第一预设数量组原始数据作为一段,对于一段原始数据,从每一组抽取一位(bit)形成一组待编码数据,基于一组待编码数据生成一组纠错编码数据,直至每一组原始数据的所有位均进行纠错编码过程;

原始数据及编码数据写入单元,将一组待编码数据和对应的一组纠错编码数据逐位写入第三数量的逻辑单元(LUN)中,每个逻辑单元写入一位数据;

读取数据单元,用于从每个逻辑单元中读取数据,并经过解码纠错获取原始数据。

在一种可能的实现方式中,上述基于纠错的高速数据存取装置还包括:异常存储单元管理单元,用于对于逻辑单元中出现错误数据位的存储单元,增加一次异常存储记录;当同一个存储单元异常存储记录次数大于预设阈值时,对数据存储空间的物理地址和逻辑地址的映射表生成更新请求,并在空闲状态下基于所述更新请求进行映射表更新。

第三方面,提供了上述高速数据存取方法在基于FPGA的高速相机中的应用,所述FPGA通过控制多个FLASH颗粒组成的固态存储阵列实现高速图像数据的读写。

本发明的一种基于纠错的高速数据存取方法及装置,具备如下有益效果:本发明通过多个存储单元的组合设置、在原始数据进行纠错编码时对参与一次编码过程的原始数据位的选择方法设置、对生成的纠错编码写入存储单元的方法设置,实现了在确保数据吞吐量的同时利用存储阵列编码对单个存储单元出现的异常错误进行纠正,避免因单个存储单元异常导致的数据错误,提高系统可靠性。

附图说明

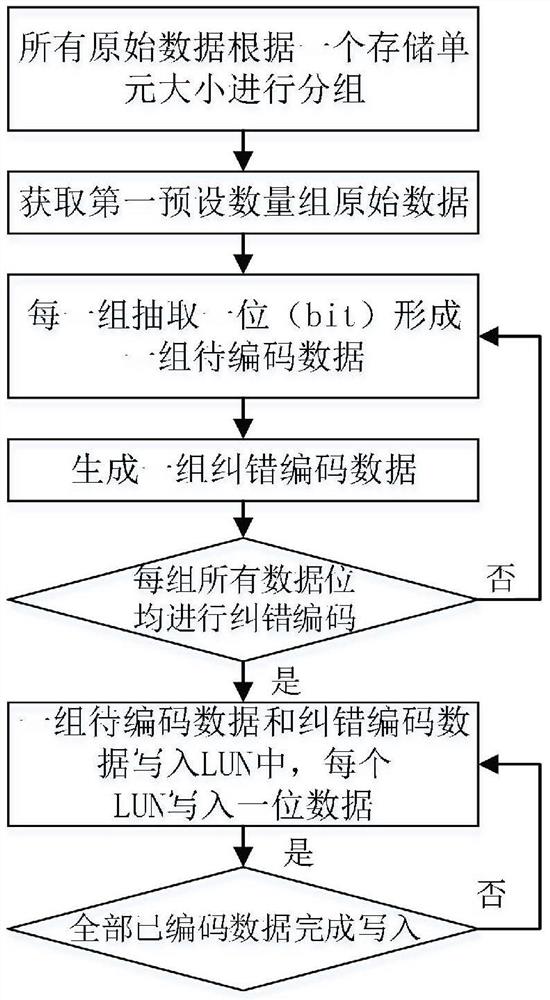

图1是本发明实施例对于一段原始数据的纠错编码及写入过程流程图;

图2是本发明实施例中读取数据的流程图;

图3是本发明中对于一组待编码数据的写入过程示意图;

图4是本发明中高速相机中FPGA对flash固态存储器件的读写控制示意图;

图5是本发明中基于纠错的高速数据存取装置的结构框图。

具体实施方式

为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作进一步地详细描述,所描述的实施例不应视为对本发明的限制,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

本发明实施例公开了一种基于纠错的高速数据存取方法,应用于基于FPGA的高速相机中FPGA对flash固态存储器件的读写控制,FPGA通过控制多个FLASH颗粒组成的固态存储阵列实现高速图像数据的读写,具体的,高速图像数据的存取过程包括:每个高速图像数据由高速图像采集传感器采集并传输给FPGA,FPGA控制了8个FLASH颗粒组成的固态存储阵列。高速图像传感器将采集的图像数据传输给FPGA,接收到原始图像数据后FPGA对该数据进行编码。编码后数据被写入到固态存储阵列中。数据采集完成后根据上位机给定的数据读取空间,读出图像数据,读出的图像数据经过解码后输出原始图像数据给上位机。其中FPGA对8个FLASH颗粒组成的固态存储阵列的控制方法,

写数据时:

将所有原始数据根据一个存储单元大小进行分组,获取第一预设数量组原始数据作为一段;

对于一段原始数据的编码和写入过程包括:

(1)从每一组抽取一位(bit)形成一组待编码数据,基于一组待编码数据进行一次纠错编码过程生成一组纠错编码数据;

(2)重复步骤(1),直至每一组原始数据的所有位均进行纠错编码过程;

(3)将一组待编码数据和对应的一组纠错编码数据逐位写入第三数量的逻辑单元(LUN)中,每个逻辑单元写入一位数据,即每个逻辑单元中启用一个存储单元存储一位数据;

(4)重复步骤(3),直至一段原始数据和对应的纠错编码数据完成写入过程。

读数据时,从每个逻辑单元中读取数据,并经过解码纠错获取原始数据。

在上述写入过程中,在第一预设数量组原始数据中的每一组抽取一位(bit)形成一组待编码数据,即一组待编码数据的位数为第一预设数量,基于第一预设数量位待编码数据和预设纠错编码算法,可确定得到的一组纠错编码数据的位数,记一组纠错编码数据的位数为第二数量;

本实施例以第一预设数量为11,所有逻辑单元的一个存储单位存储8bit数据为例,则一组原始数据的大小为8bit,一段原始数据的大小为11*8bit,即11个字节,对于该11个字节的纠错编码以及写入过程为:

对每组原始数据进行编号第1组,第2组,...第11组,对每一组数据的每一位进行编号第1位,第2位,...第8位;

从第1组到第11组原始数据中每一组抽取第1位形成第1组待编码数据,以汉明码编码算法为例,对第1组待编码数据进行编码生成5位纠错编码数据;

从第1组到第11组原始数据中每一组抽取第2位形成第2组待编码数据,形成对应的5位纠错编码数据;

类似的,从第1组到第11组原始数据中每一组抽取第j位第j组待编码数据(j小于等于8),形成对应的5位纠错编码数据;

将第1组待编码数据的11位和对应的5位纠错编码数据,共计16位数据写入到16个逻辑单元中,对逻辑单元中的每位存储空间按位进行编号,第1位,第2位,...第8位,该16位数据依次写入每个逻辑单元的第1位;

将第2组待编码数据的11位和对应的5位纠错编码数据,依次写入每个逻辑单元的第2位;

类似的,将第j组待编码数据的11位和对应的5位纠错编码数据,依次写入每个逻辑单元的第j位。

对应的,在读取数据时解码纠错的过程可以为:

将第1到第16个逻辑单元的第j位数据一一读出,并对读出数据进行解码纠错,获得原始数据。

本发明实施例中,通过第一预设数量的数值设置和纠错编码方案的选择设置,得到第二数量的数值,进一步得到对于一段原始数据和该段原始数据对应的纠错编码数据的存储过程需要的逻辑单元个数即第三数量,例如上述对一段原始数据的存取需要16个逻辑单元,在本实施例中,为了能够灵活采用多种纠错编码算法,以适应不同的第三数量的需求,将flash固态存储器件设置为包括8个FLASH颗粒,一个FLASH颗粒包括4个逻辑单元。

本发明实施例通过多个存储单元的组合设置、在原始数据进行纠错编码时对参与一次编码过程的原始数据位的选择方法设置、对生成的纠错编码写入存储单元的方法设置:

第一方面,实现了可对读出数据进行纠错处理,避免因单个单元的损坏造成的数据错误,通过对原始数据编码消除某一个存储单元失效对整个系统带来的影响。

第二方面,本实施例中通过一个所述逻辑单元(LUN)对应一个片选使能信号输入端实现对每个逻辑单元读写过程的单独控制,在将一组待编码数据和对应的一组纠错编码数据逐位写入第三数量的逻辑单元(LUN)以及读取数据时,通过控制第三数量的逻辑单元(LUN)的同时启用以提高数据读写速度,即通过并行控制存储单元阵列提高数据处理带宽。在保证高速存取的同时提高了固态存储器件存储数据的准确性,在少量存储单元因寿命问题失效时可以保证读出数据的正确性,延长了存储系统的使用时间。

第三方面,相对于现有技术中采用设置RAID冗余磁盘阵列提高数据可靠性的设计,本发明实施实例通过增加可同时操作的物理存储单元,细化单位存储单元大小,简化了控制操作方法,和存储数据块之间的关联性,提高了实时处理能力。

在上述确保数据吞吐量以及数据可靠性的基础上,本实施例对读取的数据进行错误检测并纠错之后,还包括对整个flash固态存储器件中正常和异常存储单元的管理,具体包括:

对于逻辑单元中出现错误数据位的存储单元,增加一次异常存储记录;

监控同一个存储单元异常存储记录次数是否大于预设阈值;

若是,对数据存储空间的物理地址和逻辑地址的映射表生成更新请求;

在空闲状态下基于所述更新请求进行映射表更新。

以便于下次启用flash存储器件时,根据映射表的逻辑地址和物理地址在正常存储单元上进行数据存取,本发明实施例中,每次读出数据的解码过程中会对异常存储单元的位置信息进行统计,基于多次在flash固态存储器件上的读写操作以及多次的异常存储单元位置信息统计结果,当同一个存储单元异常存储记录次数大于预设阈值,判定该位置的存储单元为异常物理存储单元,并动态更新物理地址和逻辑地址的映射表,将异常物理存储单元从映射表中剔除出去。

本发明实施例还提供了一种基于纠错的高速数据存取装置,包括:

原始数据单元纠错编码单元,用于将所有原始数据根据一个存储单元大小进行分组,获取第一预设数量组原始数据作为一段,对于一段原始数据,从每一组抽取一位(bit)形成一组待编码数据,基于一组待编码数据生成一组纠错编码数据,直至每一组原始数据的所有位均进行纠错编码过程;

原始数据及编码数据写入单元,将一组待编码数据和对应的一组纠错编码数据逐位写入第三数量的逻辑单元(LUN)中,每个逻辑单元写入一位数据;

读取数据单元,用于从每个逻辑单元中读取数据,并经过解码纠错获取原始数据;

异常存储单元管理单元,用于对于逻辑单元中出现错误数据位的存储单元,增加一次异常存储记录;当同一个存储单元异常存储记录次数大于预设阈值时,对数据存储空间的物理地址和逻辑地址的映射表生成更新请求,并在空闲状态下基于所述更新请求进行映射表更新。

本实施例中关于一种基于纠错的高速数据存取装置的具体限定可以参见上文中对于一种基于纠错的高速数据存取方法的限定,在此不再赘述。上述各单元可以软件形式实现,并基于FPGA调用执行以上各个单元对应的操作。

本发明不局限于上述具体的实施方式,本领域的普通技术人员从上述构思出发,不经过创造性的劳动,所做出的种种变换,均落在本发明的保护范围之内。

- 一种基于纠错的高速数据存取方法及装置

- 一种基于BLVDS总线的列车机箱高速数据记录装置及方法