氮化镓功率器件栅驱动电路

文献发布时间:2023-06-19 11:49:09

技术领域

本申请实施例涉及高压功率集成电路技术领域,特别涉及一种氮化镓功率器件栅驱动电路。

背景技术

Buck(降压)型DC(Direct Current,直流)-DC变换器中,通常使用两个串联连接的功率器件连接在输入高压与地之间。由于N型功率器件相对于P型功率器件来说,具有更低的导通电阻和更小的寄生电容,在300V以上乃至于600V的高压应用中,通常采用两个N型的功率器件,如图1所示,M

如图2所示的电平移位电路,其包括NLDMOS(N Laterally Diffused Metal OxideSemiconductor,N型横向扩散金属氧化物半导体) N

为解决上述问题,可以设计出一种用双路LDMOS的电平移位电路,如图3所示,其包括脉冲产生电路、两路电平移位电路、RS触发器和缓冲级。其中电平移位电路由LDMOS N

面对当下第三代功率半导体的兴起,氮化镓功率器件等对于浮栅驱动芯片的传输速度和抗干扰能力提出了更高的要求,因此,希望得到一种抗干扰能力强且传输速度快的高压电平移位电路。如图6所示,现有技术中提出了一种采用数字共模保护电路的电平移位电路,其包括脉冲产生电路,双路电平移位电路、保护电路、RS触发器以及缓冲级,其中,电平移位电路由LDMOS N

发明内容

本申请实施例提供了一种氮化镓功率器件栅驱动电路,用于解决采用数字共模保护电路的电平移位电路不具有较好的抗干扰能力的问题。所述技术方案如下:

一方面,提供了一种氮化镓功率器件栅驱动电路,所述氮化镓功率器件栅驱动电路包括:窄脉冲产生电路、高压电平移位电路、动态非对称状态产生电路、共模屏蔽逻辑、RS触发器和缓冲级;

所述窄脉冲产生电路的输入端作为所述氮化镓功率器件栅驱动电路的输入端,所述窄脉冲产生电路的第一输出端与所述高压电平移位电路的第一输入端相连,所述窄脉冲产生电路的第二输出端与所述高压电平移位电路的第二输入端相连,所述窄脉冲产生电路的电源端与低压侧电源相连,所述窄脉冲产生电路的逻辑地端与芯片地相连;所述高压电平移位电路的第一输出端分别与所述动态非对称状态产生电路的第一输出端以及所述共模屏蔽逻辑的第一输入端相连,所述高压电平移位电路的第二输出端分别与所述动态非对称状态产生电路的第二输出端以及所述共模屏蔽逻辑的第二输入端相连;所述共模屏蔽逻辑的第一输出端与所述RS触发器的复位输入端相连,所述共模屏蔽逻辑的第二输出端与所述RS触发器的置位输入端相连;所述RS触发器的同相输出端分别与所述缓冲级的输入端和所述动态非对称状态产生电路的第一输入端相连;所述RS触发器的反相输出端与所述动态非对称状态产生电路的第二输入端相连;所述缓冲级的输出端作为所述氮化镓功率器件栅驱动电路的输出端;所述共模屏蔽逻辑、所述RS触发器和所述缓冲级的电源端分别与高压侧电源相连,所述共模屏蔽逻辑、所述RS触发器和所述缓冲级的逻辑地分别与高压区浮动地相连;

所述高压电平移位电路中还包括锁存器,所述动态非对称状态产生电路用于动态改变所述锁存器在电源电压瞬变时的平衡点,所述锁存器在所述平衡点改变时偏移向上一稳定状态,以控制所述氮化镓功率器件栅驱动电路的输出信号保持不变。

在一种可能的实现方式中,所述高压电平移位电路包括:第一开关、第二开关、第一二极管、第二二极管和锁存器,所述锁存器包括第一PMOS管和第二PMOS管;

所述第一开关的栅极作为所述高压电平移位电路的第一输入端,所述第二开关的栅极作为所述高压电平移位电路的第二输入端;所述第一开关和所述第二开关的源极和衬底均接地;所述第一开关的漏极、所述第二二极管的负极、所述第一PMOS管的漏极和所述第二PMOS管的栅极互连后作为所述高压电平移位电路的第一输出端;所述第二开关的漏极、所述第一二极管的负极、所述第二PMOS管的漏极和所述第一PMOS管的栅极互连后作为所述高压电平移位电路的第二输出端;所述第一PMOS管和所述第二PMOS管的源极分别与所述高压侧电源相连;所述第一二极管和所述第二二极管的正极分别与所述高压区浮动地相连。

在一种可能的实现方式中,所述动态非对称状态产生电路包括:第一NMOS管和第二NMOS管;

所述第一NMOS管的源极和所述第二NMOS管的源极互连后与所述高压区浮动地相连;所述第一NMOS管的漏极作为所述动态非对称状态产生电路的第一输出端;所述第二NMOS管的漏极作为所述动态非对称状态产生电路的第二输出端;所述第一NMOS管的栅极作为所述动态非对称状态产生电路的第一输入端;所述第二NMOS管的栅极作为所述动态非对称状态产生电路的第二输入端。

在一种可能的实现方式中,所述共模屏蔽逻辑包括:第一反相器、第二反相器、第一与非门、第二与非门和第三与非门;

所述第一反相器的输入端作为所述共模屏蔽逻辑的第二输入端,所述第二反相器的输入端作为所述共模屏蔽逻辑的第一输入端;所述第一反相器的输出端分别与所述第一与非门的第一输入端和所述第二与非门的第一输入端相连;所述第二反相器的输出端分别与所述第一与非门的第二输入端和所述第三与非门的第一输入端相连;所述第一与非门的输出端分别与所述第二与非门的第二输入端和所述第三与非门的第二输入端相连;所述第二与非门的输出端作为所述共模屏蔽逻辑的第一输出端,所述第三与非门的输出端作为所述共模屏蔽逻辑的第二输出端。

在一种可能的实现方式中,所述RS触发器包括:第四与非门和第五与非门;

所述第四与非门的第一输入端作为所述RS触发器的复位输入端,所述第五与非门的第一输入端作为所述RS触发器的置位输入端;所述第四与非门的第二输入端与所述第五与非门的输出端互连后作为所述RS触发器的同相输出端;所述第五与非门的第二输入端与所述第四与非门的输出端互连后作为所述RS触发器的反相输出端。

在一种可能的实现方式中,所述氮化镓功率器件栅驱动电路还包括前置放大器;

所述高压电平移位电路的第一输出端分别与所述动态非对称状态产生电路的第一输出端以及所述前置放大器的第一输入端相连,所述高压电平移位电路的第二输出端分别与所述动态非对称状态产生电路的第二输出端以及所述前置放大器的第二输入端相连;所述前置放大器的第一输出端与所述共模屏蔽逻辑的第一输入端相连;所述前置放大器的第二输出端与所述共模屏蔽逻辑的第二输入端相连。

在一种可能的实现方式中,所述前置放大器包括:第一P型开关、第二P型开关、第一电阻和第二电阻;

所述第一P型开关的栅极作为所述前置放大器的第一输入端,所述第二P型开关的栅极作为所述前置放大器的第二输入端;所述第一P型开关的漏极、所述第一电阻的第一端互连后作为所述前置放大器的第一输出端;所述第二P型开关的漏极、所述第二电阻的第一端互连后作为所述前置放大器的第二输出端;所述第一电阻的第二端和所述第二电阻的第二端互连后与所述高压区浮动地相连;所述第一P型开关的源极和所述第二P型开关的源极互连后与所述高压侧电源相连。

在一种可能的实现方式中,所述动态非对称状态产生电路包括:第三NMOS管、第四NMOS管、第三电阻和第四电阻;

所述第三NMOS管的源极和所述第四NMOS管的源极互连后与所述高压区浮动地相连;所述第三电阻的第一端与所述第三NMOS管的漏极相连,所述第三电阻的第二端作为所述动态非对称状态产生电路的第一输出端;所述第四电阻的第一端与所述第四NMOS管的漏极相连,所述第四电阻的第二端作为所述动态非对称状态产生电路的第二输出端;所述第三NMOS管的栅极作为所述动态非对称状态产生电路的第一输入端;所述第四NMOS管的栅极作为所述动态非对称状态产生电路的第二输入端。

在一种可能的实现方式中,所述共模屏蔽逻辑包括:第六与非门、第七与非门和第八与非门;

所述第六与非门的第一输入端与所述第七与非门的第一输入端互连后作为所述共模屏蔽逻辑的第二输入端;所述第六与非门的第二输入端与所述第八与非门的第一输入端互连后作为所述共模屏蔽逻辑的第一输入端;所述第六与非门的输出端分别与所述第七与非门的第二输入端和所述第八与非门的第二输入端相连;所述第七与非门的输出端作为所述共模屏蔽逻辑的第一输出端,所述第八与非门的输出端作为所述共模屏蔽逻辑的第二输出端。

在一种可能的实现方式中,所述第一NMOS管和所述第二NMOS管的电流能力低于所述锁存器中的所述第一PMOS管和所述第二PMOS管的电流能力。

本申请实施例提供的技术方案的有益效果至少包括:

1、降低传输延时的同时提高芯片的抗噪声干扰能力,不仅适用于传统的高压浮栅驱动芯片,还适用于第三代半导体功率器件的驱动芯片。

2、静态功耗小,除了开关过程,该结构基本没有静态功耗。

3、提升了浮动地负压工作能力。

4、结构简单,避免带来额外的成本。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1为采用高压浮栅驱动芯片的DC-DC电源拓扑结构;

图2为现有技术中采用单路LDMOS的高压电平移位电路的示意图;

图3为现有技术中采用双路LDMOS的高压电平移位电路的示意图;

图4为dV/dt瞬变噪声对采用双路LDMOS的高压电平移位电路的影响波形;

图5为采用双路LDMOS的高压电平移位电路中增加噪声滤除电路的示意图;

图6为现有技术中采用数字共模保护电路的电平移位电路的示意图;

图7为采用数字共模保护电路的电平移位电路中,负载不匹配时dV/dt瞬变噪声对其的响应波形图;

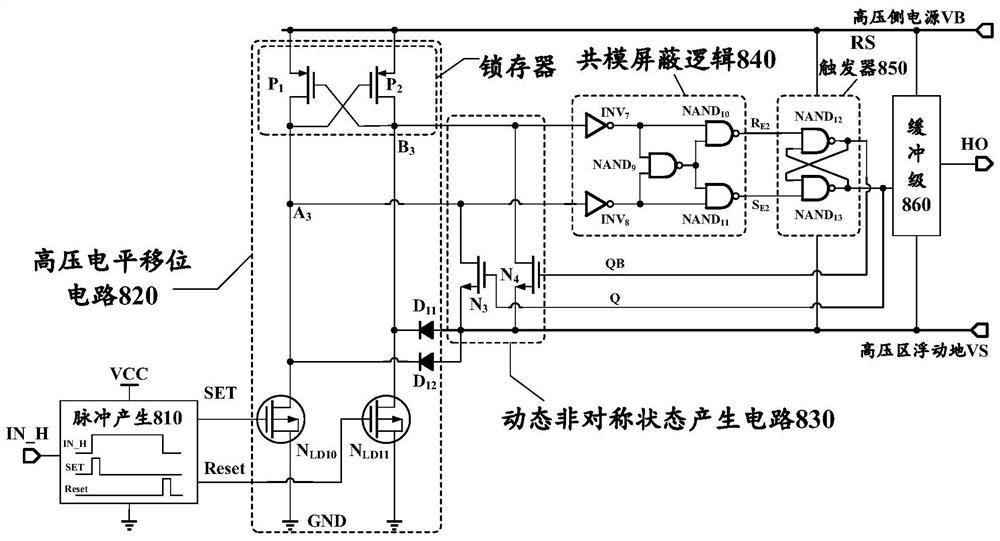

图8为本申请提出的第一种氮化镓功率器件栅驱动电路的示意图;

图9为第一种氮化镓功率器件栅驱动电路的基本工作模型的示意图;

图10为本申请提出电路中的锁存器的工作模型图;

图11为本申请提出的氮化镓功率器件栅驱动电路输出为低电平时,受dV/dt瞬变噪声的影响波形的示意图;

图12为本申请提出的氮化镓功率器件栅驱动电路输出为高电平时,受dV/dt瞬变噪声的影响波形的示意图;

图13为本申请提出的第二种氮化镓功率器件栅驱动电路的示意图。

具体实施方式

为使本申请实施例的目的、技术方案和优点更加清楚,下面将结合附图对本申请实施方式作进一步地详细描述。

请参考图8,其示出了本申请一个实施例提供的氮化镓功率器件栅驱动电路的结构流程图。该氮化镓功率器件栅驱动电路,可以包括:窄脉冲产生电路810、高压电平移位电路820、动态非对称状态产生电路830、共模屏蔽逻辑840、RS触发器850和缓冲级860。

如图8所示,窄脉冲产生电路810的输入端作为氮化镓功率器件栅驱动电路的输入端IN_H,窄脉冲产生电路810的第一输出端SET与高压电平移位电路820的第一输入端相连,窄脉冲产生电路810的第二输出端RESET与高压电平移位电路820的第二输入端相连,窄脉冲产生电路810的电源端与低压侧电源VCC相连,窄脉冲产生电路810的逻辑地端与芯片地相连;高压电平移位电路820的第一输出端A

下面分别对高压电平移位电路820、动态非对称状态产生电路830、共模屏蔽逻辑840和RS触发器850的电路结构进行介绍。

1)高压电平移位电路820;

高压电平移位电路820可以包括:第一开关N

需要说明的第一点是,第一开关和第二开关除了可以是NLDMOS器件,也可以是LDMOS器件,还可以是其他功率器件,如IGBT、JFET等。

需要说明的第二点是,第一二极管和第二二极管除了可以是二极管,也可以是三极管的基极-发射极二极管或MOS管的体二极管,其作用是钳位A

需要说明的第三点是,第一PMOS管P

2)动态非对称状态产生电路830;

动态非对称状态产生电路830可以包括:第一NMOS管N

需要说明的是,锁存器可以PMOS管构成的锁存器,也可以是其他用到负栅-源电压或负基极-发射极电压开通器件的锁存器,只要保证第一NMOS管N

3)共模屏蔽逻辑840;

共模屏蔽逻辑840可以包括:第一反相器INV

4)RS触发器850;

RS触发器850可以包括:第四与非门NAND

下面对图8所示的氮化镓功率器件栅驱动电路的工作流程进行介绍。请参考图9,输入信号IN_H为一个较宽的脉冲信号,为了降低高压开关器件的导通损耗以及可靠性要求,先通过窄脉冲产生电路810将IN_H的上升沿和下降沿分别转化为SET和RESET这两个窄脉冲信号,利用SET驱动N

当dV/dt瞬态噪声信号施加至VS和VB时,A

图11示出了氮化镓功率器件栅驱动电路输出为低电平时,受dV/dt瞬变噪声的影响的仿真波形图,从图11中可以看出,初始状态时,RS触发器850的复位输入端为逻辑低电平且置位输入端为逻辑高电平;在dV/dt瞬变噪声期间,A

图12示出了氮化镓功率器件栅驱动电路输出为高电平时,受dV/dt瞬变噪声的影响的仿真波形图,从图12中可以看出,初始状态时,RS触发器850的复位输入端为逻辑高电平且置位输入端为逻辑低电平;在dV/dt瞬变噪声期间,A

请参考图13,其示出了本申请一个实施例提供的氮化镓功率器件栅驱动电路的结构流程图。该氮化镓功率器件栅驱动电路,可以包括:窄脉冲产生电路1310、高压电平移位电路1320、动态非对称状态产生电路1330、前置放大器1340、共模屏蔽逻辑1350、RS触发器1360和缓冲级1370。

如图13所示,窄脉冲产生电路1310的输入端作为氮化镓功率器件栅驱动电路的输入端IN_H,窄脉冲产生电路1310的第一输出端SET与高压电平移位电路1320的第一输入端相连,窄脉冲产生电路1310的第二输出端RESET与高压电平移位电路1320的第二输入端相连,窄脉冲产生电路1310的电源端与低压侧电源VCC相连,窄脉冲产生电路1310的逻辑地端与芯片地相连;高压电平移位电路1320的第一输出端A

下面分别对高压电平移位电路1320、动态非对称状态产生电路1330、前置放大器1340、共模屏蔽逻辑1350和RS触发器1360的电路结构进行介绍。

1)高压电平移位电路1320;

高压电平移位电路1320可以包括:第一开关N

需要说明的第一点是,第一开关和第二开关除了可以是NLDMOS器件,也可以是LDMOS器件,还可以是其他功率器件,如IGBT、JFET等。

需要说明的第二点是,第一二极管和第二二极管除了可以是二极管,也可以是三极管的基极-发射极二极管或MOS管的体二极管,其作用是钳位A

需要说明的第三点是,第一PMOS管P

2)动态非对称状态产生电路1330;

动态非对称状态产生电路1330可以包括:第三NMOS管N

需要说明的是,锁存器可以PMOS管构成的锁存器,也可以是其他用到负栅-源电压或负基极-发射极电压开通器件的锁存器,只要保证第三NMOS管N

3)前置放大器1340;

前置放大器1340可以包括:第一P型开关P

4)共模屏蔽逻辑1350;

共模屏蔽逻辑1350可以包括:第六与非门NAND

5)RS触发器1360;

RS触发器1360可以包括:第四与非门NAND

本实施例中,前置放大器1340的逻辑作用与共模屏蔽逻辑1350中的反相器是一致的,且其响应阈值比反相器低得多,拓宽了信号的响应范围,可以提高芯片的VS负偏压能力。

图13中所示的氮化镓功率器件栅驱动电路的工作流程与图8所示的氮化镓功率器件栅驱动电路的工作流程相同,不再赘述。

本领域普通技术人员可以理解实现上述实施例的全部或部分步骤可以通过硬件来完成,也可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,上述提到的存储介质可以是只读存储器,磁盘或光盘等。

以上所述并不用以限制本申请实施例,凡在本申请实施例的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本申请实施例的保护范围之内。

- 氮化镓功率器件栅驱动电路

- 氮化镓盖帽层掩模的凹槽栅氮化镓基增强型器件制备方法