具有双TMR膜的磁传感器阵列

文献发布时间:2023-06-19 11:55:48

相关申请的交叉引用

本申请要求于2019年12月18日提交的美国专利申请16/718667的优先权,该美国申请要求于2019年8月27日提交的美国临时专利申请序列号62/892391的权益,其全部内容通过引用方式并入本文。

背景技术

技术领域

本公开的实施方案总体涉及隧穿磁阻传感器设备如惠斯通电桥阵列,及其制造方法。

惠斯通电桥是用于通过平衡电桥电路的两个支路来测量未知电阻的电路,其中一个支路包含未知部件。与简单的分压器相比,惠斯通电路提供了极其准确的测量结果。

惠斯通电桥包括多个电阻器,尤其是最近包括磁性材料诸如磁传感器。磁传感器可包括霍尔效应磁传感器、各向异性磁阻传感器(AMR)、巨磁阻(GMR)传感器和隧穿磁阻(TMR)传感器。与其他磁传感器相比,TMR传感器具有非常高的灵敏度。

典型的惠斯通电桥包括四个电阻器,其中第一电阻器和第四电阻器均包括具有设置在与钉扎层的磁化方向成+45°的磁化方向的自由层,并且第二电阻器和第三电阻器均包括具有设置在与钉扎层的磁化方向成-45°的磁化方向的自由层。所有四个电阻器由相同的材料或膜构成,并且这样,四个电阻器中的每个电阻器的钉扎层具有相同磁化方向。

当向惠斯通电桥施加磁场时,第一电阻器和第四电阻器随所施加的磁场而增大,第二电阻器和第三电阻器随所施加的磁场而减小。然而,由于自由层和钉扎层的磁化方向之间的±45°,这种设计仅可利用一半的磁阻变化。其他惠斯通电桥设计导致输出电压降低或灵敏度有限。

因此,本领域需要在全磁阻范围内操作同时实现最大输出电压或灵敏度的磁性传感器及其制造方法。

发明内容

本申请公开了一种包括一个或多个TMR传感器的TMR传感器设备。该惠斯通电桥阵列包括:第一电阻器,该第一电阻器包括第一TMR膜;第二电阻器,该第二电阻器包括不同于该第一TMR膜的第二TMR膜;第三电阻器,该第三电阻器包括该第二TMR膜;以及第四电阻器,该第四电阻器包括该第一TMR膜。第一TMR膜包括基准层,该基准层具有与钉扎层的第二磁化方向反平行的第一磁化方向。第二TMR膜包括具有平行于第一钉扎层的第二磁化方向的第一磁化方向的基准层,以及具有与基准层的第一磁化方向和第一钉扎层的第二磁化方向反平行的第三磁化方向的第二钉扎层。

在一个实施方案中,TMR传感器设备包括至少一个TMR传感器,该至少一个TMR传感器包括第一TMR膜,第一TMR膜包括具有第一磁化方向的第一基准层和具有第二磁化方向的第一钉扎层,第一基准层的第一磁化方向与第一钉扎层的第二磁化方向反平行,其中该第一钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,并且其中该第一基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆,以及至少一个TMR传感器,该至少一个TMR传感器包括第二TMR膜,该第二TMR膜包括具有第一个第三磁化方向的第二基准层,具有该第一个第三磁化方向的第一个第二钉扎层,以及具有第二个第四磁化方向的第二个第三钉扎层,该第二基准层和该第一个第二钉扎层的第一个第三磁化方向与该第二个第三钉扎层的该第二个第四磁化方向反平行,其中该第二钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,其中该第三钉扎层包括厚度为约35埃至约55埃的Co/CoFe/Co多层叠堆,并且其中该第二基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆。

在另一个实施方案中,TMR传感器设备包括第一电阻器,该第一电阻器包括第一TMR膜,第一TMR膜包括具有第一磁化方向的第一基准层,其中该第一基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆;包括第二电阻器,该第二电阻器包括第二TMR膜,该第二TMR膜包括具有第二磁化方向的第二基准层,其中该第二基准层包含厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆,并且其中第一TMR膜的第一基准层的第一磁化方向与第二TMR膜的第二基准层的第二磁化方向反平行;包括第三电阻器,该第三电阻器包括第二TMR膜;以及包括第四电阻器,该第四电阻器包括第一TMR膜。

在另一个实施方案中,一种制造具有第一电阻器、第二电阻器、第三电阻器和第四电阻器的TMR传感器设备的方法,包括通过沉积第一晶种层、在第一晶种层上沉积第一反铁磁层、在第一反铁磁层上沉积第一钉扎层来形成第一TMR膜,该第一钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,在该第一钉扎层上沉积第一间隔层,在该第一间隔层上沉积第一基准层,该第一基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆,在该第一基准层上沉积第一阻挡层,并且在该第一阻挡层上沉积第一自由层,对该第一TMR膜进行磁退火以将该第一基准层的第一磁化方向改变为与该第一钉扎层的第二磁化方向反平行;通过沉积第二晶种层来形成第二TMR膜,在该第二晶种层上沉积第二反铁磁层,在该第二反铁磁层上沉积第二钉扎层,该第二钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,在该第二钉扎层上沉积第二间隔层,在该第二间隔层上沉积第三钉扎层,该第三钉扎层包括厚度为约35埃至约55埃的Co/CoFe/Co多层叠堆,在该第三钉扎层上沉积第三间隔层,在该第三间隔层上沉积第二基准层,该第二基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆,在该第二基准层上沉积第二阻挡层,并且在该第二阻挡层上沉积第二自由层,对该第二TMR膜进行磁退火以将该第三钉扎层的第三磁化方向改变为与该第二基准层的第四磁化方向反平行,其中该第一TMR膜的该第一基准层的该第一磁化方向与该第二TMR膜的该第二基准层的该第四磁化方向反平行,由该第一TMR膜形成该第一电阻器和该第四电阻器,并且由该第二TMR膜形成该第二电阻器和该第三电阻器,其中该第一电阻器与该第二电阻器和该第三电阻器相邻,该第二电阻器与该第一电阻器和该第四电阻器相邻,该第三电阻器与该第一电阻器和该第四电阻器相邻,并且该第四电阻器与该第二电阻器和该第三电阻器相邻。

附图说明

因此,通过参考实施方案,可以获得详细理解本公开的上述特征的方式、本公开的更具体描述、上述简要概述,所述实施方案中的一些在附图中示出。然而,应当注意的是,附图仅示出了本公开的典型实施方案并且因此不应视为限制其范围,因为本公开可以允许其他同等有效的实施方案。

图1示出了TMR传感器设备的示意图。

图2示出了根据一个实施方案的用于形成TMR传感器设备的电阻器的第一TMR膜和第二TMR膜的示意图。

图3A至图3B示出了根据一个实施方案的处于各种形成阶段的第一TMR膜或TMR膜A。

图4A至图4B示出了根据另一个实施方案的处于各种形成阶段的第二TMR膜或TMR膜B。

图5A至图5B示出了第一TMR膜和第二TMR膜的输出信号与所施加的外场的曲线图。

为了有助于理解,在可能的情况下,使用相同的参考标号来表示附图中共有的相同元件。可以设想是,在一个实施方案中公开的元件可以有利地用于其他实施方案而无需具体叙述。

具体实施方式

在下文中,参考本公开的实施方案。然而,应当理解的是,本公开不限于具体描述的实施方案。相反,思考以下特征和元件的任何组合(无论是否与不同实施方案相关)以实现和实践本公开。此外,尽管本公开的实施方案可以实现优于其他可能解决方案和/或优于现有技术的优点,但是否通过给定实施方案来实现特定优点不是对本公开的限制。因此,以下方面、特征、实施方案和优点仅是说明性的,并且不被认为是所附权利要求书的要素或限制,除非在权利要求书中明确地叙述。同样地,对“本公开”的引用不应当被解释为本文公开的任何发明主题的概括,并且不应当被认为是所附权利要求书的要素或限制,除非在权利要求书中明确地叙述。

公开了一种包括一个或多个TMR传感器的隧穿磁阻(TMR)传感器设备。该惠斯通电桥阵列包括:第一电阻器,该第一电阻器包括第一TMR膜;第二电阻器,该第二电阻器包括不同于该第一TMR膜的第二TMR膜;第三电阻器,该第三电阻器包括该第二TMR膜;以及第四电阻器,该第四电阻器包括该第一TMR膜。第一TMR膜包括基准层,该基准层具有与钉扎层的第二磁化方向反平行的第一磁化方向。第二TMR膜包括具有平行于第一钉扎层的第二磁化方向的第一磁化方向的基准层,以及具有与基准层的第一磁化方向和第一钉扎层的第二磁化方向反平行的第三磁化方向的第二钉扎层。

图1为TMR传感器设备100设计如惠斯通电桥阵列的示意图。TMR传感器设备100包括偏置源102、第一电阻器104、第二电阻器106、第三电阻器108、第四电阻器110、第一传感器112、第二传感器114和接地连接116。从偏置源102到接地连接件116跨阵列施加偏置电压。第一传感器112和第二传感器114感测所施加电压的输出。来自电阻器104、106、108、110的任何温度变化均可被抵消。

如本文所讨论,电阻器104、106、108、110各自包括TMR传感器。在一个实施方案中,TMR传感器各自是独特且不同的,使得电阻器104、106、108、110具有不同电阻。在另一个实施方案中,TMR传感器相同,但是电阻器104、106、108、110不同。在又一个实施方案中,电阻器104、110彼此相同(因为包括电阻器104、110的TMR传感器彼此相同),并且电阻器106、108彼此相同(因为包括电阻器106、108的TMR传感器彼此相同)但与电阻器104、110不同。对于TMR传感器设备100中的TMR传感器,阵列100的RA为约100欧姆/平方微米。

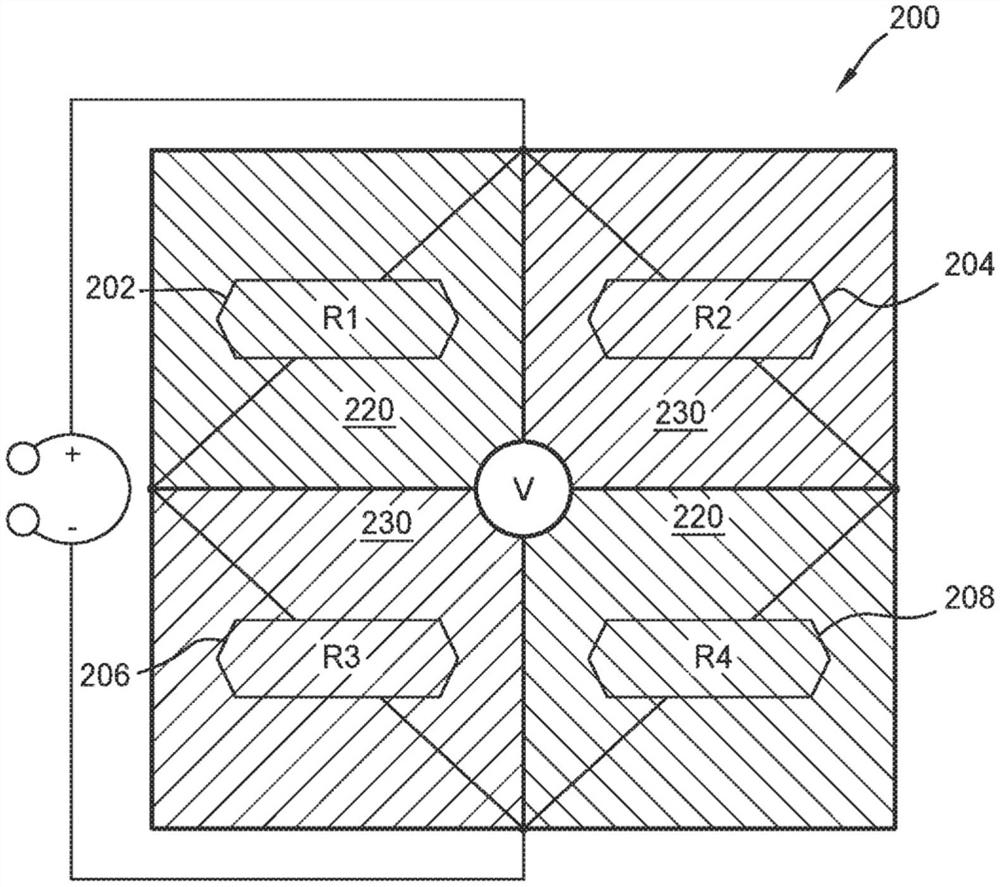

图2为示出根据一个实施方案的用于形成基于TMR的磁传感器或TMR传感器设备200(如惠斯通电桥阵列)的电阻器202、204、206、208的第一TMR膜220和第二TMR膜230的示意图。TMR传感器设备200可为图1的TMR传感器设备100。电阻器202、204、206、208中的每个各自作为TMR传感器工作。

如图2所示,第一电阻器R1 202和第四电阻器R4 208两者均包括第一TMR膜220,而第二电阻器R2 204和第三电阻器R3 206两者均包括第二TMR膜230。由第一TMR膜220形成的第一电阻器R1 202和第四电阻器R4 208的TMR电阻随着外部磁场而线性增大,而由第二TMR膜230形成的第二电阻器R2 204和第三电阻器R3 206的TMR电阻随着外部磁场而线性减小。另选地,由第一TMR膜220形成的第一电阻器R1 202和第四电阻器R4 208的TMR电阻可随着外部磁场而线性减小,而由第二TMR膜230形成的第二电阻器R2 204和第三电阻器R3 206的TMR电阻可随着外部磁场而线性增大。这样,两个不同的TMR膜220、230提供两种不同的磁阻响应。

图3A至图3B示出了根据一个实施方案的图2的处于各种形成阶段的第一TMR膜220或TMR膜A。图3A示出了在磁退火期间的第一TMR膜220,并且图3B示出了在磁退火之后的第一TMR膜220。第一TMR膜220可用作一个或多个TMR传感器。图3B示出了在图2的TMR传感器设备200中使用的第一TMR膜220。

第一TMR膜220包括自由层(FL)302、设置在FL 302下方并与之接触的阻挡层304、设置在阻挡层304下方并与之接触的基准层(RL)306、设置在RL 306下方并与之接触的间隔层308,设置在间隔层308下方并之接触的钉扎层(PL)310、设置在PL 310下方并与之接触的反铁磁(AFM)层312、以及设置在AFM层312下方并与之接触的晶种层314。FL 302也可称为传感层。第一TMR层220具有为约120埃至约630埃的总厚度。

在一个实施方案中,晶种层314包含导电材料如钌,具有为约10埃至约100埃的厚度,并且通过已知的沉积方法如电镀、化学镀或溅镀进行沉积。另外,应当理解,虽然钌已被例示为晶种层314材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将钌用于晶种层314。

用于AFM层312的合适材料包括厚度为约40埃至约100埃的IrMn或PtMn。AFM层312可通过熟知的沉积方法(诸如溅射)形成。另外,应当理解,虽然IrMn和PtMn已被例示为AFM层312材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将IrMn或PtMn用于AFM层312。

用于钉扎层310的合适材料包括厚度为约20埃至约30埃的CoFe或Co/CoFe/Co多层叠堆。在一个实施方案中,CoFe中的Co组分为约25%至70%。钉扎层310可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然CoFe或Co/CoFe/Co已被例示为钉扎层310材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将CoFe或Co/CoFe/Co用于钉扎层310。

用于间隔层308的合适材料包括厚度为约4埃至约10埃的Ru。间隔层308可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然钌已被例示为间隔层308材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将钌用于间隔层308。

用于基准层306的合适材料包括CoFe/Ta/CoFeB/CoFe,作为厚度在约21埃至约37埃的多层叠堆。第一CoFe层可具有为约8埃至约10埃的厚度。在一个实施方案中,第一CoFe层中的Co组分为约0%至25%。Ta层可具有为约0.5埃至约2埃的厚度。CoFeB层可具有为约10埃至约15埃的厚度。在一个实施方案中,CoFeB层中的B组分为约15%至25%。第二CoFe层可具有为约3埃至约10埃的厚度。在一个实施方案中,第二CoFe层中的Co组分为约10%至70%。基准层306可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然CoFe/Ta/CoFeB/CoFe已被例示为基准层306材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将CoFe/Ta/CoFeB/CoFe用于基准层306。

用于阻挡层304的合适材料包括厚度为约10埃至约20埃的MgO。应当理解,虽然MgO被例示为阻挡层304,但也设想了其他绝缘材料。

用于自由层302的合适材料包括厚度为约16埃至约332埃的CoFe/CoFeB/Ta/NiFe多层叠堆。CoFe层可具有为约3埃至约10埃的厚度。CoFeB层可具有为约10埃至约20埃的厚度。Ta层可具有为约0.5埃至约2埃的厚度。NiFe层可具有为约3埃至约300埃,如为约3埃至约10埃或为约10埃至约300埃的厚度。自由层302可通过熟知的沉积方法(诸如溅射)形成。另外,应当理解,虽然CoFe/CoFeB/Ta/NiFe已被例示为自由层302材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将CoFe/CoFeB/Ta/NiFe用于自由层302。

图3A示出了在磁退火期间的第一TMR膜220。在第一TMR膜220的层已被沉积之后,在磁烘箱中,将第一TMR膜220以为约250摄氏度至约300摄氏度的温度以及为约1特斯拉至约5特斯拉的磁场下退火。在磁退火期间,FL 302具有沿x方向指向的磁化方向322,RL 306具有沿x方向指向的第一磁化方向324,并且PL 310具有沿x方向指向的第一磁化方向326。因此,在磁退火期间,PL 310的磁化方向326平行于FL 302的磁化方向322并且平行于RL306的磁化方向324。

在图3B中,在磁退火之后,FL 302具有沿x方向指向的磁化方向322,RL 306具有沿x方向指向的第二磁化方向334,并且PL 310具有沿x方向指向的第一磁化方向326。因此,在磁退火期间,PL 310的磁化方向326平行于FL 302的磁化方向322并且反平行于RL 306的磁化方向334。

PL 310的磁化方向326由AFM层312钉扎,因此,当施加外场时,PL 310的磁矩不改变。RL 306通过间隔层308与PL 310反铁磁耦合。因此,在磁退火之后,当施加外场时,RL306的磁化方向是固定的。当施加外场以获得线性信号时,FL 302可被偏置,并且当施加外场时,FL 302的磁矩可进一步旋转。

图4A至图4B示出了根据一个实施方案的图2的处于各种形成阶段的第二TMR膜230或TMR膜B。图4A示出了在磁退火期间的第二TMR膜230,并且图4B示出了在磁退火之后的第二TMR膜230。第二TMR膜230可用作一个或多个TMR传感器。图4B示出了在图2的TMR传感器设备200中使用的第二TMR膜230。

第二TMR膜230包括FL 402、设置在FL 402下方并与之接触的阻挡层404、设置在阻挡层404下方并与之接触的RL 406、设置在RL 406下方并与之接触的第一间隔层408、设置在第一间隔层408下方并与之接触的第二钉扎层(PL2)416,设置在PL2 416下方并与之接触的第二间隔层418、设置在第二间隔层418下方并与之接触的第一钉扎层(PL1)410、设置在PL1 410下方并与之接触的AFM层412以及设置在AFM层412下方并与之接触的晶种层414。FL402也可称为传感层。第二TMR层230具有为约155埃至约1675埃的总厚度。

在一个实施方案中,晶种层414包含导电材料如钌,具有为约10埃至约100埃的厚度,并且通过已知的沉积方法如电镀、化学镀或溅镀进行沉积。另外,应当理解,虽然钌已被例示为晶种层414材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将钌用于晶种层414。

用于AFM层412的合适材料包括厚度为约40埃至约100埃的IrMn或PtMn。AFM层412可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然IrMn和PtMn已被例示为AFM层412材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将IrMn或PtMn用于AFM层412。

用于第一钉扎层410的合适材料包括厚度为约20埃至约30埃的CoFe或Co/CoFe/Co多层叠堆。在一个实施方案中,CoFe中的Co组分为约25%至70%。第一钉扎层410可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然CoFe或Co/CoFe/Co已被例示为第一钉扎层410的材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将CoFe或Co/CoFe/Co用于第一钉扎层410。

用于第二钉扎层416的合适材料包括厚度为约35埃至约55埃的CoFe或Co/CoFe/Co多层叠堆。因此,第二钉扎层416在y方向具有大于第一钉扎层410的厚度。在一个实施方案中,第二钉扎层416在y方向具有大于第一钉扎层410的1至2倍的厚度。第一Co层的厚度可为约5埃,CoFe层的厚度可为约30埃,第二Co层的厚度可为约5埃。在一个实施方案中,CoFe层中的Co组分为约25%至70%。第二钉扎层416可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然CoFe或Co/CoFe/Co已被例示为第二钉扎层416的材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将CoFe或Co/CoFe/Co用于第二钉扎层416。

用于第一和第二间隔层408、418各层的合适材料包括厚度为约4埃至约10埃的Ru。第一间隔层408和第二间隔层418可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然钌已被例示为第一间隔层408和第二间隔层418的材料,但还设想了其他材料,并且本文所讨论的实施方案不限于用于第一间隔层408和第二间隔层418的钌。

用于基准层406的合适材料包括CoFe/Ta/CoFeB/CoFe,作为厚度在约21埃至约37埃的多层叠堆。第一CoFe层可具有为约8埃至约10埃的厚度。在一个实施方案中,第一CoFe层中的Co组分为约0%至25%。Ta层可具有为约0.5埃至约2埃的厚度。CoFeB层可具有为约10埃至约15埃的厚度。在一个实施方案中,CoFeB中的B组分为约15%至25%。第二CoFe层可具有为约3埃至约10埃的厚度。在一个实施方案中,第二CoFe层中的Co组分为约10%至70%。基准层406可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然CoFe/Ta/CoFeB/CoFe已被例示为基准层406材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将CoFe/Ta/CoFeB/CoFe用于基准层406。

用于阻挡层404的合适材料包括厚度为约10埃至约20埃的MgO。应当理解,虽然MgO被例示为阻挡层404,但也设想了其他绝缘材料。

用于自由层402的合适材料包括厚度为约16埃至约332埃的CoFe/CoFeB/Ta/NiFe多层叠堆。CoFe层可具有为约3埃至约10埃的厚度。CoFeB层可具有为约10埃至约20埃的厚度。Ta层可具有为约0.5埃至约2埃的厚度。NiFe层可具有为约3埃至约300埃,如为约3埃至约10埃或为约10埃至约300埃的厚度。自由层402可通过已知的沉积方法(如溅射)形成。另外,应当理解,虽然CoFe/CoFeB/Ta/NiFe已被例示为自由层402材料,但也设想了其他材料,并且本文所讨论的实施方案不限于将CoFe/CoFeB/Ta/NiFe用于自由层402。

图4A示出了在磁退火期间的第二TMR膜230。在第二TMR膜230的层已被沉积之后,在磁烘箱中,将第二TMR膜230以为约250摄氏度至约300摄氏度的温度以及为约1特斯拉至约5特斯拉的磁场下退火。在磁退火期间,FL 402具有沿x方向指向的磁化方向422,RL 406具有沿x方向指向的第一磁化方向424,PL1 410具有沿x方向指向的第一磁化方向426,并且PL2416具有沿x方向指向的第一磁化方向428。因此,在磁退火期间,PL1 410的磁化方向426平行于FL 402的磁化方向422和RL 406的磁化方向424,并且平行于PL2 416的磁化方向428。

在图4B中,在磁退火之后,FL 402具有沿x方向指向的磁化方向422,RL 406具有沿x方向指向的第一磁化方向424,PL1 410具有沿x方向指向的第一磁化方向426,并且PL2416具有沿x方向指向的第二磁化方向438。因此,在磁退火之后,PL1 410的磁化方向426平行于FL 402的磁化方向422并且平行于RL 406的磁化方向424。然而,PL1 410的磁化方向426与PL2 418的磁化方向438反平行。

PL1 410的磁化方向426由AFM层412钉扎,因此,当在工作场范围内(如小于600Oe)施加外场时,PL1 410的磁矩不改变。RL 406通过第一间隔层408与PL 410反铁磁耦合。因此,在磁退火之后,当在工作场范围内(如小于600Oe)施加外场时,RL 406的磁化方向是固定的。当施加外场以获得线性信号时,FL 402可被偏置,并且当施加外场时,FL 402的磁矩可进一步旋转。

第一TMR膜220与用于形成图2的TMR传感器设备200的第二TMR膜230相比较而言,第一TMR膜220的FL 302的磁化方向322指向x方向并且平行于第二膜的FL 402的磁化方向422,该磁化方向也指向x方向。第一TMR膜220的RL 306的磁化方向334指向x方向并且与第二TMR膜230的RL 406的磁化方向424反平行,该磁化方向指向x方向。第一TMR膜220的PL310的磁化方向326指向x方向并且与第二TMR膜230的PL1410的磁化方向426平行,该磁化方向也指向x方向。第二膜的PL2 418的磁化方向438指向x方向,平行于第一TMR膜220的RL306的磁化方向334,并且与第二TMR膜230的RL 406的磁化方向424反平行。

因为第一TMR膜220和第二TMR膜230具有不同的RL磁化方向,所以每个膜的TMR电阻响应相等但相反(即,当一个膜线性减小时,另一个膜线性增加)。因此,图2的TMR传感器设备200中的所有电阻器202、204、206、208可在全磁阻范围内操作,同时实现给定TMR比的最大输出电压或灵敏度。

为了形成图2的TMR传感器设备200,第一TMR膜220的层中的每个层和第二TMR膜230的层中的每个层可单独沉积。第一TMR膜220和第二TMR膜230的层可同时沉积,或者一个TMR膜的层可在沉积另一个TMR膜的层之前沉积(例如,沉积第二TMR膜230的每个层,然后沉积第一TMR膜220的每个层)。为了形成第一TMR膜220,沉积晶种层314,将AFM层312沉积在晶种层314上,将钉扎层310沉积在AFM层312上,将间隔层308沉积在钉扎层310上,基准层306沉积在间隔层308上,阻挡层304沉积在基准层306上,并且自由层302沉积在阻挡层304上。

基准层306可以在沉积阻挡层304之前进行等离子体处理,以使基准层306的表面平滑,或者减小基准层306的表面粗糙度,并且增强第一TMR膜220的质量。基准层306包含CoFe/Ta/CoFeB/等离子体处理/CoFe作为多层叠堆。等离子体处理以低功率(如约35W)执行,以略微蚀刻无定形CoFeB层并使CoFeB层更平滑。

为了形成第二TMR膜230,沉积晶种层414,将AFM层412沉积在晶种层414上,将第一钉扎层410沉积在AFM层412上,将第二间隔层418沉积在第一钉扎层410上,将第二钉扎层416沉积在第二间隔层418上,第一间隔层408沉积在第二钉扎层416上,基准层406沉积在第一间隔层408上,阻挡层404沉积在基准层406上,并且自由层402沉积在阻挡层404上。

基准层406可以在沉积阻挡层404之前进行等离子体处理,以使基准层406的表面平滑,或者减小基准层406的表面粗糙度,并且增强第二TMR膜230的质量。基准层406包含CoFe/Ta/CoFeB/等离子体处理/CoFe作为多层叠堆。等离子体处理以低功率(如约35W)执行,以略微蚀刻无定形CoFeB层并使CoFeB层更平滑。

然后,第一TMR膜220和第二TMR膜230可在磁烘箱中同时或单独地在约250摄氏度至约300摄氏度的温度下在约1特斯拉至约5特斯拉的磁场下加热。然后,第一TMR膜220和第二TMR膜230可沉积在一个或多个底部引线上。例如,第一TMR膜220可沉积在第一底部引线和第二底部引线上方,并且第二TMR膜230可沉积在第三底部引线和第四底部引线上方。然后可在第一TMR膜220和第二TMR膜230上方形成一个或多个顶部引线。例如,第一顶部引线可形成在第一底部引线上方,第二顶部引线可形成在第二底部引线上方,第三顶部引线可形成在第三底部引线上方,并且第四顶部引线可形成在第四底部引线上方。

图5A至图5B分别示出了第一TMR膜和第二TMR膜的输出信号与所施加的外场的曲线图500、550。图5A示出了图2和图3B的第一TMR膜220的输出信号或电阻率(R)相对于施加的外场(H)的曲线图500。图5B示出了图2和图4B的第二TMR膜230的输出信号或电阻率(R)相对于所施加的外场(H)的曲线图550。

如图5A所示,第一TMR膜的TMR电阻随着所施加的场而线性增加。第一TMR膜的磁化方向324基准层是固定的并且指向x方向。自由层的磁化方向422随着外场增加而旋转,首先指向x方向,然后指向y方向,然后指向x方向。

如图5B所示,第二TMR膜的TMR电阻随着所施加的场而线性减小。第二TMR膜的磁化方向424基准层是固定的并且指向x方向。自由层的磁化方向422随着外场增加而旋转,首先指向x方向,然后指向y方向,然后指向x方向。

图5A和5B表明,由于第一TMR膜220和第二TMR膜230具有不同的RL磁化方向,所以每个膜的TMR电阻响应相等但相反(即,第一TMR膜线性增加时,第二TMR膜线性减小)。

因此,利用具有由两种不同TMR膜构成的四个电阻器的上述TMR传感器设备或惠斯通电桥设计使得磁传感器在全磁阻范围内操作,同时实现最大输出电压。通过使用用于第一电阻器和第四电阻器的第一TMR膜和用于第二电阻器和第三电阻器的第二TMR膜,电阻器的磁阻响应相等但相反,从而实现对于给定的TMR比达到最大灵敏度的全桥感测方案。

在一个实施方案中,TMR传感器用于作为单轴传感器操作的相机中。此类传感器的示例见于美国专利申请公布2019/0020822 A1中,该专利申请公布以引用方式并入本文。然而,预期TMR传感器可用作二维或甚至三维传感器。另外,预期TMR传感器可集成并用于除了相机之外的惯性测量单元技术中,诸如可穿戴装置、罗盘和MEMS装置。此外,TMR传感器可作为位置传感器、桥角传感器、磁开关、电流传感器或它们的组合来操作。TMR传感器可用于通过使用TMR传感器作为位置和角度传感器来聚焦相机,诸如智能电话相机。另外,TMR传感器在汽车工业中也可以作为开关、电流和角度传感器来替代电流霍尔传感器、各向异性磁阻(AMR)传感器和巨磁阻(GMR)传感器。TMR传感器也可在无人机和机器人工业中用作位置和角度传感器。医疗装置也可利用TMR传感器来对输注系统进行流量控制,还可以使用内窥镜相机传感器等。因此,本文所讨论的TMR传感器具有远远超出智能电话相机的应用,并且因此不应限于用作智能电话相机的传感器。此外,TMR传感器不需要布置成惠斯通电桥布置,而是能够以任何数量的方式布置。

在一个实施方案中,TMR传感器设备包括至少一个TMR传感器,该至少一个TMR传感器包括第一TMR膜,第一TMR膜包括具有第一磁化方向的第一基准层和具有第二磁化方向的第一钉扎层,第一基准层的第一磁化方向与第一钉扎层的第二磁化方向反平行,其中该第一钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,并且其中该第一基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆,以及至少一个TMR传感器,该至少一个TMR传感器包括第二TMR膜,该第二TMR膜包括具有第一个第三磁化方向的第二基准层,具有该第一个第三磁化方向的第一个第二钉扎层,以及具有第二个第四磁化方向的第二个第三钉扎层,该第二基准层和该第一个第二钉扎层的第一个第三磁化方向与该第二个第三钉扎层的该第二个第四磁化方向反平行,其中该第二钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,其中该第三钉扎层包括厚度为约35埃至约55埃的Co/CoFe/Co多层叠堆,并且其中该第二基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆。

由第一TMR膜构成的至少一个TMR传感器包括第一TMR传感器和第四TMR传感器,并且由第二TMR膜构成的至少一个TMR传感器包括第二TMR传感器和第三TMR传感器。该第一TMR传感器相邻于该第二TMR传感器和该第三TMR传感器,该第二TMR传感器相邻于该第一TMR传感器和该第四TMR传感器,该第三TMR传感器相邻于该第一TMR传感器和该第四TMR传感器,并且该第四TMR传感器相邻于该第二TMR传感器和该第三TMR传感器。第一TMR膜还包括第一自由层、第一阻挡层、第一间隔层、第一反铁磁层和第一晶种层。第一阻挡层设置在第一基准层和第一自由层之间,第一间隔层设置在第一基准层和第一钉扎层之间,并且第一反铁磁层设置在第一钉扎层和第一晶种层之间。

该第二TMR膜还包括第二自由层、第二阻挡层、第二间隔层、第三间隔层、第二反铁磁层和第二晶种层,并且该第二阻挡层设置在该第二基准层和该第二自由层之间,该第二间隔层设置在该第二基准层和该第三钉扎层之间,该第三间隔层设置在该第二钉扎层和该第三钉扎层之间,并且该第二反铁磁层设置在该第二钉扎层和该第二晶种层之间。第一TMR膜具有约120埃至约630埃的总厚度,并且其中第二TMR膜具有约155埃至约1675埃的总厚度。该第一钉扎层的该Co/CoFe/Co多层叠堆的CoFe中的Co组分为约25%至70%,其中该第一基准层的该CoFe/Ta/CoFeB/CoFe多层叠堆的CoFeB中的B组分为约15%至25%,其中该第二钉扎层的该Co/CoFe/Co多层叠堆的CoFe中的Co组分为约25%至70%,并且其中该第三钉扎层的该Co/CoFe/Co多层叠堆的CoFe中的Co组分为约25%至70%。

在另一个实施方案中,TMR传感器设备包括第一电阻器,该第一电阻器包括第一TMR膜,第一TMR膜包括具有第一磁化方向的第一基准层,其中该第一基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆;包括第二电阻器,该第二电阻器包括第二TMR膜,该第二TMR膜包括具有第二磁化方向的第二基准层,其中该第二基准层包含厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆,并且其中第一TMR膜的第一基准层的第一磁化方向与第二TMR膜的第二基准层的第二磁化方向反平行;包括第三电阻器,该第三电阻器包括第二TMR膜;以及包括第四电阻器,该第四电阻器包括第一TMR膜。

第一TMR膜还包括第一自由层、第一阻挡层、第一间隔层、第一钉扎层、第一反铁磁层和第一晶种层。第一阻挡层设置在第一基准层和第一自由层之间,第一间隔层设置在第一基准层和第一钉扎层之间,并且第一反铁磁层设置在第一钉扎层和第一晶种层之间。第二TMR膜还包括第二自由层、第二阻挡层、第二间隔层、第二钉扎层、第三间隔层、第三钉扎层、第二反铁磁层和第二晶种层。该第二阻挡层设置在该第二基准层和该第二自由层之间,该第二间隔层设置在该第二基准层和该第三钉扎层之间,该第三间隔层设置在该第二钉扎层和该第三钉扎层之间,并且该第二反铁磁层设置在该第二钉扎层和该第二晶种层之间。

该第二TMR膜的该第三钉扎层具有与该第一TMR膜的第一基准层的第一磁化方向平行的第三磁化方向。该第一TMR膜的该第一自由层具有与该第二TMR膜的第二自由层的第五磁化方向平行的第四磁化方向。第一TMR膜的第一自由层的第四磁化平行于第一TMR膜的第一钉扎层的第六磁化方向。该第一TMR膜的该第一钉扎层包括厚度为约20埃至约30埃之间的Co/CoFe/Co多层叠堆,其中该第二TMR膜的该第二钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,并且其中该第二TMR膜的该第三钉扎层包括厚度为约35埃至约55埃的Co/CoFe/Co多层叠堆,其中该第二TMR膜的该第二钉扎层具有比该第二TMR膜的该第一钉扎层大的厚度。第一TMR膜具有约120埃至约630埃的总厚度,并且其中第二TMR膜具有约155埃至约1675埃的总厚度。

在另一个实施方案中,一种制造具有第一电阻器、第二电阻器、第三电阻器和第四电阻器的TMR传感器设备的方法,包括通过沉积第一晶种层、在第一晶种层上沉积第一反铁磁层、在第一反铁磁层上沉积第一钉扎层来形成第一TMR膜,该第一钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,在该第一钉扎层上沉积第一间隔层,在该第一间隔层上沉积第一基准层,该第一基准层包括厚度为约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆,在该第一基准层上沉积第一阻挡层,并且在该第一阻挡层上沉积第一自由层,对该第一TMR膜进行磁退火以将该第一基准层的第一磁化方向改变为与该第一钉扎层的第二磁化方向反平行;通过沉积第二晶种层来形成第二TMR膜,在该第二晶种层上沉积第二反铁磁层,在该第二反铁磁层上沉积第二钉扎层,该第二钉扎层包括厚度为约20埃至约30埃的Co/CoFe/Co多层叠堆,在该第二钉扎层上沉积第二间隔层,在该第二间隔层上沉积第三钉扎层,该第三钉扎层包括厚度为约35埃至约55埃的Co/CoFe/Co多层叠堆,在该第三钉扎层上沉积第三间隔层,在该第三间隔层上沉积第二基准层,该第二基准层包括厚度在约21埃至约37埃的CoFe/Ta/CoFeB/CoFe多层叠堆,在该第二基准层上沉积第二阻挡层,并且在该第二阻挡层上沉积第二自由层,对该第二TMR膜进行磁退火以将该第三钉扎层的第三磁化方向改变为与该第二基准层的第四磁化方向反平行,其中该第一TMR膜的该第一基准层的该第一磁化方向与该第二TMR膜的该第二基准层的该第四磁化方向反平行,由该第一TMR膜形成该第一电阻器和该第四电阻器,并且由该第二TMR膜形成该第二电阻器和该第三电阻器,其中该第一电阻器与该第二电阻器和该第三电阻器相邻,该第二电阻器与该第一电阻器和该第四电阻器相邻,该第三电阻器与该第一电阻器和该第四电阻器相邻,并且该第四电阻器与该第二电阻器和该第三电阻器相邻。

在磁烘箱中将第一TMR膜和第二TMR膜以为约250摄氏度至约300摄氏度的温度以及为约1特斯拉至约5特斯拉的磁场下磁退火。由该第一TMR膜形成该第一电阻器和该第四电阻器包括在第一底部引线和第二底部引线上方沉积该第一TMR膜,并且在该第一底部引线上方形成第一顶部引线并且在该第二底部引线上方形成第二顶部引线。由该第二TMR膜形成该第二电阻器和该第三电阻器包括在第三底部引线和第四底部引线上方沉积该第二TMR膜,并且在该第三底部引线上方形成第三顶部引线并且在该第四底部引线上方形成第四顶部引线。第一TMR膜具有约120埃至约630埃的总厚度,并且其中第二TMR膜具有约155埃至约1675埃的总厚度。该第一电阻器、该第二电阻器、该第三电阻器和该第四电阻器是TMR传感器。

虽然前述内容针对本公开的实施方案,但是可以在不脱离本公开的基本范围的情况下设想本公开的其他和另外的实施方案,并且本公开的范围由所附权利要求书确定。

- 具有双TMR膜的磁传感器阵列

- 具有包括两个自由层的一个TMR叠堆的磁传感器阵列