低电压反熔丝元件

文献发布时间:2023-06-19 12:07:15

技术领域

本发明有关一种非挥发性存储器,特别是关于一种利用改良闸极结构达到降低击穿电压的低电压反熔丝元件。

背景技术

在计算机信息产品发达的今天,具备有电性编写和抹除数据功能的非挥发性存储器,如EEPROM、flash,能在电源关掉后所储存的数据不会消失,所以被广泛使用于电子产品上。然而,这些只读存储器或高速缓存的结构相对复杂,可靠性相对较低,且制造成本高。因此,很多地方可以使用可靠性高、制造成本低的单次可程序化存储器(one timeprogrammable memory,简称OTP),使用熔丝(fuse)或反熔丝(anti-fuse)作为元件的单次可程序化存储器在使用上更具有弹性。

传统的熔丝主要有金属熔丝(metal Fuse)及复晶硅熔丝(Poly Fuse),写入方式是以高能量激光或大电流烧断熔丝的方式为主,写入后熔丝的电阻值会上升,消耗功率较大。而反熔丝主要以电容方式在两个导体间加入介电层,写入时在两端导体各加一偏压使该介电层崩溃而击穿,写入后反熔丝的电阻值会下降。随着集成电路的高速发展,元件尺寸日益缩小,近年来已发展出使用MOS元件制作反熔丝元件,其写入方式是以闸极介电层崩溃机制为主。

由于反熔丝元件基于闸极介电层的破裂以形成永久的导电路径,其局限在于必须施加使闸极介电层崩溃的高电压,相对也需要消耗高电流,才能达成击穿闸极介电层的目的。另一方面,以先进的制程技术生产非挥发性存储器,往往需要增加很多道制程,不但增加了制造的困难度,也增加了生产成本,尤其是在嵌入式(embedded)产品;故目前先进的制程技术,都是往低电压发展。

发明内容

鉴于以上的问题,本发明的主要目的在于提供一种低电压反熔丝元件,将闸极介电层上的闸极形成具有延伸渐缩的尖角部,进行操作时,电荷于尖角处的密度较高,以降低击穿电压,可大幅降低程序化反熔丝元件的电流需求。

因此,为达上述目的,本发明提供一种低电压反熔丝元件,包含基底、第一闸极介电层、第一闸极以及第一离子掺杂区。第一闸极介电层设置在基底上。第一闸极包含本体部及自本体部一侧延伸渐缩形成的尖角部,且本体部及尖角部邻接于第一闸极介电层上。第一离子掺杂区设置在第一闸极介电层一侧的基底中。其中,当写入电压被施加于第一闸极及第一离子掺杂区之间时,产生一电场,此电场会集中于尖角部,使得尖角部下方的第一闸极介电层的一部分易于击穿,以降低击穿电压。

在本发明的一实施例中,基底为P型半导体基底或N型半导体基底;当基底为P型半导体基底时,则第一离子掺杂区为N型掺杂区,当基底为N型半导体基底时,则第一离子掺杂区为P型掺杂区。

在本发明的一实施例中,还包含邻近第一离子掺杂区的存取晶体管,存取晶体管包含第二介电层、第二闸极及第二离子掺杂区。第二介电层设置在基底上,第二闸极叠设于第二闸极介电层上,第二离子掺杂区位于第二闸极介电层远离第一离子掺杂区的一侧的基底中,且第一离子掺杂区与第二离子掺杂区掺杂同型的离子。

在本发明的一实施例中,还包含井区,井区设置于基底内并位于第一离子掺杂区下方,且井区与第一离子掺杂区掺杂不同型的离子。

由于闸极结构设计成具有尖角部,以利用电荷于尖角处的密度较高的原理,尖角处下方的第一闸极介电层将更易于击穿,可以使用低操作电压、低操作电流,同时可减少闸极面积,达到缩小元件尺寸的效果,从而可降低反熔丝元件的生产成本。

以下通过具体实施例配合所附的图式详加说明,当更容易了解本发明的目的、技术内容、特点及其所达成的功效。

附图说明

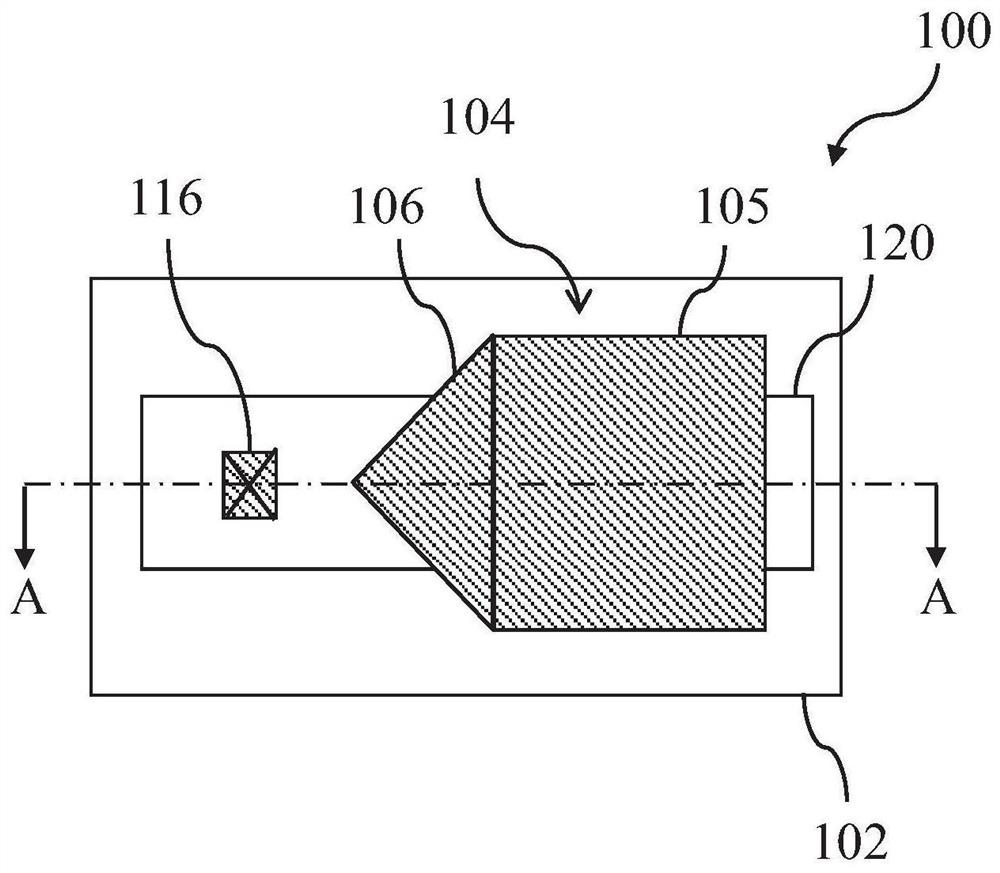

图1为本发明第一实施例的低电压反熔丝元件的平面图。

图2为图1沿线A-A的低电压反熔丝元件的剖面图。

图3为本发明第二实施例的低电压反熔丝元件的平面图。

图4为图3沿线B-B的低电压反熔丝元件的剖面图。

附图标记说明:100-低电压反熔丝元件;102-基底;104-第一闸极;105-本体部;106-尖角部;108-第一闸极介电层;110-侧壁间隔物;112-第一离子掺杂区;114-通道区;116-位元线接点;118-LDD区;120-作用区域;200-低电压反熔丝元件;202-存取晶体管;204-井区;206-第二闸极;207-侧壁间隔物;208-第二闸极介电层;210-第二离子掺杂区;212-位元线接点;214-作用区域;216-LDD区;218-通道区;WL-字线;BL-位元线;Vcp-胞元屏极电压。

具体实施方式

请参照图1,其显示本发明的第一实施例所提供的低电压反熔丝元件的平面图;同时请参照图2,其则显示图1的低电压反熔丝元件的剖面图。

本实施例中,低电压反熔丝元件100包括基底102、第一闸极104、第一闸极介电层108、侧壁间隔物110、第一离子掺杂区112、通道区114以及位元线接点116。其中,第一闸极介电层108形成于基底102上,第一闸极104叠设于第一闸极介电层108上,侧壁间隔物110设于第一闸极104的两侧,第一离子掺杂区112形成于第一闸极介电层108的一侧的基底102中,并可具有邻近第一闸极介电层108的垂直边缘的轻微掺杂(LDD)区118,且第一离子掺杂区112、LDD区118及通道区114位于作用区域120中。进一步来说,第一闸极104具有本体部105和自本体105部分一侧延伸渐缩形成的尖角部106,本体部105及尖角部106形成于第一闸极介电层108上方,以接触第一闸极介电层108。更具体地,第一闸极104的尖角部106的形状大致上为三角形,其从本体部105的一侧延伸而出,可使用与本体部105相同或不同的材料,本体部105及尖角部106形成为在基底102上的作用区域120重叠,且尖角部106的数量、尺寸并不限制,实际实施时较佳的数量为一个,并可根据预设写入电压与第一闸极介电层108的厚度而适当地选择。

本实施例中,基底102可为P型半导体基底或N型半导体基底;当基底102为P型半导体基底时,则第一离子掺杂区112为N型掺杂区,当基底102为N型半导体基底时,则第一离子掺杂区112为P型掺杂区。第一闸极介电层108位于第一闸极104之下,第一闸极介电层108大致上厚度均匀并且材料为相对较薄的闸极氧化物,其材料可选自氧化物层、氮化物层、氧氮化物层、金属氧化物层或氧化物层、氮化物层、氧氮化物层、金属氧化物层中至少两者的组合。

本实施例中,第一闸极104连接至字线WL,第一离子掺杂区112是经由位元线接点116,或用于感测来自第一闸极104的电流的其他线而连接至位元线BL,并可经掺杂而适应程序化电压或电流。当写入操作时,通过字线WL施加写入电压于第一闸极104,施加位元线电压于第一离子掺杂区112,从而在第一闸极104和第一离子掺杂区112之间产生电场,利用尖端放电的原理,第一闸极104的尖角部106由于电荷大量集中,电场较强,使得尖角部106下方所对应的第一闸极介电层108的一部分崩溃所需的写入电压降低,更容易被击穿,并能缩短写入时间。

接下来通过图3及图4说明本发明的第二实施例,低电压反熔丝元件200可串联存取晶体管202。请参照图3,其显示本发明的第二实施例所提供的低电压反熔丝元件的平面图;同时请参照图4,其显示图3的低电压反熔丝元件200的剖面图。

本实施例中,低电压反熔丝元件200包括邻近第一离子掺杂区112的存取晶体管202。低电压反熔丝元件200的反熔丝结构可与图1和图2中所示相似,因此以相同编号标示相同先前描述的部件。更具体地说,第一闸极104的结构与图2中所示相同,同样具有本体部105和尖角部106,只是第一离子掺杂区112不具有形成于其上的位元线接点。

低电压反熔丝元件200及存取晶体管202具有设置在基底102上的井区204,第二闸极介电层208设置于井区204上,第二闸极206覆盖第二闸极介电层208,其两侧具有侧壁间隔物207,第一离子掺杂区112形成于第二闸极介电层208的一侧,第二离子掺杂区210形成于第二闸极介电层208的另一侧,并且具有形成于其上而制造与位元线(图中未示)电接触的位元线接点212。第二离子掺杂区210可具有邻近于第二闸极介电层208的垂直边缘的轻微掺杂(LDD)区216。井区204包括作用区域214,且第一离子掺杂区112、第二离子掺杂区210、LDD区118、LDD区216、通道区114及通道区218位于作用区域214中。第一离子掺杂区112和第二离子掺杂区210可掺杂同型的离子,第一离子掺杂区112和井区204掺杂不同型的离子,且可为不同掺杂浓度,取决于所欲操作电压。

本实施例中,基底102可为P型半导体基底或N型半导体基底;当基底102为P型半导体基底,则第一离子掺杂区112和第二离子掺杂区210为N型掺杂区,井区204为P型掺杂区,当基底102为N型半导体基底,则第一离子掺杂区112和第二离子掺杂区210为P型掺杂区,井区204为N型掺杂区。第一闸极介电层108位于第一闸极104之下,第一闸极介电层108相对较薄且大致上厚度均匀并且其材料为闸极氧化物,其材料可选自氧化物层、氮化物层、氧氮化物层、金属氧化物层或氧化物层、氮化物层、氧氮化物层、金属氧化物层中至少两者的组合。上述实施例的低电压反熔丝元件100、200可以任何标准CMOS程序制造,诸如侧壁间隔物的形成、轻微掺杂(LDD)与闸极硅化。存取晶体管202的第二闸极介电层208为于形成第一闸极介电层108的相同时间形成,因此,第二闸极介电层208及第一闸极介电层108具有实质上相同的组成,且可具有相同或不同厚度。

本实施例的低电压反熔丝元件200的操作,类似第一实施例的低电压反熔丝元件100。存取晶体管202的第二离子掺杂区210经由位元线接点212耦接位元线BL至第一离子掺杂区112,字线WL耦接至存取晶体管202的第二闸极206,胞元屏极电压Vcp耦接至第一闸极104。当写入操作时,将写入电压施加于Vcp多晶硅线,同时位元线BL接地,开启存取晶体管202以经由位元线耦接第一离子掺杂区112至接地,以在第一闸极104和第一离子掺杂区112之间产生电场,利用尖端放电的原理,第一闸极104的尖角部106由于电荷大量集中,电场较强,使得尖角部106下方所对应的第一闸极介电层108的部分崩溃所需的写入电压降低,更容易被击穿,并能缩短写入时间。

综上所述,根据本发明所提供的低电压反熔丝元件,此反熔丝元件是利用电压击穿闸极介电层以导通电路,相较于传统的反熔丝元件的闸极于闸极介电层上方的形状多呈具有垂直边的方形,其电荷密度平均,因此需要高电压,相对也需要较高电流。本发明的低电压反熔丝元件则将闸极结构设计成具有尖角部,进行操作时,电荷于尖角处的密度较高,使得尖角部下方的闸极介电层的部分易于击穿,从而降低击穿电压,达成降低电流消耗的目的。同时,本发明还可以减少闸极面积,达到缩小元件尺寸的效果,可降低生产成本。

以上所述通过实施例说明本发明的特点,其目的在使熟习该技术者能了解本发明的内容并据以实施,而非限定本发明的专利范围,故凡其他未脱离本发明所揭示的精神所完成的等效修饰或修改,仍应包含在本案的保护范围内。

- 低电压反熔丝元件

- 反熔丝元件、反熔丝元件的制造方法及半导体器件