一种用于EEG信号采集的模拟前端AFE电路

文献发布时间:2023-06-19 12:10:19

技术领域

本发明涉及电路技术领域,特别是涉及一种用于EEG信号采集的模拟前端AFE电路。

背景技术

EEG信号代表脑电图,脑电图是脑神经细胞电生理活动在大脑皮层或头皮表面的总体反映。脑电信号中包含了大量的生理与疾病信息,并广泛应用于脑活动分析和疾病诊断。但是由于EEG信号幅值低、随机性和非线性强,在采集过程中极易受到其他信号的影响,增加后续分析难度。

由于脑电信号是大脑皮层神经元群同步放电经由皮层、脑脊液、硬膜、颅骨与头皮等多层组织传递到放置于头皮的电极采集得到,极易被污染,很可能使得EEG中隐含的大脑功能信息被噪声掩盖,甚至得出错误的结论。常见的EEG信号噪声可以分为非生理性和生理性。在生理性噪声中,比如:呼吸,心跳。非生理性噪声,比如:工频,手机射频等。

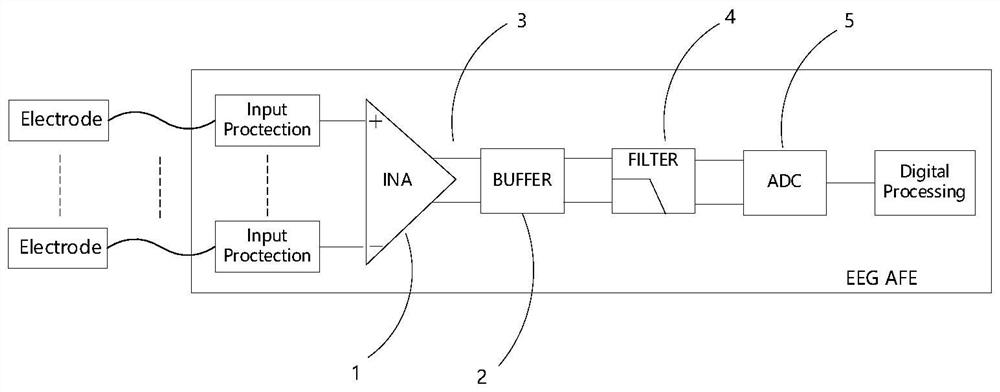

现有的EEG数据采集方案是:AFE前端采用仪表放大器(INA)差分输入,单端输出。然后单端进行放大,滤波,数据送入模数转换器 ADC进行采样。请参考图1,图1为现有技术中基于EEG信号的模拟前端AFE结构示意图,即EEG AFE,图中标记6表示单端信号。仪表放大器是标准的三运放架构,为了满足共模抑制比CMRR要求,仪表放大器内部对差分信号使用减法器,这样会导致输出是单端信号。同时单端信号在后面链路中滤波,放大,缓冲,ADC采样都比较好处理。EEG信号单端信号,无论是精度,信噪比,抗干扰能力都不如差分信号。但是现有的仪表放大器都是单端输出的,无法满足全差分的需求。所以在追求高性能EEG数据采集信号时,EEG全差分链路出色的性能就显得很重要。

因此,如何提供全新的全差分链路架构,提高信噪比和抗干扰能力是亟待解决的问题。

发明内容

本发明的目的是提供一种用于EEG信号采集的模拟前端 AFE电路,实现提供全新的全差分链路架构,提高信噪比和抗干扰能力。

为解决上述技术问题,本发明提供一种用于EEG信号采集的模拟前端AFE电路,包括:

仪表放大器;所述仪表放大器为差分输出的仪表放大器;

与所述仪表放大器相连的信号缓冲器;

与所述信号缓冲器相连的差分低通滤波器;

与所述差分低通滤波器相连的模数转化器。

优选的,所述模拟前端AFE电路还包括:

与所述仪表放大器的第一输入端和第二输入端均相连的输入保护器件;

与所述模数转化器相连的数字处理器。

优选的,所述仪表放大器的第一输出端和第二输出端分别与所述信号缓冲器的第一输入端和第二输入端相连;

所述信号缓冲器的第一输出端和第二输出端分别与所述差分低通滤波器的第一输入端和第二输入端相连;

所述差分低通滤波器的第一输出端和第二输出端分别与所述模数转化器的第一输入端和第二输入端相连。

优选的,所述仪表放大器输出差分信号,采用两个三运放仪表放大器交叉连接,包括第一三运放仪表放大器、第二三运放仪表放大器以及增益电阻R0。

优选的,第一三运放仪表放大器包括运算放大器A1、A2、A3和电阻R1、R2、R3、R4、R5、R11,第二三运放仪表放大器包括运算放大器A4、A5、A6和电阻R6、R7、R8、R9、R10、R12。

优选的,所述运算放大器A1的同相输入端与运算放大器A2的同相输入端均与所述差分输出的仪表放大器的第一输入端相连,运算放大器A1的输出端经电阻R1连接A1的反相输入端,运算放大器A2 的输出端经R2连接A2的反相输入端;运算放大器A3的反相输入端分两路,一路经R3连接A1的输出端,另一路连接R5的一端,R5 的另一端和A3的输出端均与所述差分输出的仪表放大器的第一输出端相连;运算放大器A3的同相输入端分两路,一路经R4连接A2的输出端,另一路经R11接地。

优选的,所述运算放大器A4的同相输入端与运算放大器A5的同相输入端均与所述差分输出的仪表放大器的第二输入端相连,运算放大器A4的输出端经电阻R6连接A4的反相输入端,运算放大器A5 的输出端经R7连接A5的反相输入端;运算放大器A6的反相输入端分两路,一路经R8连接A4的输出端,另一路经R12接地,运算放大器A6的同相输入端分两路,一路经R9连接A5的输出端,另一路连接R10的一端,R10的另一端和A6的输出端均与所述差分输出的仪表放大器的第二输出端相连;A5的反相输入端和A1的反相输入端通过增益电阻R0相连。

本发明所提供的一种用于EEG信号采集的模拟前端AFE电路,对传统的EEG AFE单端链路进行了重新设计,将单端链路改造成差分链路,差分链路的设计不同于单端链路,滤波器和缓冲链路都需要采用差分模式,滤波器采用差分低通滤波器,信号缓冲器采用双通道运放电路实现,实现了一种全新的全差分链路架构,相比传统的单端链路架构,充分利用了全差分链路在信号处理中的优势,提高了整机的信噪比SNA和抗干扰能力。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

图1为现有技术中基于EEG信号的模拟前端AFE结构示意图;

图2为本发明实施例所提供的一种用于EEG信号采集的模拟前端AFE电路结构示意图;

图3为本发明实施例所提供的差分输出的仪表放大器结构示意图。

具体实施方式

本发明的核心是提供一种用于EEG信号采集的模拟前端 AFE电路,以实现提供全新的全差分链路架构,提高信噪比和抗干扰能力。

为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

图2为本发明实施例所提供的一种用于EEG信号采集的模拟前端AFE电路结构示意图,该模拟前端AFE电路包括:

仪表放大器INA;所述仪表放大器INA为差分输出的仪表放大器;

与仪表放大器INA相连的信号缓冲器BUFFER;

与信号缓冲器BUFFER相连的差分低通滤波器FILTER;

与差分低通滤波器FILTER相连的模数转化器ADC。

进一步的,还包括:

与仪表放大器INA的第一输入端和第二输入端均相连的输入保护器件InputProctection;

与模数转化器ADC相连的数字处理器Digital Processing。

图2中,标记1表示仪表放大器INA,标记2表示信号缓冲器BUFFER,标记3表示差分信号,标记4表示差分低通滤波器FILTER,标记5表示模数转化器ADC。Electrode表示电极,保护器件Input Proctection的个数为多个,依次相连接,第一个Input Proctection的输出端和最后一个Input Proctection的输出端分别与仪表放大器INA的第一输入端和第二输入端相连。

详细的,仪表放大器的第一输出端和第二输出端分别与信号缓冲器的第一输入端和第二输入端相连;信号缓冲器的第一输出端和第二输出端分别与差分低通滤波器的第一输入端和第二输入端相连;差分低通滤波器的第一输出端和第二输出端分别与模数转化器的第一输入端和第二输入端相连。

对比图1和图2两个方案可以看出,差分链路是为了充分利用差分信号抗干扰能力强,高信噪比的特点,所以对传统的EEG AFE单端链路进行了重新设计,将单端链路改造成差分链路。差分链路的设计不同于单端链路,滤波器和缓冲链路都需要采用差分模式,滤波器采用差分低通滤波器,信号缓冲器采用双通道运放电路实现。仪表放大器INA是链路最前置的电路,决定了链路很多关键参数,比如输入噪声,共模抑制比CMRR,偏置电流,失调电压等,而且市面上的仪表放大器INA都是单端输出的,所以如何设计差分输出的仪表放大器就成了最重要的工作。

详细的,仪表放大器输出差分信号,采用两个三运放仪表放大器交叉连接,包括第一三运放仪表放大器、第二三运放仪表放大器以及增益电阻R0。请参考图3,图3为本发明实施例所提供的差分输出的仪表放大器结构示意图,为了使仪表放大器能输出差分信号,采用两个仪表放大器交叉连接,图3中Vout_A和Vout_B输出刚好就是全差分信号。这种新电路使用单个增益电阻提供具有精密增益或衰减的全差分输出。并且优点是链路不用匹配电阻,所以不影响仪表放大器的性能。通过一种新的将两个参考引脚连接在一起的特殊设计方式,可以根据需要调整输出并控制共模电压。图3中,标记7表示第一三运放仪表放大器,标记8表示第二三运放仪表放大器,标记9表示仪表放大器参考,即电路的“地”,零点点位,标记10表示增益电阻,即R0。

其中,第一三运放仪表放大器包括运算放大器A1、A2、A3和电阻R1、R2、R3、R4、R5、R11,第二三运放仪表放大器包括运算放大器A4、A5、A6和电阻R6、R7、R8、R9、R10、R12。

其中,运算放大器A1的同相输入端与运算放大器A2的同相输入端均与所述差分输出的仪表放大器的第一输入端相连,运算放大器A1 的输出端经电阻R1连接A1的反相输入端,运算放大器A2的输出端经R2连接A2的反相输入端;运算放大器A3的反相输入端分两路,一路经R3连接A1的输出端,另一路连接R5的一端,R5的另一端和 A3的输出端均与所述差分输出的仪表放大器的第一输出端相连;运算放大器A3的同相输入端分两路,一路经R4连接A2的输出端,另一路经R11接地。

其中,运算放大器A4的同相输入端与运算放大器A5的同相输入端均与所述差分输出的仪表放大器的第二输入端相连,运算放大器A4 的输出端经电阻R6连接A4的反相输入端,运算放大器A5的输出端经R7连接A5的反相输入端;运算放大器A6的反相输入端分两路,一路经R8连接A4的输出端,另一路经R12接地,运算放大器A6的同相输入端分两路,一路经R9连接A5的输出端,另一路连接R10 的一端,R10的另一端和A6的输出端均与所述差分输出的仪表放大器的第二输出端相连;A5的反相输入端和A1的反相输入端通过增益电阻R0相连。

本发明设计了一种在EEG信号采集的AFE电路中,采用全新的全差分链路来实现EEG微弱信号的采集,提供基于全差分链路的 EEG信号采集的AFE电路,对传统的EEG AFE单端链路进行了重新设计,将单端链路改造成差分链路,差分链路的设计不同于单端链路,滤波器和缓冲链路都需要采用差分模式,滤波器采用差分低通滤波器,缓冲器采用双通道运放实现,信号缓冲器具有双通道运放,实现了一种全新的全差分链路架构,相比传统的单端链路架构,充分利用了全差分链路在信号处理中的优势,提高了整机的信噪比SNA和抗干扰能力。

以上对本发明所提供的一种用于EEG信号采集的模拟前端 AFE电路进行了详细介绍。本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以对本发明进行若干改进和修饰,这些改进和修饰也落入本发明权利要求的保护范围内。

- 一种用于EEG信号采集的模拟前端AFE电路

- 一种应用于心电信号采集的模拟前端电路