半导体器件及其形成方法

文献发布时间:2023-06-19 12:14:58

技术领域

本发明实施例是有关于一种半导体器件及其形成方法。

背景技术

电容器和电阻器是许多半导体集成电路中的标准组件。举例来说,电容器可用于动态随机存取存储(dynamic random-access memory,DRAM)单元中的各种射频(radiofrequency,RF)电路(例如振荡器、相移网络、滤波器、转换器等)中,并且可用作高功率微处理器单元(microprocessor unit,MPU)中的去耦电容器;并且电阻器通常与电容器一起用来控制至少一个上文所提到的电路的其它电子组件的相应电阻。

发明内容

本发明实施例提供一种半导体器件,其包括电阻器以及电容器。电阻器包括薄膜。电容器包括第一板、设置在第一板上方的电容器介电层以及设置在电容器介电层上方的第二板。其中电阻器的薄膜和电容器的第一板包括相同导电材料且在单一图案化工艺中被定义。

本发明实施例提供一种用于形成半导体器件的方法,其包括:在多个内连线结构上方形成第一介电层;在第一介电层上方沉积导电材料;在导电材料上方沉积介电材料;刻蚀导电材料和介电材料以同时定义电阻器的薄膜、电容器的底板以及电容器的电容器介电层;以及在电容器介电层上方形成电容器的顶板。

本发明实施例提供一种半导体器件,其包括:第一板、薄膜、电容器介电层以及第二板。第一板包括第一导电材料。薄膜也包括第一导电材料,薄膜与第一板基本上共面。电容器介电层包括介电材料且设置在第一板上方。第二板包括第二导电材料且设置在电容器介电层上方。其中薄膜构成电阻器的至少一部分,且第一板、电容器介电层以及第二板构成电容器的至少一部分。

附图说明

结合附图阅读以下详细描述会最好地理解本公开的各个方面。应注意,各种特征未必按比例绘制。实际上,为了清楚说明起见,可任意地增大或减小各种特征的尺寸和几何结构。

图1A和图1B示出根据一些实施例的用于形成半导体器件的示例性方法的流程图。

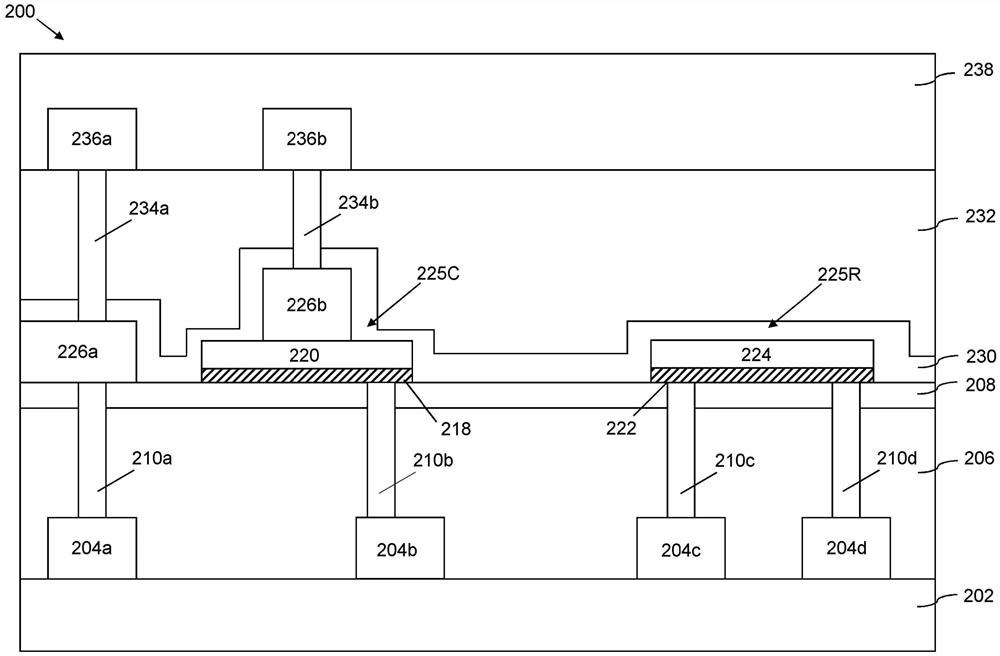

图2A、图2B、图2C、图2D、图2E、图2F、图2G、图2H、图2I、图2J、图2K、图2L以及图2M示出根据一些实施例的通过图1A和图1B的方法所进行的各个制造阶段期间的示例性半导体器件的横截面图。

具体实施方式

以下公开内容描述用于实施主题的不同特征的各种示范性实施例。下文描述组件和布置的具体实例是为了简化本公开。当然,这些组件和布置仅仅是实例且并不意图作为限制。举例来说,在以下描述中,在第二特征上方或第二特征上形成第一特征可包含第一特征与第二特征直接接触地形成的实施例,且还可包含在第一特征与第二特征之间可形成额外特征以使得第一特征与第二特征可以不直接接触的实施例。另外,本公开可在各种实例中重复附图标记和/或字母。这种重复是出于简化和清楚的目的并且本身并不指示所论述的各种实施例和/或配置之间的关系。

此外,为易于描述,本文中可使用如“在……之下”、“在……下方”、“下部”、“在……上方”、“上部”等空间相对术语来描述如图式中所示出的一个元件或特征与另一(些)元件或特征的关系。除图式中所描绘的定向以外,空间相对术语还意图涵盖器件在使用或操作中的不同定向。设备可以其它方式定向(旋转90度或处于其它定向),且本文中所使用的空间相对描述词可同样相应地作出解释。

一般来说,电容器实施为金属-绝缘体-金属(metal-insulator-metal,MIM)结构(在下文中称为“MIM电容器”),所述金属-绝缘体-金属结构包含两个金属板和包夹在两个金属板之间的充当电容器介电层的绝缘体。电阻器实施为金属薄膜电阻器。金属薄膜可表征为具有低电阻温度系数(temperature coefficient of resistivity,TCR)(在下文中称为“低TCR金属电阻器”)。存在各种原因将电容器和电阻器分别实施为MIM电容器和低TCR金属电阻器,而不是其它电容器和电阻器结构(或材料)。举例来说,与由一个半导体电极和金属板组成的金属氧化物半导体(metal-oxide-semiconductor,MOS)电容器相比,在相同面积的情况下,MIM电容器可提供比MOS电容器的电容更大的电容(所述更大电容在各种电路中通常是所需要的)。而且,尽管不是由金属(例如由多晶硅)制成的其它薄膜电阻器也可以存在低TCR,但在与金属薄膜电阻器相比时,这种非金属薄膜电阻器通常存在更紧密(即,更窄)的薄层电阻公差,这会不利地限制这种电阻器的使用。

常规地,当制作与互补金属氧化物半导体(complementary metal-oxide-semiconductor,CMOS)技术兼容的MIM电容器时,需要两种或多于两种图案化工艺(例如光刻工艺,有时将其称为“掩模”)。举例来说,第一掩模用于制作(例如定义)低TCR金属电阻器的金属薄膜,紧接着第二掩模用于刻蚀形成于金属薄膜上的额外层(例如抗反射涂层(anti-reflective coating,ARC)和着陆衬垫层(landing pad layer))。由此,可能增加制造成本/资源/时间。因此,常规的MIM电容器和低TCR金属电阻器以及用以形成此类电容器和电阻器的方法并不完全令人满意。

本公开提供半导体器件的各种实施例,所述半导体器件包含可通过单一图案化工艺制造的至少一个电容器和至少一个薄膜电阻器。在一些实施例中,电容器可以是金属-绝缘体-金属(MIM)电容器,且薄膜电阻器可以是低电阻率温度系数(TCR)的金属电阻器。在一些实施例中,MIM电容器的金属板中的一者(例如底部金属板)和低TCR金属电阻器的金属薄膜同时在单一图案化工艺期间被定义。举例来说,MIM电容器的底部金属板和低TCR金属电阻器的金属薄膜是通过在共同图案化工艺(common patterning process)期间使用同一掩模中所含有的相应的不同图案来图案化(例如刻蚀)同一金属材料而形成的。由此,可在制作包含MIM电容器和低TCR金属电阻器的半导体器件时有利地避免上文所提到的问题。

图1A和图1B共同地示出根据本公开的一个或多个实施例的形成包含至少一个MIM电容器和一个低TCR金属电阻器的半导体器件的方法100的流程图。应注意,方法100仅仅为实例且并不意图限制本公开。因此,应理解,可在图1A到图1B的方法100之前、期间以及之后提供额外操作,且应理解,一些其它操作可仅在本文中进行简要描述。在一些实施例中,方法100的操作可与如分别在图2A、图2B、图2C、图2D、图2E、图2F、图2G、图2H、图2I、图2J、图2K、图2L以及图2M中所绘示的各个制造阶段中的半导体器件的横截面图相关联,这将在下文进一步详细论述。

概括来说,方法100从提供衬底的操作102开始。方法100继续进行到形成多个第一内连线结构的操作104。方法100继续进行到形成第一介电层的操作106。方法100继续进行到沉积富含硅(Si)的介电材料的操作108。方法100继续进行到形成多个第一通孔的操作110。方法100继续进行到沉积导电材料的操作112。方法100继续进行到沉积抗反射涂层材料的操作114。方法100继续进行到同时形成电容器的底板和电容器介电层以及电阻器的薄膜的操作116。方法100继续进行到形成多个第二内连线结构的操作118。方法100继续进行到再次沉积富含Si的介电材料的操作120。方法100继续进行到形成第二介电层的操作122。方法100继续进行到形成多个第二通孔的操作124。方法100继续进行到形成多个第三内连线结构的操作126。方法100继续进行到形成第三介电层的操作128。

如上文所提及,图2A到图2M利用横截面图示出在图1A和图1B的方法100的各个制造阶段中的半导体器件200(包含至少一个电容器和至少一个电阻器)的一部分。半导体器件200可包含于微处理器、存储单元和/或其它集成电路(integrated circuit,IC)中。此外,为了更好地理解本公开的概念起见,简化了图2A到图2M。尽管图式示出半导体器件200,但应了解,IC可包括多个其它器件(如电感器、保险丝、晶体管、线圈等),出于清楚说明的目的,图2A到图2M中并未绘示所述其它器件。

对应于图1A的操作102,图2A是在各个制造阶段中的一个阶段中的包含衬底202的半导体器件200的横截面图。衬底202可为设置在底层处的层间介电(inter-layerdielectric,ILD)层。相应地,可存在设置于衬底202下方或被衬底202上覆的一个或多个器件特征(例如晶体管的栅极、漏极、源极)和/或导电特征(例如导电插塞),出于清楚的目的,并未绘示所述器件特征和/或导电特征。在一些实施例中,可将设置在衬底202上方的层统称为后段工艺(back-end-of-line,BEOL)层。

衬底202包含作为以下材料中的至少一种的材料:氧化硅、低介电常数(低k)材料、其它合适的介电材料或其组合。低k介电材料可包含氟硅玻璃(fluorinated silicaglass,FSG)、磷硅酸盐玻璃(phosphosilicate glass,PSG)、硼磷硅酸盐玻璃(borophosphosilicate glass,BPSG)、掺碳的氧化硅(SiO

对应于图1A的操作104,图2B是在各个制造阶段中的一个阶段中的包含多个第一内连线结构204的半导体器件200的横截面图。举例来说,第一内连线结构204包含第一内连线结构204a、第一内连线结构204b、第一内连线结构204c以及第一内连线结构204d。尽管在图2B(以及以下图式)的所示出实施例中,绘示了四个第一内连线结构204,但应了解,可在衬底202上形成任何数量的第一内连线结构204,同时仍落入本公开的范围内。在一些实施例中,形成在衬底202上的第一内连线结构204a到第一内连线结构204d可彼此横向间隔开。以这种方式,在第一内连线结构204a到第一内连线结构204d上方形成介电材料(这将在下文进行论述)之后,第一内连线结构204a到第一内连线结构204d中的每一者可分别用作器件组件的导电接触件或衬垫。

在图2B的所示出实施例中,第一内连线结构204a到第一内连线结构204d可通过执行以下工艺中的至少一种或多种来形成:使用化学气相沉积(chemical vapordeposition,CVD)、物理气相沉积(physical vapor deposition,PVD)、电子枪(electron-gun)(E枪)和/或其它合适的技术在衬底202上方沉积金属材料(例如Cu、Al或其组合);在金属材料上方形成具有图案的掩模层(例如一个或多个光刻胶层、硬掩模层等),所述图案定义第一内连线结构204a到第一内连线结构204d的相应的期望位置;使用所述图案来刻蚀金属材料;去除掩模层;以及清理残余物。在一些其它实施例中,第一内连线结构204a到第一内连线结构204d可通过执行以下工艺中的至少一种或多种来形成:在衬底202上方沉积介电层(例如金属间介电(inter-metal dielectric,IMD)层的至少一部分);在介电层上方形成具有图案的掩模层(例如一个或多个光刻胶层、硬掩模层等),所述图案定义第一内连线结构204a到第一内连线结构204d的相应的期望位置;使用所述图案来刻蚀介电层以形成至少部分地延伸穿过介电层的凹槽(例如沟槽);在介电层上方沉积金属材料(例如Cu、Al或其组合)以填充凹槽;对所沉积的金属材料执行抛光工艺(例如化学机械抛光(chemical-mechanical polishing,CMP)工艺)以形成嵌入于介电层中的第一内连线结构204a到第一内连线结构204d;以及清理残余物。在介电层中形成嵌入的第一内连线结构204a到第一内连线结构204d有时可称为镶嵌工艺。

对应于图1A的操作106,图2C是在各个制造阶段中的一个阶段中的包含第一介电层206的半导体器件200的横截面图。第一介电层206(其可以是IMD层)上覆于第一内连线结构204a到第一内连线结构204d。在第一内连线结构204a到第一内连线结构204d被形成为BEOL层的最底部内连线结构的实例中,第一内连线结构204有时可称为金属1s(M1s),且包含M1s的第一介电层206有时可称为IMD1层。在图2C的所示出实施例中,第一内连线结构204a到第一内连线结构204d是在形成这种IMD1层之前形成的。应了解,可在形成IMD1层之后例如通过上文所描述的镶嵌工艺来形成第一内连线结构204a到第一内连线结构204d,同时仍落入本公开的范围内。

第一介电层206包含作为以下材料中的至少一种的材料:氧化硅、低介电常数(低k)材料、其它合适的介电材料或其组合。低k介电材料可包含氟硅玻璃(FSG)、磷硅酸盐玻璃(PSG)、硼磷硅酸盐玻璃(BPSG)、掺碳的氧化硅(SiO

对应于图1A的操作108,图2D是在各个制造阶段中的一个阶段中的包含富含Si(Si-rich)的介电材料208的半导体器件200的横截面图。在一些实施例中,富含Si的介电材料208可以是富含Si的氧化物材料。在第一介电层206上方形成这种富含Si的介电材料208可帮助避免不合需要的原子扩散到待形成于富含Si的介电材料208上方的器件组件中。富含Si的介电材料208可包含其中具有许多硅纳米晶体的氧化层。富含Si的介电材料208可经由低压化学气相沉积(low pressure chemical vapor deposition,LPCVD)工艺、等离子体增强式化学气相沉积(plasma enhanced chemical vapor deposition,PECVD)工艺或硅植入工艺使用硅烷(SiH

对应于图1A的操作110,图2E是在各个制造阶段中的一个阶段中的包含多个第一通孔210的半导体器件200的横截面图。举例来说,第一通孔包含通孔210a、通孔210b、通孔210c以及通孔210d。术语“通孔”一般是指竖直内连线结构,所述竖直内连线结构延伸穿过一个或多个介电层(例如IMD层)以电连接沿着所述一个或多个介电层的顶部边界和底部边界设置的器件组件。举例来说,延伸穿过第一介电层206和富含Si的介电材料208的通孔210a可将第一内连线结构204a电连接到另一器件组件(其将在下文进行绘示);延伸穿过第一介电层206和富含Si的介电材料208的通孔210b可将第一内连线结构204b电连接到另一器件组件(其将在下文进行绘示);延伸穿过第一介电层206和富含Si的介电材料208的通孔210c可将第一内连线结构204c电连接到另一器件组件(其将在下文进行绘示);且延伸穿过第一介电层206和富含Si的介电材料208的通孔210d可将第一内连线结构204d电连接到另一器件组件(其将在下文进行绘示)。

通孔210a到通孔210d可通过执行以下工艺中的至少一种或多种来形成:在富含Si的介电材料208(图2D中所绘示)上方形成具有图案的掩模层(例如一个或多个光刻胶层、硬掩模层等),所述图案定义通孔210a到通孔210d的相应的期望位置;使用所述图案来刻蚀富含Si的介电材料208和第一介电层206以形成凹槽(例如介层孔),所述凹槽暴露第一内连线结构204a到第一内连线结构204d的相应顶部边界;沉积金属材料(例如Cu、Al或其组合)以填充凹槽;对所沉积的金属材料执行抛光工艺(例如化学机械抛光(CMP)工艺)以形成延伸穿过富含Si的介电材料208和第一介电层206的通孔210a到通孔210d;以及清理残余物。

对应于图1A的操作112和操作114,图2F是在各个制造阶段中的一个阶段中的包含导电材料212和抗反射涂层(ARC)材料214的半导体器件200的横截面图。如将在下文所论述的,导电材料212可用于定义电阻器(例如低TCR金属电阻器)的薄膜和电容器(MIM电容器)的底板。在一些实施例中,导电材料212与通孔210a到通孔210d直接接触。一些通孔可充当电阻器的内连线结构。与通常在通孔与电阻器之间包含着陆衬垫层(例如TiN层)的现有电阻器相比,由于本公开的通孔与电阻器直接接触,因此可有利地减小电阻器的接触电阻。

导电材料212和抗反射涂层材料214可按顺序形成在富含Si的介电材料208上方。在一些实施例中,导电材料212可包含从以下各材料的至少一种中选出的金属材料:Ta、TaN、Ti、TiN、W、WN、NiCr或SiCr。导电材料212可通过使用化学气相沉积(CVD)、物理气相沉积(PVD)、电子枪(E枪)和/或其它合适的技术在富含Si的介电材料208上方沉积上文所列出的金属材料中的一种或多种来形成。在一些实施例中,ARC材料214可包含从以下各材料的至少一种中选出的介电材料:SiO

对应于图1A的操作116,图2G是在各个制造阶段中的一个阶段中的包含第一板218、第一介电区段220、薄膜222以及第二介电区段224的半导体器件200的横截面图。在一些实施例中,第一板218、第一介电区段220、薄膜222以及第二介电区段224可通过对导电材料212和ARC材料214执行单一图案化工艺215来同时地形成,这将在下文进行论述。由此,第一板218与薄膜222可彼此共面;且第一介电区段220与第二介电区段224可彼此共面。术语“共面”是指两个物体的相应顶部边界或底部边界沿着虚拟边界或实体边界对准。举例来说,第一板218与薄膜222彼此共面,这是由于第一板218的底部边界和薄膜222的底部边界沿着富含Si的介电材料208的中间边界209对准。

图案化工艺215可包含以下工艺中的至少一种或多种:在ARC材料214(图2F中所绘示)上方形成具有图案的掩模层(例如一个或多个光刻胶层、硬掩模层等),所述图案定义第一板218和薄膜222的相应的期望位置;使用图案来刻蚀ARC材料214和导电材料212以同时形成第一板218、第一介电区段220、薄膜222以及第二介电区段224;以及清理残余物。在一些其它实施例中,可使用图案通过以第一刻蚀速率刻蚀ARC材料214来形成第一介电区段220和第二介电区段224。响应于在导电材料212上方形成第一介电区段220和第二介电区段224,可使用相同图案通过以第二刻蚀速率刻蚀导电材料212来形成第一板218和薄膜222。

在一些实施例中,在形成薄膜222后,低TCR金属电阻器225R可形成为具有作为电阻器介电层的第二介电区段224,所述第二介电区段224形成在低TCR金属电阻器225R上方。此外,在形成第一板218和第一介电区段220的同时,可形成MIM电容器225C的一部分。举例来说,第一板218可用作MIM电容器225C的底板或底部电极,且第一介电区段220可用作MIM电容器225C的电容器介电层。因此,第一板218、第一介电区段220以及第二介电区段224在本文中分别称为“底板218”、“电容器介电层220”以及“电阻器介电层224”。在一些实施例中,底板218和薄膜222可承继与导电材料212的厚度基本上类似的厚度,所述厚度在约40埃到约50埃的范围内;且电容器介电层220和电阻器介电层224可承继与ARC材料214的厚度基本上类似的厚度,所述厚度在约100埃到约300埃的范围内。在一些实施例中,底板218和薄膜222的厚度与电容器介电层220和电阻器介电层224的厚度的比率可在约0.2到约0.25的范围内,这是由于可能期望保持低TCR金属电阻器225R的薄膜222的厚度,所述范围还限定了MIM电容器225C的底板218的基本上较小的厚度。这是因为当薄膜222的厚度过大时,低TCR金属电阻器225R的电阻可能变得过小,这在低TCR金属电阻器的应用中通常是不合需要的。

对应于图1A的操作118,图2H是在各个制造阶段中的一个阶段中的包含多个第二内连线结构226的半导体器件200的横截面图。举例来说,第二内连线结构226包含内连线结构226a和内连线结构226b。在一些实施例中,第二内连线结构226中的至少一个(如(例如)第二内连线结构226b)形成在电容器介电层220上方。第二内连线结构226b可具有比底板218和电容器介电层220的宽度(W

举例来说,第二内连线结构226b的宽度W

在图2H的所示出实施例中,第二内连线结构226a到第二内连线结构226b可通过执行以下工艺中的至少一种或多种来形成:使用化学气相沉积(CVD)、物理气相沉积(PVD)、电子枪(E枪)和/或其它合适的技术在富含Si的介电材料208上方沉积金属材料(例如Cu、Al或其组合);在金属材料上方形成具有图案的掩模层(例如一个或多个光刻胶层、硬掩模层等),所述图案定义第二内连线结构226a到第二内连线结构226b的相应的期望位置;使用图案来刻蚀金属材料;去除掩模层;以及清理残余物。在一些其它实施例中,第二内连线结构226a到第二内连线结构226b可通过上文所描述的镶嵌工艺来形成。

在一些实施例中,第二内连线结构226b可用作MIM电容器225C的顶板或顶部电极,在本文中称为“顶部电极226b”。由此,响应于形成顶部电极226b,可完成MIM电容器225C的形成。

对应于图1A的操作120,图2I是在各个制造阶段中的一个阶段中的包含另一富含Si的介电材料230的半导体器件200横截面图。在一些实施例中,富含Si的介电材料230可由与富含Si的介电材料208基本上类似的介电材料形成。如所绘示,可形成富含Si的介电材料230以上覆于第二内连线结构226a、低TCR金属电阻器225R以及MIM电容器225C。由此,在形成富含Si的介电材料230后,低TCR金属电阻器225R和MIM电容器225C可至少部分地被连续的富含Si的介电层包裹,所述连续的富含Si的介电层由富含Si的介电材料208和富含Si的介电材料230组成。

对应于图1B的操作122,图2J是在各个制造阶段中的一个阶段中的包含第二介电层232的半导体器件200的横截面图。第二介电层232(其可以是IMD层)上覆于富含Si的介电材料230。在第一介电层206形成为IMD1层的实例中,第二内连线结构226有时可称为金属2s(M2s),且包含M2s的第二介电层232有时可称为IMD2层。尽管低TCR金属电阻器225R和MIM电容器225C形成在IMD1层(例如第一介电层206)与IMD2层(例如第二介电层232)之间,但应了解,本文中所公开的方法的实施例可使得低TCR金属电阻器和MIM电容器形成在任何后续的IMD层之间。在图2J的所示出实施例中,第二内连线结构204a到第二内连线结构204d是在形成这种IMD2层之前形成的。应了解,可在形成IMD2层之后例如通过上文所描述的镶嵌工艺来形成第二内连线结构226a到第二内连线结构226b,同时仍落入本公开的范围内。

第二介电层232包含作为以下材料中的至少一种的材料:氧化硅、低介电常数(低k)材料、其它合适的介电材料或其组合。低k介电材料可包含氟硅玻璃(FSG)、磷硅酸盐玻璃(PSG)、硼磷硅酸盐玻璃(BPSG)、掺碳的氧化硅(SiO

对应于图1B的操作124,图2K是在各个制造阶段中的一个阶段中的包含多个第二通孔234的半导体器件200的横截面图。举例来说,第二通孔包含通孔234a和234b。延伸穿过第二介电层232和富含Si的介电材料230的通孔234a可将第二内连线结构226a电连接到另一器件组件(其将在下文进行绘示);且延伸穿过第二介电层232和富含Si的介电材料230的通孔234b可将第二内连线结构(顶板)226b电连接到另一器件组件(其将在下文进行绘示)。

通孔234a到通孔234b可通过执行以下工艺中的至少一种或多种来形成:在第二介电层232(图2J中所绘示)上方形成具有图案的掩模层(例如一个或多个光刻胶层、硬掩模层等),所述图案定义通孔234a到通孔234b的相应的期望位置;使用所述图案来刻蚀第二介电层232和富含Si的介电材料230以形成凹槽(例如介层孔),所述凹槽暴露第二内连线结构226a到第二内连线结构226b的相应顶部边界;沉积金属材料(例如Cu、Al或其组合)以填充凹槽;对所沉积的金属材料执行抛光工艺(例如化学机械抛光(CMP)工艺)以形成延伸穿过富含Si的介电材料230和第二介电层232的通孔234a到通孔234b;以及清理残余物。

对应于图1B的操作126,图2L是在各个制造阶段中的一个阶段中的包含多个第三内连线结构236的半导体器件200的横截面图。举例来说,第三内连线结构包含内连线结构236a和内连线结构236b。尽管在图2L(以及以下图式)的所示出实施例中,绘示了两个第三内连线结构236,但应了解,可在第二介电层232上形成任何数量的第三内连线结构236,同时仍落入本公开的范围内。在一些实施例中,形成在第二介电层232上的第三内连线结构236a到第三内连线结构236b可彼此横向间隔开。以这种方式,在第三内连线结构236a到第三内连线结构236b上方形成介电材料(这将在下文进行论述)之后,第三内连线结构236a到第三内连线结构236b中的每一者可分别用作器件组件的导电接触件或衬垫。

在图2L的所示出实施例中,第三内连线结构236a到第三内连线结构236b可通过执行以下工艺中的至少一种或多种来形成:使用化学气相沉积(CVD)、物理气相沉积(PVD)、电子枪(E枪)和/或其它合适的技术在第二介电层232上方沉积金属材料(例如Cu、Al或其组合);在金属材料上方形成具有图案的掩模层(例如一个或多个光刻胶层、硬掩模层等),所述图案定义第三内连线结构236a到第三内连线结构236b的相应的期望位置;使用图案来刻蚀金属材料;去除掩模层;以及清理残余物。在一些其它实施例中,第三内连线结构236a到第三内连线结构236b可通过执行上文所描述的镶嵌工艺来形成。

对应于图1B的操作128,图2M是在各个制造阶段中的一个阶段中的包含第三介电层238的半导体器件200的横截面图。第三介电层238(其可以是IMD层)上覆于第三内连线结构236a到第三内连线结构236b。在第二介电层232被形成为IMD2层的实例中,第三内连线结构236有时可被称为金属3s(M3s),且包含M3s的第三介电层238有时可称为IMD3层。在图2M的所示出实施例中,第三内连线结构236a到第三内连线结构236b是在形成这种IMD3层之前形成的。应了解,可在形成IMD3层之后例如通过上文所描述的镶嵌工艺来形成第三内连线结构236a到第三内连线结构236b,同时仍落入本公开的范围内。

第三介电层238包含作为以下材料中的至少一种的材料:氧化硅、低介电常数(低k)材料、其它合适的介电材料或其组合。低k介电材料可包含氟硅玻璃(FSG)、磷硅酸盐玻璃(PSG)、硼磷硅酸盐玻璃(BPSG)、掺碳的氧化硅(SiO

前文概述若干实施例的特征以使本领域的普通技术人员可更好地理解本公开的各个方面。本领域的技术人员应了解,其可易于使用本公开作为设计或修改用于实施本文中所引入的实施例的相同目的和/或获得相同优势的其它工艺和结构的基础。本领域的技术人员还应认识到,此类等效构造并不脱离本公开的精神和范围,且本领域的技术人员可在不脱离本公开的精神和范围的情况下在本文中进行各种改变、替代以及更改。

在实施例中,一种半导体器件包含电容器和电阻器。电容器包含:第一板;设置在第一板上方的电容器介电层;以及设置在电容器介电层上方的第二板。电阻器包含薄膜。电阻器的薄膜和电容器的第一板包含相同导电材料。电阻器的薄膜和电容器的第一板由单一图案化工艺定义。

在上述半导体器件中,还包括:第一竖直内连线结构,至少部分地延伸穿过设置在所述第一板和所述薄膜下方的第一介电层并且将所述第一板电连接到嵌入于所述第一介电层中的多个内连线结构中的第一内连线结构;以及第二竖直内连线结构,至少部分地延伸穿过设置在所述电容器上方的第二介电层并且将所述第二板电连接到嵌入于第三介电层中的第三内连线结构,所述第三介电层设置在所述第二介电层上方。

在上述半导体器件中,还包括嵌入于所述第二介电层中的第二内连线结构,其中所述第二内连线结构、所述电容器以及所述电阻器在第四介电层中彼此横向地间隔开,所述第四介电层设置在所述第一介电层与所述第二介电层之间。

在上述半导体器件中,所述第二内连线结构、所述电容器以及所述电阻器至少部分地由所述第四介电层包裹。

在上述半导体器件中,还包括:第三竖直内连线结构,至少部分地延伸穿过所述第一介电层并且将所述薄膜的第一端电连接到嵌入于所述第一介电层中的所述多个内连线结构中的第二内连线结构;以及第四竖直内连线结构,至少部分地延伸穿过所述第一介电层并且将所述薄膜的第二端电连接到嵌入于所述第一介电层中的所述多个内连线结构中的第三内连线结构。

在上述半导体器件中,所述第三竖直内连线结构和所述第四竖直内连线结构与所述薄膜直接接触。

在上述半导体器件中,所述电阻器还包括设置在所述薄膜上方的电阻器介电层,其中所述电阻器介电层和所述电容器介电层包括相同介电材料且形成于所述单一图案化工艺中。

在上述半导体器件中,所述介电材料包含抗反射涂层(ARC)材料。

在上述半导体器件中,所述导电材料包含由以下各材料所组成的群组中选出的至少一种材料:钽、氮化钽、钛、氮化钛、钨、氮化钨、镍铬以及硅铬。

在另一实施例中,一种用于形成半导体器件的方法包含:在多个内连线结构上方形成第一介电层。方法包含:在第一介电层上方沉积导电材料。方法包含:在第一金属材料上方沉积介电材料。方法包含:刻蚀导电材料和介电材料以同时定义电阻器的薄膜、电容器的底板以及电容器的电容器介电层。方法包含:在电容器介电层上方形成电容器的顶板。

在上述用于形成半导体器件的方法中,还包括:在沉积所述导电材料之前,形成第一竖直内连线结构、第三竖直内连线结构以及第四竖直内连线结构,所述第一竖直内连线结构、所述第三竖直内连线结构以及所述第四竖直内连线结构中的每一者至少部分地延伸穿过所述第一介电层。

在上述用于形成半导体器件的方法中,其中:所述第一竖直内连线结构被配置成将所述电容器的所述底板电连接到所述多个内连线结构中的第一内连线结构;所述第三竖直内连线结构被配置成将所述电阻器的所述薄膜的第一端电连接到所述多个内连线结构中的第二内连线结构;以及所述第四竖直内连线结构被配置成将所述电阻器的所述薄膜的第二端电连接到所述多个内连线结构中的第三内连线结构。

在上述用于形成半导体器件的方法中,还包括:在形成所述电容器的所述顶板之后,在所述电容器和所述电阻器上方形成第二介电层;以及形成至少部分地延伸穿过所述第二介电层的第二竖直内连线结构。

在上述用于形成半导体器件的方法中,其中所述第二竖直内连线结构被配置成将所述电容器的所述顶板电连接到嵌入于第三介电层中的第三内连线结构,所述第三介电层设置在所述第二介电层上方。

在上述用于形成半导体器件的方法中,其中所述介电材料包含抗反射涂层(ARC)材料。

在上述用于形成半导体器件的方法中,其中所述导电材料包含由以下各材料所组成的群组中选出的至少一种材料:钽、氮化钽、钛、氮化钛、钨、氮化钨、镍铬以及硅铬。

在又一实施例中,一种半导体器件包含第一板,第一板包含导电材料。半导体器件包含与第一板基本上共面的薄膜,薄膜也包含导电材料。半导体器件包含设置在第一板上方的电容器介电层,电容器介电层包含介电材料。半导体器件包含设置在电容器介电层上方的第二板,第二板包含导电材料。薄膜构成电阻器的至少一部分,并且第一板、电容器介电层以及第二板构成电容器的至少一部分。

在上述半导体器件中,其中所述介电材料包含抗反射涂层(ARC)材料。

在上述半导体器件中,其中所述第一导电材料包含由以下各材料所组成的群组中选出的至少一种材料:钽、氮化钽、钛、氮化钛、钨、氮化钨、镍铬以及硅铬。

在上述半导体器件中,还包括:第一竖直内连线结构,至少部分地延伸穿过设置在所述第一板和所述薄膜下方的第一介电层并且将所述第一板电连接到嵌入于所述第一介电层中的所述多个内连线结构中的第一内连线结构;第二竖直内连线结构,至少部分地延伸穿过设置在所述电容器上方的第二介电层并且将所述第二板电连接到嵌入于第三介电层中的第三内连线结构,所述第三介电层设置在所述第二介电层上方;第三竖直内连线结构,至少部分地延伸穿过所述第一介电层,所述第三竖直内连线结构将所述薄膜的第一端电连接到嵌入于所述第一介电层中的所述多个内连线结构中的第二内连线结构;以及第四竖直内连线结构,至少部分地延伸穿过所述第一介电层,所述第四竖直内连线结构将所述薄膜的第二端电连接到嵌入于所述第一介电层中的所述多个内连线结构中的第三内连线结构。

- 半导体膜的形成方法、半导体器件的形成方法和半导体器件

- 栅极结构的形成方法、半导体器件的形成方法以及半导体器件