能够改进ESD保护回路回冲特性的SiC MOS器件

文献发布时间:2023-06-19 12:19:35

技术领域

本发明属于微电子技术领域,特别涉及一种能够改善ESD保护回路回冲特性的SiCMOS器件的结构和制作方法,以降低器件在ESD作用下的触发电压,并且具有高保持电压。

背景技术

SiC具有独特的物理、化学及电学特性,是在高温、高频、大功率及抗辐射等极端应用领域极具发展潜力的半导体材料。ESD是一个很重要的可靠性话题,会在电路中产生过压和过流,导致栅氧化层失效器件的热毁伤。硅中ESD已经研究很多,但是SiC中研究的有限。目前国际上,SKyoung-II提出了一种SiC栅体浮动NMOS器件,具有低导通电阻,低触发电压和高温稳定性。P.Denis研究了ESD HBM应力下的SiC结势垒肖特基二极管,目的是为了强调SiC器件和工艺的限制性。T.P等研究了三种类型晶体管的失效机理,在ESD应力下的MOS器件的工作利用PE以及SPE等方法进行研究。之前报道了15V SiCNMOSESD器件特性来研究ESD的鲁棒性以及保护方式。但是对于SiC功率器件的ESD保护依旧仅有少数文献可查。众所周知,SiC材料大约10倍的临界电场,Ec=2.4MV/cm,而Si是0.25MV/cm,而且pn结内建电势大约3倍Si材料大约3.4V在300K下,所以这个材料特性导致了触发电压和保持电压之间将会有很大的差异,并具有很强的回冲效应,这对优化ESD设计以及保护IC核来说是非常不利的。

发明内容

本发明的目的在于针对上述现有技术的不足,提出一种能够改善ESD保护回路回冲特性的SiC MOS器件,以改善器件在ESD作用下的触发电压并且具有高保持电压。

为实现上述目的,本发明技术方案:

一种能够改进ESD保护回路回冲特性的SiC MOS器件,包括N型的SiC衬底(9),在该SiC衬底(9)的上面设有N型的SiC外延区(8),构成外延片,其特征在于,在该SiC外延区(8)的上面设有相互间隔的源极P型区(6)和漏极P型区(7),在该漏极P型区(7)的上面设有第一nMOSFET(MN1),在该源极P型区(6)的上面设有第二nMOSFET(MN2);

该第一nMOSFET(MN1)包括:设在该源极P型区(6)上面的漏极N+区(1)和N+/P+区(2),在该漏极N+区(1)与N+/P+区(2)之间的上面设有第一栅极氧化层(10),在该漏极N+区(1)和N+/P+区(2)的上面分别设有接触电极;在该第一栅极氧化层(10)的上面设有栅电极;

该第二nMOSFET(MN2)包括:依次排列的源极第一N+区(3)、源极第二N+区(4)和源极P+区(5),在该源极第一N+区(3)与源极第二N+区(4)之间的的上面设有第二栅极氧化层(11),在该源极第一N+区(3)、源极第二N+区(4)和源极P+区(5)的上面分别设有接触电极;在该第二栅极氧化层(11)的上面设有栅电极;

在所述的漏极N+区(1)上面的接触电极上设有漏极引线(D);

所述的第一栅极氧化层(10)上面的栅电极与该源极第一N+区(3)上面的接触电极通过第一互连电极(12)互连,并设有栅极引出线(G);

所述的N+/P+区(2)、源极第二N+区(4)和源极P+区(5)上面的接触电极,以及第二栅极氧化层(11)上面的栅电极均通过第二互连电极(13)互连,并设有源极引出线(S)。

所述的SiC外延区(8)为,浓度5e+15cm-3,该N型的SiC衬底(9)为浓度为5e+18cm-3。

一种所述的能够改进ESD保护回路回冲特性的SiC MOS器件的制作方法,其特征在于,包括以下步骤:

步骤1、外延片表面清洗:对所述的外延片的表面进行标准湿法工艺清洗;

步骤2、源极P型区(6)和漏极P型区(7)的制作:在表面被清洗过的外延片的SiC外延区(8)表面涂光刻胶,刻出源极P型区(6)和漏极P型区(7)的高温离子注入区域,然后进行高温Al离子注入;

步骤3、漏极N+区(1)、源极第一N+区(3)和源极第二N+区(4)的高温氮离子注入,在进行过P-BODY区域高温离子注入之后,刻出N+掺杂源、漏区域,然后进行N+源源、漏区域高温N离子注入;

步骤4、源极P+区(5)和N+/P+区(2)的P型离子注入的形成:在进行N+源、漏区域离子注入之后,刻出P型掺杂接触区域,然后进行P型掺杂高温Al离子注入;

步骤5、表面碳保护膜的形成:在进行了P型离子注入之后,在SiC外延层表面形成碳保护膜;

步骤6、高温离子注入激活:对SiC外延层表面形成碳保护膜的样品进行1600℃高温离子注入退火;

步骤7、表面碳膜的去除:对进行过高温离子注入退火之后的SiC样品进行表面碳膜的去除;

步骤8、第一栅极氧化层(10)和第二栅极氧化层(11)的制备:将去除了表面碳膜的SiC样品进行大面积HF酸清洗,然后进行SiO2栅介质层的生长;

步骤9、漏极N+区(1)、N+/P+区(2)、源极第一N+区(3)、源极第二N+区(4)和源极P+区(5)的接触电极的形成:在进行完栅介质层的生长之后,在样品表面涂剥离胶、光刻胶、刻出欧姆接触孔,进行欧姆接触金属淀积,并剥离形成欧姆接触图形,并进行欧姆接触退火;

步骤10、栅电极的形成:对进行了欧姆接触电极退火的SiC样品进行栅电极的形成;

步骤11、互连电极的形成:对形成栅电极的SiC样品表面涂剥离胶、光刻胶、刻出栅、源接触孔,进行栅、源漏、P型欧姆接触区淀积,并剥离形成栅、源漏、P型欧姆接触区互连图形。

所述步骤A2具体过程如下,

A21将表面被清洗过的N-/N+型SiC外延片样品放入PECVD当中,大面积淀积SiO2层,厚度为60nm;

A22在淀积了SiO2的SiC样品表面涂光刻胶,并光刻出P-BODY区域;然后在HF酸溶液当中将未经光刻胶保护的SiO2层清洗掉,露出P-BODY区高温离子注入区域;

A23将露出源极P型区(6)和漏极P型区(7)区域的SiC样品放入高温离子注入机,在400℃下分四次进行高温磷离子注入,形成P-BODY区域,深度大概0.7μm,浓度5×1018cm-3;

A24对进行了高温离子注入后的样品在HF溶液中清洗,去除表面的SiO2阻挡层;

所述步骤A3具体过程如下:

A31将去除了表面SiO2阻挡层的SiC样品放入PECVD当中,大面积淀积SiO2层,厚度为60nm;

A32在淀积了SiO2的SiC样品表面涂光刻胶、甩胶,光刻出源注入区;然后在HF酸溶液当中将未经光刻胶保护的SiO2层清洗掉,露出源注入区;

A33将露出源极P型区(6)和漏极P型区(7)的SiC样品放入高温离子注入机,在400℃下分四次进行高温氮离子注入,形成结深0.3μm,浓度大概3×1019cm-3;

A34对进行了高温离子注入后的样品在HF酸溶液当中清洗,去除表面的SiO2阻挡层。

所述步骤A4具体过程如下:

A41将去除了表面SiO2阻挡层的SiC样品放入PECVD当中,大面积淀积SiO2层,厚度为60nm;

A42在淀积了SiO2的SiC样品表面涂光刻胶、甩胶,光刻出P型注入区;然后在HF酸溶液当中将未经光刻胶保护的SiO2层清洗掉,露出P型注入区;

A43将露出源极P+区(5)和漏极P型区(2)的SiC样品放入高温离子注入机,在400℃下分四次进行高温铝离子注入,形成浓度约1.5×1019cm-3,深度大约0.2μm;

A44对进行了高温离子注入后的样品在HF酸溶液当中清洗,去除表面的SiO2阻挡层。

所述步骤A5具体过程如下:

A51在除掉表面SiO2阻挡层的SiC外延片样品表面涂光刻胶、甩胶,放入烤箱中90℃下前烘1分钟;

A52将进行前烘过的SiC样品放入高温退火炉中,在600℃下保持30分钟,进行碳化;

A53对进行过碳化的SiC样品进行降温。

所述步骤A6具体过程如下:

A61将SiC表面进行了碳化的样品置于高温退火炉中,将有碳膜的一面朝下,抽真空到10-7Torr,充Ar气,逐步升温到1600℃,在1600℃停留30分钟,进行高温离子注入退火;

A62对加载样品的高温离子注入退火炉进行降温到常温,将SiC样品从高温退火炉中拿出。

所述步骤A7具体过程如下:

A71将进行了高温离子注入退火的SiC样品放入RIE反应室中,带有碳膜的一面朝上,关上反应室阀门,打开N2阀门到1/4,通N260秒,然后关掉氮气阀门;

A72对带有碳膜的SiC样品进行了60秒的N2冲洗之后,打开油泵,等到油泵的声音变大并且变得稳定的时候完全打开油泵阀门,等到泵稳定20-30分钟;

A73打开氧气阀门,直到腔室里面的压力达到9-12mT;

A74打开冷却系统,调节氧气流量到47sccm;

A75打开射频网络适配器,计时90分钟去掉SiC样品表面的碳膜;

A76关掉网络适配器电源,关掉O2;

A77将系统降压到常压,关掉冷却系统,对RIE反应室里面充N2直到反应室门可以打开,取出样品。

所述步骤A8具体过程如下:

A81对去除了表面碳膜的SiC样品进行HF酸清洗;

A82将进行进行过HF酸清洗的SiC样品放入高温氧化炉中,1180℃时,通入纯氧气,在干氧条件下氧化SiC外延片正面10小时,生成厚度为50nm的SiO2氧化膜;

A83对生长的氧化膜进行氮化:对生长的SiO2氧化膜进行1175℃下2小时的NO退火;

A84利用栅介质版形成栅介质图形。

所述步骤A9采用20nm/240nm的Ni/Au两种金属做源漏以及P型欧姆接触金属;其具体过程如下:

A91在进行了栅介质层制作的SiC样品正面涂剥离胶、光刻胶,光刻,清洗光刻胶、剥离胶,露出有效源漏以及P型欧姆接触区域;

A92 SiC样品放入电子束蒸发室中;

A93在SiC样品正面蒸发厚度为20nm/240nm的Ni/Au作为源漏以及P型欧姆接触金属;

A94剥离形成源漏以及P型欧姆接触金属图形;

A95将进行了源漏以及P型欧姆接触电极的SiC样品置于退火炉中在950℃下合金退火30分钟。

所述步骤A10采用20nm/240nm的Ni/Au两种金属做栅金属;其具体过程如下:

A101在进行了源漏以及P型欧姆接触的SiC样品表面涂剥离胶,甩胶;

A102在涂完剥离胶的SiC样品表面涂光刻胶,甩胶,利用栅版光刻出栅金属区域;

A103在刻出栅接触孔的SiC样品表面上蒸发厚度为20nm/240nm的Ni/Au作为栅接触金属;

A104利用剥离方法形成栅图形。

所述步骤A11,互连电极的制作采用Ti/Au两种金属,厚度分别为50nm/200nm;包括以下步骤:

A111在制作完栅金属的SiC样品表面涂剥离胶、涂光刻胶;

A112利用互连光刻版刻出栅和源、漏以及P型欧姆接触电极互连窗口;

A113在刻出栅、源、漏以及P型欧姆接触孔的SiC样品表面上蒸发厚度为30nm/200nm的Ti/Au作为栅、源、漏以及P型欧姆接触金属;

A114利用剥离方法形成栅、源、漏以及P型欧姆接触互连图形。

本发明与现有技术相比具有如下优点:本发明通过对传统的SiC MOS结构进行改进,降低了器件在ESD作用下的触发电压,并且具有高保持电压,能够有效地抑制器件的ESD保护回路回冲效应。

附图说明

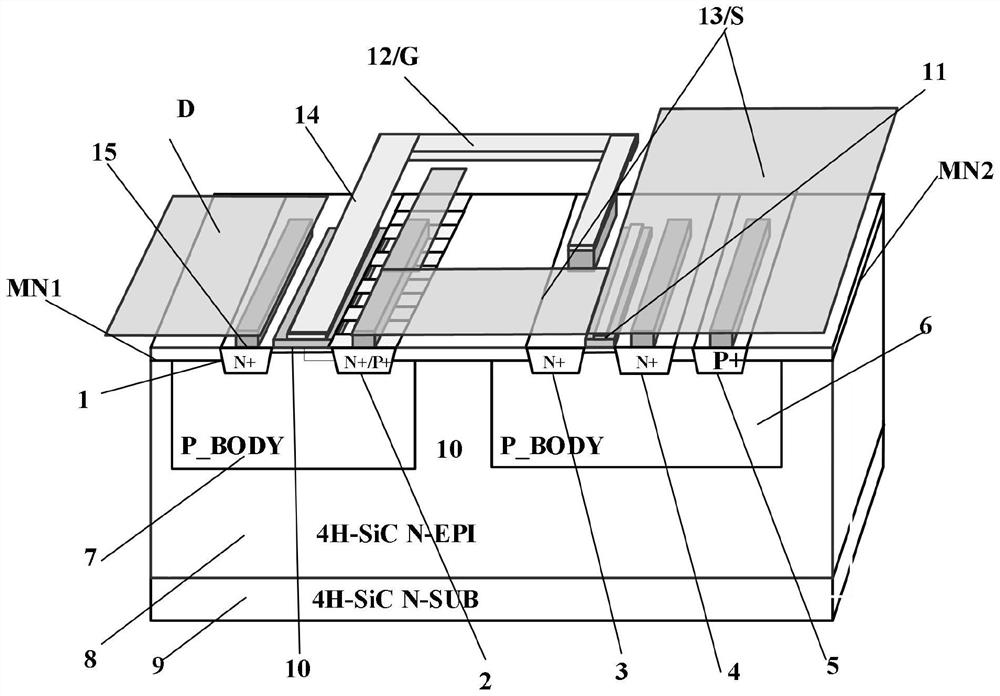

图1是本发明器件的结构示意图;

图2是本发明器件的等效电路示意图;

图3是本发明器件的制备方法流程示意图,图中的(a)-(g)图表示各步骤加工的内容(器件截面图),其中:(a)图为清洗后的外延片;(b)图为注入源极P型区6和漏极P型区7后;(c)图为完成漏极N

附图标记说明:1、漏极N

具体实施方式

参见图1,本发明一种能够改善ESD保护回冲效应的高压SiC功率MOS器件,包括N型的SiC衬底9,在该SiC衬底9的上面设有N型的SiC外延区8,构成外延片,其特征在于,在该SiC外延区8的上面设有相互间隔的源极P型区6和漏极P型区7,在该漏极P型区7的上面设有第一nMOSFET,标记为MN1(位于图1中的左半部),在该源极P型区6的上面设有第二nMOSFET,标记为MN2(位于图1中的右半部)。

标记为MN1的第一nMOSFET包括:设在该源极P型区6上面的漏极N

标记为MN2的第二nMOSFETMN2包括:依次排列的源极第一N

在所述的漏极N

所述的第一栅极氧化层10上面的栅电极14与该源极第一N

所述的N

本发明上述器件的等效电路如图2所示,其中MN1的漏极N

在没有静电释放的正常工作模式下,MN1不工作,因为反向结的高电位,但是当出现ESD(静电释放)时,漏极N

MN1的N

参见图3,本发明上述器件的制备方法的第一实施例工艺流程如下(以下工艺的各个步骤的具体操作都属于常规技术):

步骤1,采用标准清洗方法RCA对4H-SiC P-/N+型外延片样品进行表面清洗(参见图3中的a图)。

步骤2,在外延片样品正面的外延面制作源极P型区(6)和漏极P型区(7)高温离子注入区域(参见b图)。

(2a)将清洗好的外延片放入P-BODY反应室,在300℃下表面淀积SiO

(2b)在淀积了SiO

(2c)甩光刻胶,然后对甩过胶的外延片在90℃下进行前烘;前烘时间为1min;

(2d)利用N-WELL注入光刻版对前烘之后的外延片样品曝光;

(2e)在正性显影液中显影,溶液温度为20℃,显影时间为20s;

(2f)将显影之后的外延片在超纯水进行坚膜,水温度为20℃,坚膜时间为20s;

(2g)在等离子体去胶机中去掉曝光过的光刻胶,露出有效N-WELL区域;

(2h)然后在HF酸溶液中将露出的SiO

(2i)将清洗掉SiO

(2j)对注入过后的样品在体积比为1:10的HF(浓度为40%)与水的混合溶液漂洗,去除表面的SiO

步骤3,在源极P型区(6)和漏极P型区(7)上面进行源漏区离子注入漏极N

(3a)将清洗好的外延片放入PECVD反应室,在300℃下表面淀积SiO

(3b)在淀积了SiO

(3c)甩光刻胶,然后对甩过胶的外延片在90℃下进行前烘;前烘时间为1min;

(3d)利用N-source注入光刻版对前烘之后的外延片样品曝光;

(3e)在正性显影液中显影,溶液温度为20℃,显影时间为20s;

(3f)将显影之后的外延片在超纯水进行坚膜,水温度为20℃,坚膜时间为20s;

(3g)在等离子体去胶机中去掉曝光过的光刻胶,露出有效N-source区域;

(3h)然后在HF酸溶液中将露出的SiO

(3i)将清洗掉源漏区SiO

(3j)对注入过后的样品在体积比为1:10的HF(浓度为40%)与水的混合溶液漂洗,去除表面的SiO

步骤4,在源极P型区(6)和漏极P型区(7)上面进行P型区离子注入N

(4a)将清洗好的外延片放入PECVD反应室,在300℃下表面淀积SiO

(4b)在淀积了SiO

(4c)甩光刻胶,然后对甩过胶的外延片在90℃下进行前烘;前烘时间为1min;

(4d)利用P型注入光刻版对前烘之后的外延片样品曝光;

(4e)在正性显影液中显影,溶液温度为20℃,显影时间为20s;

(4f)将显影之后的外延片在超纯水进行坚膜,水温度为20℃,坚膜时间为20s;

(4g)在等离子体去胶机中去掉曝光过的光刻胶,露出有效P+区域;

(4h)然后在HF酸溶液中将露出的SiO

(4i)将清洗掉源漏区SiO

(4j)对注入过后的样品在体积比为1:10的HF(浓度为40%)与水的混合溶液漂洗,去除表面的SiO

下面步骤5-9为制备第一栅氧化层10和第二栅极氧化层11的工艺流程(参见图3中的d图):

步骤5,在N-/N+外延片样品正面制作高温离子注入退火碳保护膜:

(5a)在除掉表面SiO

(5b)甩胶,放入烤箱中90℃下前烘1分钟;

(5c)将进行前烘过的SiC样品放入高温退火炉中,碳面朝上;

(5d)抽真空2小时,压力达到4~5E-7Torr;

(5e)充Ar气,设置输出压为12psi;

(5f)打开风扇;

(5g)首先将电源功率调至10%,然后按照5%/2min速度调到30%的电源功率,然后细调电源功率按照2%/2min的功率调至温度上升到600℃,在600℃下保持30分钟;

(5h)关掉升温电源功率调节旋钮;

(5i)拿出带有碳膜的SiC样品;

步骤6,高温离子注入退火;

(6a)将带有碳保护膜的SiC样品放入高温退火炉中,带有碳面的一面朝下;

(6b)抽真空,压力达到4~5E-7Torr;

(6c)充Ar气,设置输出压为12psi;

(6d)打开风扇;

(6e)首先将电源功率调至60%,然后按照1%/10s速度调至温度上升到1600℃,在1600℃下保持30分钟;

(6f)关掉升温电源功率调节旋钮;

(6i)拿出带有碳膜的经过高温离子注入退火之后的SiC样品;

步骤7,去掉N-/N+SiC外延样品正面的碳保护膜:

(7a)给RIE腔体中充N

(7b)将样品放置在正中,带有碳膜的一面朝上,用镊子压紧,关上反应室门然后拧紧阀门;

(7c)开始通O

(7d)打开射频网络适配器,调节功率设置为18±3W;

(7e)开始计时90分钟去除SiC样品表面的碳膜;

(7f)关掉射频网络适配器,关掉O

(7g)充N

(7h)将去除掉表面碳膜的SiC样品进行RCA清洗;

步骤8,第一栅氧化层10和第二栅极氧化层11的制备:

(8a)将去进行完RCA清洗的SiC样品放入高温氧化炉中,在温度为750℃的N

(8b)按3℃/min速率对恒温区进行升温;

(8c)当温度升至1150℃时通入氧气,氧气流量为0.5l/min,在纯干氧条件下氧化外延片表面10小时,在外延片正面生成厚度为50nm的SiO

(8d)关掉O

(8e)按照3℃/min速率对恒温区进行升温;

(8f)当温度升到1175℃时,打开NO,流量577sccm,时间2小时;

(8h)关掉NO气体,将炉温降到900℃;

(8i)关掉Ar气体,取出样品;

(8j)在进行了大面积生长的SiO

(8k)利用栅氧光刻版对前烘之后的外延片曝光;

(8l)在正性显影液中显影,溶液温度为20℃,显影时间为85s;

(8m)将显影之后的外延片在超纯水进行坚膜,水温度为20℃,坚膜时间为85s;

(8n)在等离子体去胶机中去掉曝光过的光刻胶,然后将去过光刻胶的外延片在丙酮中浸泡5小时以及利用丙酮超声1分钟,露出有效栅区域。

步骤9,制作漏极N

(9a)在进行高温退火后的外延片表面涂剥离胶,甩胶;

(9b)在涂过剥离胶的外延片表面涂光刻胶、甩胶,然后对甩过胶的外延片样品在80℃下进行前烘;前烘时间为10~15min;

(9c)利用欧姆接触光刻版对前烘之后的外延片曝光;

(9d)在正性显影液中显影,溶液温度为20℃,显影时间为85s;

(9e)将显影之后的外延片在超纯水进行坚膜,水温度为20℃,坚膜时间为85s;

(9f)在等离子体去胶机中去掉曝光过的光刻胶,露出有效源漏区域以及P型欧姆接触区域;

(9g)将去过光刻胶的外延片在丙酮中浸泡5小时以及利用丙酮超声处理1分钟,然后再丙酮、酒精清洗各一次,去掉源漏欧姆接触区域以及P型欧姆接触区域的剥离胶;露出有效接触区域;

(9h)将去过胶的外延片放入电子束蒸发室中,大面积蒸发三种金属Al/Ni/Au做欧姆接触电极,其厚度分别为150nm、50nm和70nm,然后利用剥离的方法实现欧姆接触图形;

(9i)最后将做完源电极的外延片置于退火炉中在950℃下进行合金退火30分钟;

步骤10,栅电极14的制备(参见图3中的f图):

(10a)在进行完欧姆电极退火的SiC样品正面涂剥离胶、光刻胶,甩胶,然后对甩过胶的外延片在80℃下进行前烘;前烘时间为10~15min;

(10b)利用栅电极光刻板刻出栅图形;

(10c)在正性显影液中显影,溶液温度为20℃,显影时间为85s;

(10d)将显影之后的外延片在超纯水进行坚膜,水温度为20℃,坚膜时间为85s;

(10e)在等离子体去胶机中去掉曝光过的光刻胶,然后利用去离子水进行清洗;

(10f)然后将去过光刻胶的外延片在丙酮中浸泡5小时以及利用丙酮超声1分钟,然后再丙酮、酒精清洗各一次,去掉栅电极区域的剥离胶;露出有效接触区域;

(10g)对去过光刻胶和剥离胶的外延片放入电子束蒸发室当中,大面积蒸发Ti/Au,厚度为50nm/200nm;

(10m)通过剥离方法形成最后的栅电极14。

步骤11,第一互连电极12和第二互连电极13的制作互连电极14(参见图3中的g图):

(11a)对淀积了栅金属的外延片表面涂剥离胶,甩胶;涂光刻胶,甩胶,然后对甩过胶的外延片在80℃下进行前烘;前烘时间为10~15min;

(11b)利用互连接触版对前烘之后的外延片曝光;

(11c)在正性显影液中显影,溶液温度为20℃,显影时间为85s;

(11d)将显影之后的外延片在超纯水进行坚膜,水温度为20℃,坚膜时间为85s;

(11e)在等离子体去胶机中去掉曝光过的光刻胶,然后将去过光刻胶的外延片在丙酮中浸泡5小时以及利用丙酮超声1分钟,然后再丙酮、酒精清洗各一次,去掉接触互连区域的剥离胶;露出有效接触区域;

(11f)对去过光刻胶和剥离胶的外延片放入电子束蒸发室当中,大面积蒸发Ti/Au,厚度为50nm/200nm;

(11g)通过剥离方法形成最后的电极接触。

制备方法的实施例2:

该实施例在实施案例1中步骤6之后,步骤7之前增加了牺牲氧化一道工序,能够更有效的减小高温离子注入退火所带来的界面损伤,有效的改善界面平整度。而其余的步骤将与案例1完全相同。

该实施例的牺牲氧化实现步骤如下:

(1)将进行过高温退火的外延片放入高温氧化炉中,在1200℃时在纯干氧条件下氧化外延片表面30min,在外延片正面生成厚度为20nm的SiO

(2)将生长过SiO2氧化膜的外延片放入HF酸当中,将表面的氧化层清洗掉。

- 能够改进ESD保护回路回冲特性的SiC MOS器件

- 提高SOI NMOS器件ESD保护能力的方法以及SOI NMOS器件