一种写辅助装置及其工作方法、存储器

文献发布时间:2023-06-19 12:21:13

技术领域

本发明涉及计算机技术领域,尤其涉及一种写辅助装置及其工作方法、存储器。

背景技术

低功耗在当今的集成电路设计中是一个重要的课题,对于芯片而言,其动态功耗和静态功耗都和电源电压直接相关,因此降低电源电压是实现低功耗的有效途径之一。

然而,对于很多电路而言,电源电压降低虽然可以降低功耗,但也可能给电路性能带来不利影响。例如,对SRAM(Static Random Access Memory,静态随机存储器)存储电路而言,SRAM存储电路中设置有SRAM存储单元阵列。SRAM存储单元阵列由若干个存储单元bitcell组成,每个存储单元可以用于存储一位二进制数0或1。电源电压降低虽然可以节省bitcell的工作功耗,也会导致写操作时用于传输写入数据的晶体管(也称传输管)的栅源压差变小,写入电流变小,因此会拉长写入时间,甚至可能出现写失败的情况。为此,写辅助技术应运而生。

写辅助技术具体可以通过多种方式实现,例如,可以在写操作期间,对存储单元的位选线加一个负向冲击电压,使传输管的源极电压降低,以便提高该传输管的栅源压差,加大写入电流,提高写成功率;或者,可以在写操作期间,对存储单元的字选线加一个正向冲击电压,使传输管的栅压提高,进而提高该传输管的栅源压差,加大写入电流,提高写成功率。然而,对于大量出产的芯片,工艺偏差时常在不同芯片间发生,具体哪个芯片的哪个电压需要一个多大的冲击电压需要经过大量的测试,并将测试结果烧入该芯片的熔断阵列。这样,一方面导致冲击电压的确定过程非常低效,另一方面,由于在熔断阵列中烧入了固定值,写辅助开启的冲击电压无法适配不同的电压场景。

针对写辅助开启冲击电压效率低下且适配性差的问题,相关技术中尚无有效的解决方案。

发明内容

有鉴于此,本发明实施例提供一种写辅助装置及其工作方法、存储器,能够有效提高写辅助效率和适配性。

第一方面,本发明实施例提供写辅助装置,包括:电压识别部,一端连接被监测电压,另一端连接辅助电压生成部,用于从预设的电压区间集合中识别所述被监测电压所处的电压区间,得到目标电压区间;所述辅助电压生成部,一端连接所述电压识别部,另一端连接写数据传输部,用于根据所述目标电压区间产生辅助电压,并将所述辅助电压施加于所述写数据传输部,以辅助所述写数据传输部将待写入的数据写入目标位置。

可选的,所述电压识别部包括:分压模块,输入端与所述被监测电压相连,输出端包括至少一个输出通道,各所述输出通道的输出电压分别为所述被监测电压的一个分压,各所述输出通道的输出电压互不相等;识别模块,与所述分压模块相连,用于根据所述分压模块的各输出通道的输出电压与预设阈值的关系,从预设的所述电压区间集合中识别所述被监测电压所处的电压区间,得到目标电压区间。

可选的,所述识别模块,具体用于:按照预设顺序,将所述分压模块的各输出通道的输出电压与所述预设阈值相比较;在确定其中一个输出通道的输出电压大于所述预设阈值的情况下,放弃后续输出通道的比较操作。

可选的,所述预设顺序为所述输出电压由低到高的顺序。

可选的,所述辅助电压生成部包括:译码模块,与所述电压识别部相连,用于根据所述电压识别部识别出的所述目标电压区间,选通产生所述辅助电压所需的辅助通道;产生模块,与所述译码模块相连,用于通过所述译码模块选通的所述辅助通道产生所述辅助电压。

可选的,所述译码模块,具体用于:为各所述目标电压区间及其对应的所述辅助通道分别建立编码-选通对应关系,其中,每个所述目标电压区间对应选通0个、一个或多个所述辅助通道;根据所述编码-选通对应关系,选通产生所述辅助电压所需的辅助通道。

可选的,所述译码模块包括第一逻辑门;所述产生模块包括至少一个所述辅助通道,每个所述辅助通道包括第二逻辑门及与所述第二逻辑门串联连接的电容。

可选的,所述写辅助装置还包括:锁存部,所述锁存部一端与所述电压识别部相连,另一端与所述辅助电压生成部相连,用于将所述电压识别部识别出的所述目标电压区间锁存。

可选的,所述电压识别部,还用于根据识别出的所述目标电压区间,关闭自身的直流通路。

可选的,所述被监测电压包括以下至少一项:第一电源电压,所述第一电源电压用于为所述写数据传输部提供写入选通信号;第一节点电压,所述第一节点电压在预设条件下具有预设逻辑电平。

可选的,所述辅助电压包括冲击电压。

可选的,所述目标位置包括以下至少一项:目标寄存器、目标存储单元、目标端口。

可选的,所述写数据传输部设置有写入选通端、数据输入端、数据输出端;所述数据输出端与所述目标位置相连;所述辅助电压生成部与所述数据输入端相连,用于根据所述电压识别部识别出的所述目标电压区间产生第一辅助电压,并将所述第一辅助电压施加于所述数据输入端,其中,所述第一辅助电压与所述写入选通端的电压极性相反;和/或,所述辅助电压生成部与所述写入选通端相连,用于根据所述电压识别部识别出的所述目标电压区间产生第二辅助电压,并将所述第二辅助电压施加于所述写入选通端,其中,所述第二辅助电压与所述写入选通端的电压极性相同。

第二方面,本发明的实施例还提供一种写辅助装置的工作方法,包括:从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间;根据所述目标电压区间产生辅助电压,以在所述辅助电压的辅助下,将待写入的数据写入目标位置。

可选的,所述从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间包括:将所述被监测电压分压后通过至少一个输出通道,各所述输出通道的输出电压分别为所述被监测电压的一个分压,各所述输出通道的输出电压互不相等;根据各所述输出通道的输出电压与预设阈值的关系,从预设的所述电压区间集合中识别所述被监测电压所处的电压区间,得到目标电压区间。

可选的,所述根据各所述输出通道的输出电压与预设阈值的关系,从预设的所述电压区间集合中识别所述被监测电压所处的电压区间包括:按照预设顺序,将各所述输出通道的输出电压与所述预设阈值相比较;在确定其中一个输出通道的输出电压大于所述预设阈值的情况下,放弃后续输出通道的比较操作。

可选的,所述根据所述目标电压区间产生辅助电压包括:根据所述目标电压区间,选通产生所述辅助电压所需的辅助通道;通过所述辅助通道产生所述辅助电压。

可选的,所述根据所述目标电压区间,选通产生所述辅助电压所需的辅助通道包括:为各所述目标电压区间及其对应的所述辅助通道分别建立编码-选通对应关系,其中,每个所述目标电压区间对应选通0个、一个或多个所述辅助通道;根据所述编码-选通对应关系,选通产生所述辅助电压所需的辅助通道。

可选的,所述从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间之后,所述根据所述目标电压区间产生辅助电压之前,所述方法还包括:将所述目标电压区间锁存。

可选的,所述从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间之后,所述方法还包括:根据识别出的所述目标电压区间,停止对所述被监测电压的识别。

第三方面,本发明的实施例还提供一种存储器,所述存储器中设置有本发明的实施例提供的任一种写辅助装置。

本发明的实施例提供的写辅助装置及其工作方法、存储器,能够对被监测电压进行实时监测,从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间,根据目标电压区间产生辅助电压,并将辅助电压施加于写数据传输部,以辅助写数据传输部将待写入的数据写入目标位置。这样,就能够根据电路实际工作中被监测电压的实际大小,及时确定在进行数据写操作时写辅助装置所需要的合适的辅助电压,并及时产生该辅助电压,既无需复杂的测试操作,又可以适用于各种场景,从而有效提高了写辅助效率和适配性。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

图1为本发明的实施例中位线负压写辅助技术的电路原理图;

图2为本发明的实施例中与图1所示的电路对应的写数据时序图;

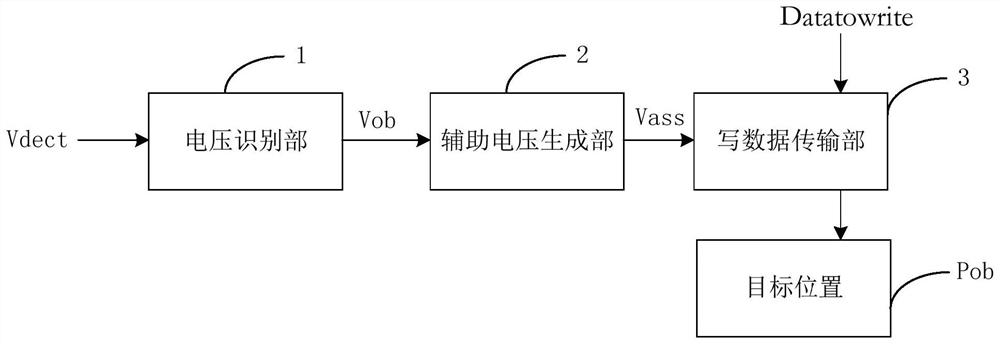

图3为本发明的实施例提供的写辅助装置的一种结构示意图;

图4为本发明的实施例提供的写辅助装置的另一种结构示意图;

图5为本发明的实施例提供的写辅助装置的又一种结构示意图;

图6为本发明的实施例提供的写辅助装置中第一逻辑门的一种结构示意图;

图7为本发明的实施例提供的写辅助装置中第二逻辑门的一种结构示意图;

图8为本发明的实施例提供的写辅助装置的又另一种结构示意图;

图9为本发明的实施例提供的写辅助装置中锁存部的一种结构示意图;

图10为本发明的实施例提供的写辅助装置中辅助电压生成部与写数据传输部的一种连接关系示意图;

图11为本发明的实施例提供的写辅助装置的一种详细结构示意图;

图12为图11所示实施例中写辅助装置的电路行为的一种状态转换示意图;

图13为图12的电压识别状态中分压电路的一种结构示意图;

图14为图12的电压识别状态中进行电压区间识别的一种电路结构示意图;

图15为图12的电压识别状态中进行电压区间识别的另一种电路结构示意图;

图16为图12的电压识别状态中进行电压区间识别的又一种电路结构示意图;

图17为图12的电压识别状态中进行电压区间识别的又另一种电路结构示意图;

图18为图12的电压识别状态中进行电压区间识别的再一种电路结构示意图;

图19为图12的直流通路关断处理状态的一种电路结构示意图;

图20为本发明的实施例提供的写辅助装置的工作方法的一种流程图。

具体实施方式

下面结合附图对本发明实施例进行详细描述。

应当明确,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

如背景技术所言,对于很多电路而言,电源电压降低虽然可以降低功耗,但也可能给电路性能带来不利影响,因此产生了写辅助技术。针对相关技术中,写辅助开启冲击电压效率低下且适配性差的问题,本发明的实施例提供了一种写辅助装置。

为了便于理解本发明,首先以SRAM存储器为例,对写操作进行简要说明。

图1是位线负压(NegBL)写辅助技术的简要原理图,其中,每个SRAM bitcell包括两个输入输出背靠背相连的反相器,每个反相器的PMOS(P-Metal Oxide Semi-conductorField Effect Transistor,P型金属氧化物场效应晶体管)称为bitcell的上拉管MPU,反相器的NMOS称为bitcell的下拉管MPD,由字线(WL)门控的NMOS称为传输管PGT、PGC。图中,字线WL后的“@”符号,表示该字线WL的电压域是VDDM(该字线WL的供电电压源为VDDM)。C1/C2/C3所在的电路部分为写辅助电路。写辅助电路的电源电压可以使用与WL相同的电源,也可以使用与WL不同的电源。C1/C2/C3为电容元件,WA1/WA2/WA3可以通过不同的逻辑值的组合,产生不同的cc1/cc2/cc3信号,并分别在cc1/cc2/cc3的下降沿产生负压冲击。C1/C2/C3电容可以由MOS电容或者线间耦合电容组成。NMOS PDWR为负压下拉管,由信号WA_ENX门控,在不需要产生负压时开启,使BL最低下拉电压为0v,在需要产生负压时关闭,浮空VSS_WA,并使用电容两端压差不突变的特性,使用电容C1/C2/C3对VSS_WA进行负压冲击。

下面对写辅助的操作过程进行简要介绍。当需要对bitcell进行写入操作时,可以考虑写入与存储相同值和不同值的情形。当写入相同值时,假设bitcell存0,准备写入0(即WrData=0),BLT此时已经准备好待写入的值0,BLC为1,待传输管PGT、PGC开启,位线BLT上预先准备的逻辑0与bitcell QT逻辑0相同,BLC预先准备好的1与bitcell QC逻辑1相同,bitcell的值不会被改写,传输管PGT、PGC关闭后,bitcell进入保持状态;当写入值与bitcell存储值相反时,如bitcell存1,此时准备写入0(即WrData=0),BLT已经准备好逻辑0,BLC为1,待传输管PGT、PGC打开,位线BLT通过传输管PGT将QT的1下拉到0,开启对面的上拉管PUC,将QC上拉到逻辑1,待后续传输管PGT、PGC关闭后,bitcell进入保持状态,位线BLT、BLC通过PCHT、PCHC重新充电回逻辑1,至此完成写操作。

由于写入值与bitcell存储值相反,当bitcell的电源电压VDDM下降后,如果不开启写辅助则有可能出现写入不成功的情况。具体而言,如图2所示,当bitcell的电源电压VDDM下降后,字线WL电压下降,第一个写周期,写辅助不开启。在信号变为1开启WPGT和WPGC后BLT下降为0电平,等待WL变为1,WL变为1开启PGT和PGC,QT被逐渐下拉到某个中间电压,但是这个中间电压没有达到bitcell翻转的电压值,对面的QC点没有上升到1,写失败。第二个写周期,和第一个写周期一样向QT写0,当负压使能WA_ENX变0之前,可以看到QT、QC的情况下和第一个周期相同,无法写入,直到WA_ENX变为0,将BLT、BLC写驱动反相器X1、X2的地信号VSS_WA浮空,同时信号cc1/cc2/cc3通过WA1/WA2/WA3的组合由1变为0,由电容两端电压不突变特性,电容C1/C2/C3接VSS_WA一端由初始的0耦合出负压,这个负压传输到BLT上,加大了bitcell的传输管PGT的栅源压差,加大了传输管的电流,拉低QT点的电压,达到bitcell的翻转点,写入成功。

WA[3:1]为负压冲击开启的控制端口。集成电路中,电路工作情况复杂多变,具体到某个电路是否需要开启负压冲击,以及需要开启多大的负压冲击,可以由WA[3:1]来确定。当WA[3:1]都为1时,不产生负压;WA[3:1]中有一位为0其他为1时,开启对应的电容产生的负压;WA[3:1]中有两位为0,一位为1时,开启两个电容组合的负压;WA[3:1]三位全为0时,开启三个电容组合产生最大幅度的负压。

为了有效提高写辅助电压开启的效率,并使写辅助电压能够适配多种应用场景,本发明的实施例提供一种写辅助装置,能够根据电路实际工作情况,及时确定在进行数据写操作时写辅助装置所需要的合适的辅助电压,并及时产生该辅助电压,既无需复杂的测试操作,又可以适用于各种场景,从而有效提高了写辅助效率和适配性。下面通过具体实施例进行详细说明。需要说明的是,本发明的实施例提供的写辅助装置,不仅可以应用于SRAM中,也适用于其他需要进行写操作的场景。

如图3所示,本发明的实施例提供一种写辅助装置,该装置可以包括:

电压识别部1,一端连接被监测电压Vdect,另一端连接辅助电压生成部2,用于从预设的电压区间集合中识别被监测电压Vdect所处的电压区间,得到目标电压区间Vob;

辅助电压生成部2,一端连接电压识别部1,另一端连接写数据传输部3,用于根据目标电压区间Vob产生辅助电压Vass,并将辅助电压Vass施加于写数据传输部3,以辅助写数据传输部3将待写入的数据Datatowrite写入目标位置Pob。

本发明的实施例提供的写辅助装置,电压识别部1能够对被监测电压Vdect进行实时监测,从预设的电压区间集合中识别被监测电压Vdect所处的电压区间,得到目标电压区间Vob,辅助电压生成部2能够根据目标电压区间Vob产生辅助电压Vass,并将辅助电压Vass施加于写数据传输部3,以辅助写数据传输部3将待写入的数据写入目标位置Pob。这样,就能够根据电路实际工作中被监测电压Vdect的实际大小,及时确定在进行数据写操作时写辅助装置所需要的合适的辅助电压Vass,并及时产生该辅助电压Vass,既无需复杂的测试操作,又可以适用于各种场景,从而有效提高了写辅助效率和适配性。

可选的,被监测电压Vdect可以是任何能够直接或间接反映写操作困难程度的电压信号。例如,在本发明的一个实施例中,被监测电压Vdect可以包括以下一项或多项:第一电源电压,所述第一电源电压用于为所述写数据传输部提供写入选通信号;第一节点电压,所述第一节点电压在预设条件下具有预设逻辑电平。

可以理解的,芯片在不同PVT(process voltage temperature,工艺电压温度角)下,性能表现会有所差异,因此,不同芯片的性能表现可能不同。同时,芯片的运行速度以及对资源的消耗情况,也会因为芯片所承载的业务和计算量的分布而变化。因此,给芯片供电的各电源的输出电压也可能会产生变化。例如,当芯片执行运算多而复杂时,各运算模块消耗的电压消耗就会比较大,导致供电电源的输出电压偏低。而如果该电源恰恰是为写数据传输部3提供写入选通信号的电源的话,则可能会提高写操作的难度。

进一步地,在供电电源的输出电压偏低的同时,也可能会影响电路中一些比较特殊的节点的节点电压,当对电源输出电压监测不方便的时候,也可以监测这些特殊节点的电压,只要预先获知该节点在预设条件下的电压波动范围即可。例如,某节点电压在预设条件下具有预设逻辑电平1,对应的电压本应为1.1V以上,但由于电源电压的变化,导致该节点在该预设条件下的电压为0.9V,因此可以间接反映写操作可能处于困难状态。这样,本发明的实施例提供的写辅助装置,通过对这些电源电压和节点电压的监测,可以及时、准确地掌握写操作是否困难,以及困难程度,从而为其提供适当的写辅助,以使写操作顺利完成。

电压识别部1的具体结构可以多种多样。具体而言,如图4所示,在本发明的一个实施例中,电压识别部1具体可以包括:

分压模块11,输入端与被监测电压Vdect相连,输出端包括至少一个输出通道,各输出通道的输出电压Vn,分别为被监测电压Vdect的一个分压,其中n为正整数,各所述输出通道的输出电压Vn(例如V1、V2……)互不相等;

识别模块12,与分压模块11相连,用于根据分压模块11的各输出通道的输出电压Vn与预设阈值的关系,从预设的电压区间集合中识别被监测电压Vdect所处的电压区间,得到目标电压区间Vob。

其中,各输出通道的输出电压Vn可以通过多种方式对被监测电压Vdect进行分压。例如,在本发明的一个实施例中,可以在被监测电压Vdect与地信号之间串联多个分压元件,并从不同的分压元件之间分别取输出电压。可选的,分压元件可以为以下一种或多种:电阻、二极管、三极管、MOS管等。例如,在本发明的一个实施例中,被监测电压Vdect与地信号之间串联了3个阻值相等的电阻,则可以形成两个输出通道,其输出电压分别为Vdect/3,2Vdect/3。这样可以通过扩散电阻跟踪工艺参数变化的器件,以分压的形式实现跟踪工艺、电压、温度等。

可选的,在本发明的另一个实施例中,也可以在被监测电压Vdect与地信号之间并行设置多个不同的通路,其中,每个通路对应一个输出通道和一个输出电压。通过分压模块11对被监测电压Vdect进行分压后,可以得到各输出通道的不同输出电压,将这些不同的输出电压分别与预设阈值比较,即可确定被监测电压Vdect所处的电压区间,得到目标电压区间Vob。其中,预设阈值在电路上可以通过多种方式实现,例如MOS管开启电压、二极管导通电压、通过各种钳位措施、稳压措施等实现的预设阈值。

举例而言,在本发明的一个实施例中,预设的电压区间集合为{[0.3,0.6),[0.6V,0.8V),[0.8V,1.2V),[1.2V,1.5V]},输出电压V1=Vdect-Vdelta,V2=Vdect-2Vdelta,V3=Vdect-3Vdelta,其中,0<3delta 可选的,在将各输出通道的输出电压与预设阈值比较时,可以按照各种顺序进行比较,例如同时比较、按照随机顺序比较等,只要能够识别出被监测电压Vdect所处的目标电压区间即可。为了提高对被监测电压Vdect的识别效率,在本发明的一个实施例中,识别模块12具体可以用于:按照预设顺序,将所述分压模块的各输出通道的输出电压与所述预设阈值相比较;在确定其中一个输出通道的输出电压大于所述预设阈值的情况下,放弃后续输出通道的比较操作。可选的,该预设顺序可以为输出电压由低到高的顺序。这样,首先将各输出通道中最低的一个输出电压与预设阈值相比较,如果该最低的一个输出电压都大于预设阈值,则说明被监测电压Vdect足够大,无需开启写辅助。如果该最低的一个输出电压小于预设阈值,次低的一个输出电压大于预设阈值,则说明被监测电压Vdect较大,可以开启较小的写辅助电压。以此类推。 上述实施例中,是对被监测电压Vdect进行不同的分压后,将各分压分别与同一个预设阈值比较,从而确定被监测电压Vdect所处的目标电压区间,但本发明的实施例不限于此,在本发明的其他实施例中,也可以直接将被监测电压Vdect与不同的预设阈值相比较,从而得出被监测电压Vdect所处的目标电压区间。例如,分别将Vdect与预设阈值1.2V、0.8V、0.6V相比较,若Vdect大于1.2V,则可以确定Vdect的目标电压区间为[1.2,1.5]。 进一步地,识别出被监测电压Vdect所在被目标电压区间Vob后,可以通过辅助电压生成部2产生该目标电压区间对应的辅助电压。可选的,辅助电压可以包括冲击电压或者其他稳定电压、暂态电压,例如恒压源提供的电压、振荡器提供的电压等,只要能够减轻写操作的困难程度即可。 辅助电压施加在写数据传输部3后,可以辅助写数据传输部3将待写入的数据写入目标位置Pob。其中,目标位置Pob可以包括任何能够接收写操作的位置,例如,在本发明的一个实施例中,目标位置Pob可以包括以下一项或多项:目标寄存器、目标存储单元、目标端口。 具体而言,如图5所示,在本发明的一个实施例中辅助电压生成部2可以包括: 译码模块21,与电压识别部1相连,用于根据电压识别部1识别出的目标电压区间,选通产生辅助电压所需的辅助通道Wa; 产生模块22,与译码模块21相连,用于通过译码模块21选通的辅助通道产生辅助电压。 本实施例中,由于电压识别部1识别出的被监测电压Vdect可能处于多个目标电压区间中的任一个,为了使辅助电压生成部2在Vdect处于这些目标电压区间的情况下,都能产生对应所需的辅助电压,译码模块21可以用于:为各所述目标电压区间及其对应的所述辅助通道分别建立编码-选通对应关系,其中,每个所述目标电压区间可以对应选通0个、一个或多个辅助通道;根据所述编码-选通对应关系,选通产生所述辅助电压所需的辅助通道。 可选的,在本发明的一个实施例中,被监测电压Vdect处于哪个目标电压区间可以通过一组信号编码表示。例如,在电压识别部1将被监测电压Vdect的多个分压分别与预设阈值比较时,不同的比较结果可以对应不同的输出电平,各分压的比较结果可以形成一个组合逻辑,即编码。例如,输出通道ch3的输出电压V3与预设阈值Vth的比较结果为V3 译码模块21能够将上述编码译出,选通对应的辅助通道WA。对于每一组编码,可以根据目标电压区间的不同,开启不同的辅助通道或辅助通道的组合,产生不同的辅助电压。例如,在本发明的一个实施例中,编码0101可以开启辅助通道WA1,产生辅助电压VA,编码0111可以开启辅助通道WA2,产生辅助电压2VA,编码1001可以开启辅助通道WA2和WA3,产生辅助电压4VA等。 具体实施中,译码模块21可以包括第一逻辑门。可选的,第一逻辑门可以包括一系列的与门、非门、或门及其组合。第一逻辑门的输入信号可以是电压识别部1识别出的、被监测电压Vdect所处的目标电压区间对应的信号组合,例如V3OK V2OK V1OK,第一逻辑门的输出信号可以是被选通的辅助通道,例如辅助通道WA2被选通,则第一逻辑门的输出信号中辅助通道WA2对应的信号为“1”,其他未被选通的辅助通道对应的信号为“0”。示例性的,本发明的实施例中,第一逻辑门的一种结构可以如图6所示。 产生模块22可以通过被译码模块21选通的辅助通道产生对应的辅助电压。具体而言,产生模块22可以包括一个或多个辅助通道,其中每个辅助通道可以包括第二逻辑门及与所述第二逻辑门串联连接的电容。可选的,第二逻辑门的输入端可以连接译码模块21,根据译码模块21的输出确定各辅助通道是否被选通。第二逻辑门的输出端可以连接对应的电容,该电容可以被充电,并在该电容两极板间形成电压差。 根据该辅助通道是否需要产生辅助电压的不同,第二逻辑门可以输出高电平或低电平,并通过在高电平、低电平之间的切换,使电容的一个极板电位突然升高或降低。由于电容两极板间的电压不能突变,该电容的另一个极板的电位也会随之突然升高或降低,从而产生冲击电压,该冲击电压可以作为辅助电压被施加到写数据传输部3,以便使待写入的数据通过写数据传输部3顺利写入目标位置。随着对电容进行较缓慢的充电或放电,冲击电压逐渐消失,电路达到新的平衡。示例性的,本发明的实施例中,第二逻辑门和电容的一种结构可以如图7所示。 为了进一步降低功耗,在本发明的一个实施例中,如图8所示,写辅助装置还可以包括锁存部4,锁存部4一端与电压识别部1相连,另一端与辅助电压生成部2相连,用于将电压识别部1识别出的目标电压区间锁存。这样,在识别出被监测电压所处的目标电压区间后,辅助电压生成部2就可以依靠锁存部4锁存的目标电压区间进行译码和产生辅助电压,电压识别部1就无需进行持续的电压识别操作。可选的,在本发明的一个实施例中,可以采用定时器等手段,定期触发电压识别部1来进行一次电压识别操作。 需要说明的是,锁存部4是按照电路的功能来划分的,在电路的具体结构上,锁存部4既可以独立于电压识别部1和辅助电压生成部2,也可以设置在电压识别部1中,或者设置在辅助电压生成部2中。本发明的实施例对此不做限定。 进一步地,在本发明的一个实施例中,在电压识别部1未进行电压识别操作时,电压识别部1还可以用于根据识别出的目标电压区间,关闭自身的直流通路,以进一步降低功耗。例如,可以将电压识别部1的输出信号经过适当的组合逻辑反馈至电压识别部1的输入端,以关闭电压识别部1的直流通路。为了保证电压识别部1的直流通路关闭时,锁存部4已经将识别出的目标电压区间成功锁存,在本发明的一个实施例中,可以将电压识别部1的输出信号通过若干个延时器后,再反馈至电压识别部1的输入端。在本发明的另一个实施例中,也可以将锁存部4的输出信号引入电压识别部1的输入端,以与电压识别部1的输出信号相配合,关闭电压识别部1的直流通路。示例性的,本发明的一个实施例中,锁存部4的一种结构可以如图9所示。 前述实施例详细介绍了写辅助装置的结构和工作原理,其中,辅助电压生成部2能够根据电压识别部1对被监测电压的识别,产生对应的辅助电压,将该辅助电压施加在写数据传输部3上,即可辅助写数据传输部3将待写入的数据写入目标位置。具体而言,在本发明的一个实施例中,写数据传输部3可以包括多个不同的端口,具体可以包括多种辅助电压施加方式。 如图10所示,在本发明的一个实施例中,写数据传输部3设置有写入选通端31、数据输入端32、数据输出端33;数据输出端33与所述目标位置Pob相连。例如,写数据传输部3可以为MOS管,其中,写入选通端31可以为MOS管的栅极、数据输入端32可以为MOS管的源极、数据输出端33可以为MOS管的漏极。当然,写数据传输部3也可以为其他具有数据传输功能的结构,例如三极管、门电路等。 辅助电压生成部2可以与数据输入端32相连,用于根据电压识别部1识别出的目标电压区间,产生第一辅助电压Vass1,并将第一辅助电压Vass1施加于数据输入端32,其中,第一辅助电压Vass1与写入选通端31的电压极性相反。这样,辅助电压的加入,可以使写数据传输部3的写入选通端31与数据输入端32之间的电压差增大,从而可以增大写入电流,提高写入成功率。 可选的,在本发明的另一个实施例中,辅助电压生成部2可以与写入选通端31相连,用于根据电压识别部1识别出的目标电压区间,产生第二辅助电压Vass2,并将第二辅助电压Vass2施加于写入选通端31,其中,第二辅助电压Vass2与写入选通端31的电压极性相同。这样,辅助电压的加入,也可以使写数据传输部3的写入选通端31与数据输入端32之间的电压差增大,从而可以增大写入电流,提高写入成功率。 当然,在本发明的其他实施例中,也可以将第一辅助电压Vass1施加于数据输入端32,将第二辅助电压Vass2施加于写入选通端31,以产生叠加的写辅助效果。 此外,本发明的实施例提供写辅助装置也可以进一步加入时序逻辑,以帮助时序逻辑实现合适的信号建立保持时间。 下面通过具体的实施例来对本发明的实施例提供的写辅助装置进行详细说明。 图11是本发明的实施例提供的写辅助装置的一种结构示意图。该写辅助装置可以包括:电压识别模块61,用于检测跟踪字选线WL所在电压域(即为字选线WL供电的电源)的电压,识别其所属的目标电压区间;锁存模块62,用于将电压识别模块61识别出的目标电压区间锁存;译码模块63,用于根据该目标电压区间对应的编码,选通需要开启的辅助通道;辅助电压生成模块64,用于根据根据选通的辅助通道产生辅助电压;直流通路关闭模块65,用于在识别完目标电压区间后,关闭电压识别模块61中的直流通路,节省功耗。 图12是本发明的实施例提供的写辅助装置的电路行为的状态转换图。该电路行为主要可以包括:电源就绪状态(状态s0)、电压识别状态(状态s1)、译码状态(状态s2)、直流通路关闭状态(状态s3)、不开辅助电压状态(状态s4)、开启辅助电压状态(s5)。 电源就绪状态(状态s0)。当系统电源就绪时,该状态转到电压识别s1;否则继续停留在本状态等待电源就绪。 电压识别状态(状态s1)。当电路接收到系统提供的电源就绪信号开始分析电压的信号后,电路进入电压识别状态,电路识别出芯片当前工作环境的实际电压,并生成电压对应的等级码,电压识别码表达当前电压处在哪一个区间,电压识别码经过下游编码产生唯一的负压编码。举例而言,在本发明的一个实施例中,可以将电压分成4个电压区间,那么会产生4个电压识别码(V1,V2,V3,V4),对应4档电压区间。电压识别码经过s2编码可以生成4位负压编程码(V4OK和WA[3:1]),其中,第4位V4OK用以识别是否需要开启负压,剩余三位用于调整负压开启幅度。在本发明的另一个实施例中,电压识别码是5位,则负压编码是5位(V5OK,WA[4:1]),其中,V5OK用来表示开启或关闭负压产生。电压区间数量可以根据不同的设计需求进行不同的实现。 图13是状态s1电压识别的分压电路结构示意图,图14-图18是进行电压区间识别的电路结构示意图。结合图13-图18,本发明的实施例中,分压电路可以有多种方法,这里采用一种以二极管接法的MOS管来完成电压的区间分级。下面以V1和V4的两个电路讲解电压区间的识别。 先看V4产生电路。V4电路需要的使能信号来自于Disable、PwrOK和Start。下面从关闭及开启两种状态讲解V4产生电路: 1)当Disable=1(表示关闭检测)或者Start=0(表示不进行检测)或者PwrOK=0(表示电源没有就绪)时,Ready_v4=1,NMOS NTL4开启,V4=0; 2)当Disable=0(表示在检测中),Start和PwrOK=1(表示电源就绪并开启检测)时,Ready_v4=0,V4电压状态为VDDM减去4个PMOS的阈值电压Vtp。假设VDDM=1.0v,Vtp=200mv(毫伏),V4=1-0.2*4=200mv。NMOS NDIO4的用处是给PMOS串联通路提供一个极弱的下拉电流,保证V4不会因为NTL4关闭而被漏电上拉到接近VDDM电平。 V1的电压产生和V4原理相同,当进行电压识别时,V1的电压为VDDM-1*Vtp。V1、V2、V3的电路和V4的不同点在于直流通路的关闭信号来源。V4由Disable来关闭直流通路,V3则由V4OK来关闭直流通路,此时认为一旦V4OK=1,就表示电源水平在V4区间,就不在需要V3及以下区间判断。如果V4OK=0,那就再判断V3,看电压水平是否在V3区间,如果在,则关闭V2及以下区间的识别电路,如果不在,则继续判断V2...以此类推,直到判断V1。 V2直流通路的关闭信号是V34OK,V34OK表示V3OK=1或者V4OK=1,意味着此时电压区间落在较高压或者高压区间,V2所代表的的中等电压区间不需要继续进行判断,可以关闭其直流通路。V1直流通路的关闭信号是V234OK,表示此时电压已经被判断出在中等电压或较高压或高压区间,V1所代表的的低压区间的判断就不需要了,可以关闭其直流通路。 得到电压区间集合(V1、V2、V3、V4)后,可以对电源电压VDDM所在电压区间进行识别。具体而言,在电源就绪的情况下,start=0将所有VOK信号置为0。等待start=1到来,进行电压分析;Start=1后,先从V4开始分析,如果V4的电压水平能够开启NMOS NE4,信号eval4就会被下拉为0,V4OK变为1。V4OK和系统时钟或者电路其他信号可以生成负压使能信号WA_ENX,供图11中的辅助电压生成模块64使用。当V4OK=1时,关断V3及以下的分析路径,并将V3OK、V2OK、V1OK置位为0,Vmin置位为0。如果V4的电压水平不足以开启NE4,V4OK会被PFB4锁存在0,并开启V3分析路径。PFB4和NFB4共同将每个分析路径中的eval值锁存住,防止电压识别模块关闭后,电压识别结果的丢失。 V3、V2、V1路径原理和V4路径相似。只是多了置位MOS和传输门。如V3路径中多了PMOS PRST3,这个MOS用在当V4OK=1时,将V3OK置为0。传输门则在V4OK=1时关断V3去开启NE3的路径。置位MOS和传输门的加入在设计意义上表示当电压区间被识别到V4时(最高位的区间),较低的区间就不需要再做判断和分析。NEN3则是在传输门关断时,将NE3的输入置位0,防止浮空网络的产生。 电压识别时,可以先从最高位的电压识别码算起,如果最高位的电压识别码有效,则无需开启辅助电路产生负压冲击;如果最高电压识别码无效,则可以依次降低识别等级,直到某一位电压识别码被认为有效。例如,可以依次对V4、V3、V2、V1做分析,直到出现V4OK=1或V3OK=1或V2OK=1或V1OK=1,依次代表当前电压在最高压、次高压、中等电压、低电压区间,对应的负压幅度为不开启、微弱幅度、中等幅度、最大幅度。如果上述VOK都没有从初态0变为1。那么Vmin会变为1。表示当前电源识别处在最低电压区间。需要开启最大的的负压幅度。 具体而言,图14所示,如果最高位的电压识别码V4有效(即V4较高,足以开启NE4),则V4OK=1,V3、V2、V1、Vmin停止判断,V4OK=1表示当前电压处在无需开启负压区间。如果V4无效(即V4较低,不足以开启NE4),则V4OK=0,需要开启辅助电路产生负压,此时需要继续判断V3是否有效。参见图15,如果V3有效,则V3OK=1,说明电压处在较高的区间,开启的负压仅需要一个小的幅度;如果V3无效,则V3OK=0,则需要继续判断V2,具体可以参见图16。以此类推,直到判断到V1。参见图17,如果V1有效,则开启更大的负压幅度,如果V1无效,则如图18所示,Vmin=1。Vmin表示开启所有的耦合电容进行负压冲击。 译码状态(状态s2)。可以对识别状态产生的编码进行译码,得到产生辅助电压所需的辅助通道。例如,可以对V3OK、V2OK、V1OK和Vmin的组合编码,进行译码,得到辅助通道的选通信号WA3、WA2、WA1。V4OK可以产生负压使能信号WA_ENX(参见图14)。 直流通路关闭状态(状态s3)。在s1生成的负压编码一段时间后,可以认为电压识别已经稳定有效,电压识别码已经可以反应真实工作电压。此时,可以对s1输出的V4OK、V3OK...Vmin的进行逻辑运算,运算结果返回s1,通过Disable信号关闭电压识别模块中存在的直流通路,以降低识别电路的功耗。而已经识别出的电压识别码会被电路中的锁存单元锁存住,继续对后续负压编程起到作用。图19是关断直流通路的电路实施例。如图19所示,当字线WL电源电压被识别出时,就可以认为电压识别模块可以关断了,以达到节省功耗的目的。电路中加入延时单元是让电压识别和分析充分,保证每条分析路径都已经锁存了相应的电压分析值后,再关断电压识别模块的直流通路。 不开辅助电压状态(状态s4)。根据VOK产生负压编码的电路有NR1/NR2/NR3/IN1/XD1/XD2/XD3组成。当V4OK=1时,WA[3:1]=111,在时钟使能下WA_ENX=1,不产生负压。 开启辅助电压状态(s5)。当V4OK=0,WA[3:1]分别由上述第4条产生对应幅度负压。如果V3OK=1,则WA[3:1]=011;如果V2OK=1,则WA[3:1]=001;如果V1OK=1,则WA[3:1]=000;如果V3OK/V2OK/V1OK都为0,Vmin=1,此时WA[3:1]=000,和V1OK一样,开启最大幅度负压。 第二方面,相应的,本发明的实施例还提供了一种写辅助装置的工作方法,能够有效提高写辅助的操作效率和适配性。 如图20所示,本发明的实施例提供的写辅助装置的工作方法,可以包括: S71、从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间; S72、根据所述目标电压区间产生辅助电压,以在所述辅助电压的辅助下,将待写入的数据写入目标位置。 本发明的实施例提供的写辅助装置的工作方法,从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间,根据所述目标电压区间产生辅助电压,以在所述辅助电压的辅助下,将待写入的数据写入目标位置。这样,就能够根据电路实际工作中被监测电压的实际大小,及时确定在进行数据写操作时写辅助装置所需要的合适的辅助电压,并及时产生该辅助电压,既无需复杂的测试操作,又可以适用于各种场景,从而有效提高了写辅助效率和适配性。 可选的,步骤S71中从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间具体可以包括: 将所述被监测电压分压后通过至少一个输出通道,各所述输出通道的输出电压分别为所述被监测电压的一个分压,各所述输出通道的输出电压互不相等; 根据各所述输出通道的输出电压与预设阈值的关系,从预设的所述电压区间集合中识别所述被监测电压所处的电压区间,得到目标电压区间。 可选的,根据各所述输出通道的输出电压与预设阈值的关系,从预设的所述电压区间集合中识别所述被监测电压所处的电压区间可以包括: 按照预设顺序,将各所述输出通道的输出电压与所述预设阈值相比较; 在确定其中一个输出通道的输出电压大于所述预设阈值的情况下,放弃后续输出通道的比较操作。 可选的,步骤S72中,根据所述目标电压区间产生辅助电压可以包括: 根据所述目标电压区间,选通产生所述辅助电压所需的辅助通道; 通过所述辅助通道产生所述辅助电压。 可选的,所述根据所述目标电压区间,选通产生所述辅助电压所需的辅助通道可以包括: 为各所述目标电压区间及其对应的所述辅助通道分别建立编码-选通对应关系,其中,每个所述目标电压区间对应选通0个、一个或多个所述辅助通道; 根据所述编码-选通对应关系,选通产生所述辅助电压所需的辅助通道。 可选的,从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间之后,根据所述目标电压区间产生辅助电压之前,本发明的实施例提供的写辅助装置的工作方法还可以包括:将所述目标电压区间锁存。 可选的,从预设的电压区间集合中识别被监测电压所处的电压区间,得到目标电压区间之后,本发明的实施例提供的写辅助装置的工作方法还可以包括:根据识别出的所述目标电压区间,停止对所述被监测电压的识别。 本发明的实施例提供的写辅助装置的工作方法,基于前述实施例提供的任一种写辅助装置,其具体的电路结构及工作过程已经在前文进行了说明,此处不再赘述。 第三方面,相应的,本发明的实施例还提供了一种存储器,所述存储器中设置有本发明的前述实施例提供的任一种写辅助装置,因此也能产生相应的有益技术效果,具体可以参见前述实施例,此处不再赘述。 需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。 本说明书中的各个实施例均采用相关的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。 尤其,对于装置实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。 为了描述的方便,描述以上装置是以功能分为各种单元/模块分别描述。当然,在实施本发明时可以把各单元/模块的功能在同一个或多个软件和/或硬件中实现。 本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于一计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中,所述的存储介质可为磁碟、光盘、只读存储记忆体(Read-Only Memory,ROM)或随机存储记忆体(Random AccessMemory,RAM)等。 以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

- 一种写辅助装置及其工作方法、存储器

- 一种用于静态随机存储器的写辅助电路以及写辅助方法