存储器件及其制备方法

文献发布时间:2023-06-19 13:29:16

技术领域

本申请涉及存储技术领域,具体涉及一种存储器件及其制备方法。

背景技术

如图1所示,传统技术方案中的存储器件包括多个存储块510、多个局部位线译码器520、多个字线译码器540、多个全局位线译码器530以及其他电路550,其中,存储块510的构造区域、局部位线译码器520的构造区域、字线译码器540的构造区域、全局位线译码器530的构造区域以及其他电路550的构造区域互不重叠,例如,局部位线译码器520的构造区域位于对应的存储块510的构造区域的一侧,字线译码器540位于对应的局部位线译码器520的构造区域和/或存储块510的构造区域的另一侧,全局位线译码器530的构造区域位于对应的局部位线译码器520的构造区域与全局位线译码器530的构造区域之间。

具体地,如图2所示,沿某一方向,存储块510和局部位线译码器520依次交替排列,末尾一个局部位线译码器520之后依次为全局位线译码器530、多个感测放大器551,位于每个存储块510的另一侧则设置有一字线译码器540,每个局部位线译码器520与对应的存储块510和全局位线译码器530电性连接,全局位线译码器530的输出端与对应的多个感测放大器551电性连接。同样的,图2中的各存储块510的构造区域、各局部位线译码器520的构造区域、全局位线译码器530的构造区域、各感测放大器551的构造区域以及各字线译码器540的构造区域也互不重叠。

如此,上述传统技术方案中的存储器件需要占用较大空间以集成上述的各部分结构,不利于最小化存储器件的尺寸。

需要注意的是,上述关于背景技术的介绍仅仅是为了便于清楚、完整地理解本申请的技术方案。因此,不能仅仅由于其出现在本申请的背景技术中,而认为上述所涉及到的技术方案为本领域所属技术人员所公知。

发明内容

本申请提供一种存储器件及其制备方法,以缓解存储器件需要占用较大面积的技术问题。

第一方面,本申请提供一种存储器件,其包括第一芯片和第二芯片,第一芯片包括第一存储阵列和第二存储阵列,第一存储阵列包括至少一个第一存储块,第一存储块包括多条沿第一方向延伸的第一字线和多条沿第二方向延伸的第一位线,第二存储阵列包括至少一个第二存储块,第二存储块包括多条沿第一方向延伸的第二字线和多条沿第二方向延伸的第二位线;第二芯片沿第三方向叠置于第一芯片的上方,第二芯片包括逻辑控制电路,逻辑控制电路包括第一全局位线子译码器和第二全局位线子译码器,第一全局位线子译码器与至少一个第一存储块电性连接,第二全局位线子译码器与至少一个第二存储块电性连接,第二芯片具有一第一存储块的第一俯视投影区域和一第二存储块的第二俯视投影区域;第一全局位线子译码器形成的第一全局位线子译码器区块位于第一俯视投影区域内,第二全局位线子译码器形成的第二全局位线子译码器区块位于第二俯视投影区域内;且在第二方向上,第二俯视投影区域、第一俯视投影区域依次排列。

在其中一些实施方式中,在第二方向上,第一俯视投影区域、第二俯视投影区域相邻。

在其中一些实施方式中,在第一方向上,第一全局位线子译码器区块的长度小于或者等于第一俯视投影区域的长度;在第一方向上,第二全局位线子译码器区块的长度小于或者等于第二俯视投影区域的长度。

在其中一些实施方式中,在第一方向上,第一俯视投影区域的长度等于第二俯视投影区域的长度。

在其中一些实施方式中,逻辑控制电路还包括感应放大电路,感应放大电路与第一全局位线子译码器的输出端和第二全局位线子译码器的输出端电性连接,感应放大电路所形成的感应放大电路区块位于第一俯视投影区域和/或第二俯视投影区域内。

在其中一些实施方式中,感应放大电路包括第一感应放大子电路和第二感应放大子电路,第一感应放大子电路与第一全局位线子译码器的输出端电性连接,第一感应放大子电路所形成的第一感应放大子电路区块位于第一俯视投影区域内;第二感应放大子电路与第二全局位线子译码器的输出端电性连接,第二感应放大子电路所形成的第二感应放大子电路区块位于第二俯视投影区域内。

在其中一些实施方式中,逻辑控制电路还包括第一局部位线子译码器,第一局部位线子译码器包括与第一全局位线子译码器电性连接的第一局部位线译码单元和第二局部位线译码单元,第一局部位线译码单元所形成的第一局部位线译码单元区块、第二局部位线译码单元所形成的第二局部位线译码单元区块均位于第一俯视投影区域内;在第二方向上,第一全局位线子译码器区块位于第一局部位线译码单元区块与第二局部位线译码单元区块之间。

在其中一些实施方式中,局部位线译码器还包括第二局部位线子译码器,第二局部位线子译码器包括与第二全局位线子译码器电性连接的第三局部位线译码单元和第四局部位线译码单元,第三局部位线译码单元所形成的第三局部位线译码单元区块、第四局部位线译码单元所形成的第四局部位线译码单元区块均位于第二俯视投影区域内,在第二方向上,第二全局位线子译码器区块位于第四局部位线译码单元区块与第三局部位线译码单元区块之间。

在其中一些实施方式中,在第二方向上,第四局部位线译码单元区块、第三局部位线译码单元区块、第二局部位线译码单元区块以及第一局部位线译码单元区块依次排列;在第二方向上,第一全局位线子译码器区块至第二局部位线译码单元区块的距离小于第一全局位线子译码器区块至第一局部位线译码单元区块的距离;在第二方向上,第二全局位线子译码器区块至第三局部位线译码单元区块的距离小于第二全局位线子译码器区块至第四局部位线译码单元区块的距离。

在其中一些实施方式中,逻辑控制电路还包括第一字线译码单元和第二字线译码单元,第一字线译码单元与第一存储块电性连接,第一字线译码单元所形成的第一字线译码单元区块位于第一俯视投影区域内;第二字线译码单元与第一存储块电性连接,第二字线译码单元所形成的第二字线译码单元区块位于第一俯视投影区域内;其中,在第一方向上,第一字线译码单元区块的投影与第二字线译码单元区块的投影至少部分重叠;且第一字线译码单元区块、第二字线译码单元区块均位于第一全局位线子译码器区块与第一局部位线译码单元区块之间。

在其中一些实施方式中,在第一方向上,第一感应放大子电路区块位于第一字线译码单元区块与第二字线译码单元区块之间;且在第二方向上,第一感应放大子电路区块位于第一全局位线子译码器区块与第一局部位线译码单元区块之间。

在其中一些实施方式中,在第一方向上,第一感应放大子电路区块的投影与第一字线译码单元区块的投影和/或第二字线译码单元区块的投影至少部分重叠。

在其中一些实施方式中,在第二方向上,第一感应放大子电路区块的投影与第一字线译码单元区块的投影和/或第二字线译码单元区块的投影互不重叠。

在其中一些实施方式中,逻辑控制电路还包括第三字线译码单元和第四字线译码单元,第三字线译码单元与第二存储块电性连接,第三字线译码单元所形成的第三字线译码单元区块位于第二俯视投影区域内;第四字线译码单元与第二存储块电性连接,第四字线译码单元所形成的第四字线译码单元区块位于第二俯视投影区域内;其中,在第一方向上,第三字线译码单元区块的投影与第四字线译码单元区块的投影至少部分重叠;且第三字线译码单元区块、第四字线译码单元区块均位于第二全局位线子译码器区块与第四局部位线译码单元区块之间。

在其中一些实施方式中,第一芯片包括N个沿第二方向依次排列的存储块,第一存储阵列包括M个存储块,第二存储阵列包括N-M个存储块,其中,M小于N,且M、N均为正整数;第一俯视投影区域为第M个存储块在第二芯片上的投影区域,第二俯视投影区域为第M+1个存储块在第二芯片上的投影区域;第一全局位线子译码器与第一局部位线译码单元至第2M局部位线译码单元中的至少一个电性连接,第二全局位线子译码器与第2M+1局部位线译码单元至第2N局部位线译码单元中的至少一个电性连接。

在其中一些实施方式中,M等于取整后的N/2;且第二全局位线子译码器区块、第2M+1局部位线译码单元形成的第2M+1局部位线译码单元区块、第2M局部位线译码单元形成的第2M局部位线译码单元区块以及第一全局位线子译码器区块沿第二方向依次相邻排列。

在其中一些实施方式中,存储器件还包括多条第一走线和多条第二走线,多条第一走线与第一全局位线子译码器、第一局部位线译码单元至第2M局部位线译码单元电性连接;多条第二走线与第二全局位线子译码器、第2M+1局部位线译码单元至第2N局部位线译码单元电性连接。

在其中一些实施方式中,在第二方向上,第二感应放大子电路区块的投影与第三字线译码单元区块的投影和/或第四字线译码单元区块的投影互不重叠。

第二方面,本申请提供一种存储器件的制备方法,其包括:构造第一存储阵列、第二存储阵列于第一芯片,第一存储阵列包括至少一个第一存储块,第一存储块包括多条沿第一方向延伸的第一字线和多条沿第二方向延伸的第一位线,第二存储阵列包括至少一个第二存储块,第二存储块包括多条沿第一方向延伸的第二字线和多条沿第二方向延伸的第二位线;构造逻辑控制电路于第二芯片,逻辑控制电路包括第一全局位线子译码器和第二全局位线子译码器,第一全局位线子译码器与至少一个第一存储块电性连接,第二全局位线子译码器与至少一个第二存储块电性连接,第二芯片具有一第一存储块的第一俯视投影区域和一第二存储块的第二俯视投影区域;第一全局位线子译码器形成的第一全局位线子译码器区块位于第一俯视投影区域内,第二全局位线子译码器形成的第二全局位线子译码器区块位于第二俯视投影区域内;且在第二方向上,第二俯视投影区域、第一俯视投影区域依次排列;以及沿第三方向叠置第二芯片于第一芯片的上方。

在其中一些实施方式中,制备方法还包括:构造感应放大电路于逻辑控制电路;电性连接感应放大电路与第一全局位线子译码器的输出端、第二全局位线子译码器的输出端;以及配置感应放大电路所形成的感应放大电路区块位于第一俯视投影区域和/或第二俯视投影区域内。

在其中一些实施方式中,制备方法还包括:构造第一感应放大子电路、第二感应放大子电路于感应放大电路;电性连接第一感应放大子电路与第一全局位线子译码器的输出端,且电性连接第二感应放大子电路与第二全局位线子译码器的输出端;以及配置第一感应放大子电路所形成的第一感应放大子电路区块位于第一俯视投影区域,且配置第二感应放大子电路所形成的第二感应放大子电路区块位于第二俯视投影区域。

本申请提供的存储器件及其制备方法,通过构造第一全局位线子译码器区块位于第一存储块所形成的第一俯视投影区域以及第二全局位线子译码器区块位于第二存储块所形成的第二俯视投影区域内,可以减小第一芯片与第二芯片堆叠后的占用面积,进而减小了存储器件的占用面积,有助于实现存储器件的最小化尺寸。

基于译码器完全在投影范围内的设置以及两颗芯片的堆叠结构,译码器可以垂直地与存储阵列连接无需通过额外的横向走线连接,因此两个子模块之间并不需要留置走线空间,可以进一步减少第一芯片和第二芯片的面积。

附图说明

下面结合附图,通过对本申请的具体实施方式详细描述,将使本申请的技术方案及其它有益效果显而易见。

图1为传统技术方案提供的存储器件中各部分结构的一种分布示意图。

图2为传统技术方案提供的存储器件中各部分结构的另一种分布示意图。

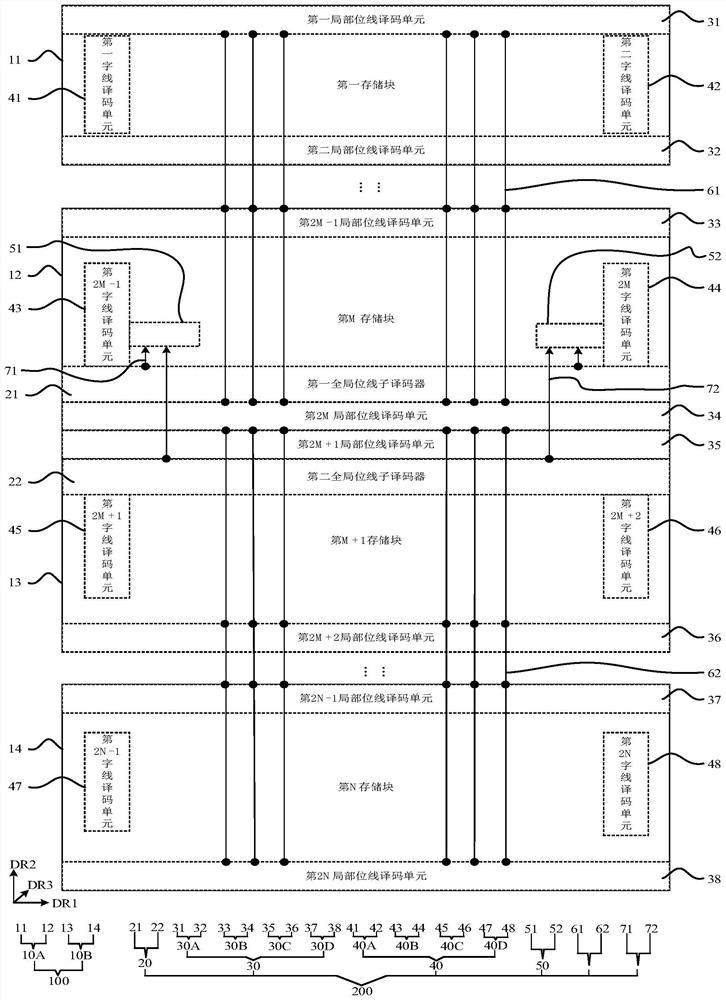

图3为本申请实施例提供的存储器件的一种结构分布示意图。

图4为本申请实施例提供的存储器件的另一种结构分布示意图。

图5为图3中第一感应放大子电路的结构分布示意图。

图6为图5中第二感应放大子电路的结构分布示意图。

图7为本申请实施例提供的存储器件的制备方法的流程示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

在本公开的描述中,字线译码器也被描述为X-DEC,位线译码器可被描述为位线选择器、位线复用器或Y-MUX,用以进行存储阵列中的多数存储单元的定位,供进一步对存储单元进行读写动作。

在本公开的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系均为基于附图所示的方位或位置关系,仅是为了便于简化描述本公开,而不是指示或暗示所指的装置或组件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本公开的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本公开的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

在本公开的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接或可以相互通讯;可以是直接相连,也可以通过中间媒介间接相连,可以是两个组件内部的连通或两个组件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本公开中的具体含义。

在本公开中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一特征和第二特征直接接触,也可以包括第一特征和第二特征不是直接接触而是通过它们之外的第三特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征的水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征的水平高度小于第二特征。

请参阅图3至图7,如图3所示,本实施例提供了一种存储器件,其包括第一芯片100和第二芯片200,第一芯片100包括第一存储阵列10A和第二存储阵列10B,第一存储阵列10A包括至少一个第一存储块,第一存储块11包括多条沿第一方向DR1延伸的第一字线和多条沿第二方向DR2延伸的第一位线,第二存储阵列10B包括至少一个第二存储块,第二存储块包括多条沿第一方向DR1延伸的第二字线和多条沿第二方向DR2延伸的第二位线;第二芯片200包括逻辑控制电路,逻辑控制电路包括第一全局位线子译码器21和第二全局位线子译码器22,第一全局位线子译码器21与至少一个第一存储块11电性连接,第二全局位线子译码器22与至少一个第二存储块电性连接;第二芯片200具有一第一存储块的第一俯视投影区域和一第二存储块的第二俯视投影区域;第一全局位线子译码器21形成的第一全局位线子译码器区块位于第一俯视投影区域内,第二全局位线子译码器22形成的第二全局位线子译码器区块位于第二俯视投影区域内;且在第二方向DR2上,第二俯视投影区域、第一俯视投影区域依次排列。

可以理解的是,本实施例提供的存储器件,通过构造第一全局位线子译码器区块位于第一存储块所形成的第一俯视投影区域以及第二全局位线子译码器区块位于第二存储块所形成的第二俯视投影区域内,可以减小第一芯片100与第二芯片200堆叠后的占用面积,进而减小了存储器件的占用面积,有助于实现存储器件的最小化尺寸。

其中,逻辑控制电路包括全局位线译码器20,全局位线译码器20包括第一全局位线子译码器21和第二全局位线子译码器22。

需要进行说明的是,本申请中的至少部分重叠可以为部分重叠,还可以为全部重叠。第一存储块可以为第一存储阵列10A中的任一存储块,例如,第一存储块11至第M存储块12中的任一个。具体地,第一存储块可以为第M存储块12。第二存储块可以为第二存储阵列10B中的任一存储块,例如,第M+1存储块13至第N存储块14中的任一个。具体地,第二存储块可以为第M+1存储块13。其中,M、N均为正整数,且N大于M。

第一方向DR1可以为字线的延伸方向。第二方向DR2可以为位线的延伸方向。第三方向DR3可以为存储器件的厚度方向。

在其中一个实施例中,在第二方向DR2上,第一俯视投影区域、第二俯视投影区域相邻。相邻指的是两个投影区的边缘相接或边缘靠近。可以理解的是,如此,第一全局位线子译码器21、第二全局位线子译码器22以及感应放大电路50三者之间的空间分布可以更为紧凑,便于第一全局位线子译码器21、第二全局位线子译码器22共用同一感应放大电路50,也可以减少感应放大电路50至第一全局位线子译码器21、第二全局位线子译码器22的电性传输距离。

在其中一个实施例中,在第一方向DR1上,第一全局位线子译码器区块的长度小于或者等于第一俯视投影区域的长度;在第一方向DR1上,第二全局位线子译码器区块的长度小于或者等于第二俯视投影区域的长度。

在其中一个实施例中,在第一方向DR1上,第一俯视投影区域的长度等于第二俯视投影区域的长度。

在其中一个实施例中,逻辑控制电路还包括感应放大电路50,感应放大电路50与第一全局位线子译码器21的输出端和第二全局位线子译码器22的输出端电性连接,感应放大电路50所形成的感应放大电路区块位于第一俯视投影区域和/或第二俯视投影区域内。可以理解的是,本实施例提供的存储器件,通过构造感应放大电路区块位于第一俯视投影区域和/或第二俯视投影区域内,可以进一步减小第一芯片100与第二芯片200堆叠后的占用面积,进而减小了存储器件的占用面积,有助于实现存储器件的最小化尺寸;并且缩短了感应放大电路50和两个全局位线子译码器之间的距离,减小了延迟。

需要进行说明的是,在本实施例中,第一存储阵列10A与第二存储阵列10B可以共用同一感应放大电路50。

如图4所示,在其中一个实施例中,感应放大电路50包括第一感应放大子电路51、第二感应放大子电路52、第三感应放大子电路53以及第四感应放大子电路54,第一全局位线子译码器21的输出端与第一感应放大子电路51、第二感应放大子电路52电性连接,第一感应放大子电路51所形成的第一感应放大子电路区块、第二感应放大子电路52所形成的第二感应放大子电路区块均位于第一俯视投影区域内;第二全局位线子译码器22的输出端与第三感应放大子电路53、第四感应放大子电路54电性连接,第三感应放大子电路53所形成的第三感应放大子电路区块、第四感应放大子电路54所形成的第四感应放大子电路区块均位于第二俯视投影区域内。

可以理解的是,在本实施例中,第一存储阵列10A通过第一全局位线子译码器21与第一感应放大子电路51、第二感应放大子电路52电性连接,第二存储阵列10B通过第二全局位线子译码器22与第三感应放大子电路53、第四感应放大子电路54电性连接,每个存储阵列可以单独采用一组感应放大子电路,如此可以分别独立实现每个存储阵列的位线读出操作。

在其中一个实施例中,逻辑控制电路还包括局部位线译码器30,局部位线译码器30包括第一局部位线子译码器30A,第一局部位线子译码器30A与第一全局位线子译码器21电性连接,第一局部位线子译码器30A包括第一局部位线译码单元31和第二局部位线译码单元32,第一局部位线译码单元31所形成的第一局部位线译码单元区块、第二局部位线译码单元32所形成的第二局部位线译码单元区块均位于第一俯视投影区域内;在第二方向DR2上,第一全局位线子译码器区块位于第一局部位线译码单元区块与第二局部位线译码单元区块之间。

可以理解的是,本实施例提供的存储器件,通过构造第一局部位线译码单元区块、第二局部位线译码单元区块位于第一俯视投影区域内,可以进一步减小第一芯片100与第二芯片200堆叠后的占用面积,进而减小了存储器件的占用空间,有助于实现存储器件的最小化尺寸。

在一些实施例中,第一全局位线子译码器区块、第一局部位线译码单元区块和/或第二局部位线译码单元区块可以位于同一芯片的不同层中,第一全局位线子译码器区块与第一局部位线译码单元区块和/或第二局部位线译码单元区块也可以在第三方向上DR3至少部分重叠。

在一些实施例中,第一全局位线子译码器区块位于第一局部位线译码单元区块与第二局部位线译码单元区块之间,且第一全局位线子译码器区块与第一局部位线译码单元区块和/或第二局部位线译码单元区块并不发生重叠。

需要进行说明的是,在本实施例中,每一个第一存储块均与一个对应的局部位线子译码器电性连接。例如,第一存储块11可以与第一局部位线译码单元31和第二局部位线译码单元32电性连接,局部位线译码器30还包括第M局部位线子译码器30B,第M局部位线子译码器30B包括第2M-1局部位线译码单元33和第2M局部位线译码单元34,第M存储块12可以与第2M-1局部位线译码单元33和第2M局部位线译码单元34电性连接。其中,第一存储块可以为第一存储块11至第M存储块12中的任一个存储块,当第一存储块为第M存储块12时,第一局部位线译码单元可以为第2M-1局部位线译码单元33;第二局部位线译码单元可以为第2M局部位线译码单元34。同理,第二存储块可以为第M+1存储块13至第N存储块14中的任一个存储块。

在其中一个实施例中,局部位线译码器30还包括第二局部位线子译码器30C,第二局部位线子译码器30C与第二全局位线子译码器22电性连接,第二局部位线子译码器30C包括第三局部位线译码单元35和第四局部位线译码单元36,第三局部位线译码单元35所形成的第三局部位线译码单元区块、第四局部位线译码单元36所形成的第四局部位线译码单元区块均位于第二俯视投影区域内,在第二方向DR2上,第二全局位线子译码器区块位于第四局部位线译码单元区块与第三局部位线译码单元区块之间。

需要进行说明的是,在本实施例中,每一个第二存储块均与一个对应的局部位线子译码器电性连接。例如,第二存储块可以与第三局部位线译码单元35和第四局部位线译码单元36电性连接,第二局部位线子译码器30C可以为第M+1局部位线子译码器30C,第M+1局部位线子译码器30C包括第2M+1局部位线译码单元35和第2M+2局部位线译码单元36,第M+1存储块13可以与第2M+1局部位线译码单元35和第2M+2局部位线译码单元36电性连接,局部位线译码器30还包括第四局部位线子译码器,第四局部位线子译码器可以为第N局部位线子译码器30D,第N局部位线子译码器30D包括第2N-1局部位线译码单元37和第2N局部位线译码单元38,第N存储块14可以与第2N-1局部位线译码单元37和第2N局部位线译码单元38电性连接。

在其中一个实施例中,在第二方向DR2上,第四局部位线译码单元区块、第三局部位线译码单元区块、第二局部位线译码单元区块以及第一局部位线译码单元区块依次排列;在第二方向DR2上,第一全局位线子译码器区块至第二局部位线译码单元区块的距离小于第一全局位线子译码器区块至第一局部位线译码单元区块的距离;在第二方向DR2上,第二全局位线子译码器区块至第三局部位线译码单元区块的距离小于第二全局位线子译码器区块至第四局部位线译码单元区块的距离。

在其中一个实施例中,逻辑控制电路还包括第一字线译码单元41和第二字线译码单元42,第一字线译码单元41与第一存储块11电性连接,第一字线译码单元41所形成的第一字线译码单元区块位于第一俯视投影区域内;第二字线译码单元42与第一存储块11电性连接,第二字线译码单元42所形成的第二字线译码单元区块位于第一俯视投影区域内;其中,在第一方向DR1上,第一字线译码单元区块的投影与第二字线译码单元区块的投影至少部分重叠;且第一字线译码单元区块、第二字线译码单元区块均位于第一全局位线子译码器区块与第一局部位线译码单元区块之间(如图4,当M取1,N取2时)。

可以理解的是,本实施例提供的存储器件,通过构造第一字线译码单元41所形成的第一字线译码单元区块、第二字线译码单元42所形成的第二字线译码单元区块位于第一俯视投影区域内,可以进一步减小第一芯片100与第二芯片200堆叠后的占用面积,进而减小了存储器件的占用空间,有助于实现存储器件的最小化尺寸。

在一些实施例中,第一字线译码单元区块、第二字线译码单元区块均位于第一全局位线子译码器区块与第二局部位线译码单元区块之间,且第一字线译码单元区块与第一全局位线子译码器区块和/或第二局部位线译码单元区块并不发生重叠,第二字线译码单元区块与第一全局位线子译码器区块和/或第二局部位线译码单元区块也不发生重叠。第一字线译码单元区块与第二字线译码单元区块也并不发生重叠。

需要进行说明的是,在本实施例中,逻辑控制电路包括字线译码器40,字线译码器40包括至少一个字线子译码器,字线子译码器可以包括两个字线译码单元,在一些实施例中,任一存储块均配置有一个或者两个对应的字线译码单元,例如,第一字线子译码器40A包括第一字线译码单元41和第二字线译码单元42,第一存储块11与第一字线译码单元41和第二字线译码单元42电性连接,第M字线子译码器40B包括第2M-1字线译码单元43和第2M字线译码单元44,第M存储块12与第2M-1字线译码单元43和第2M字线译码单元44电性连接,第M+1字线子译码器40C包括第2M+1字线译码单元45和第2M+2字线译码单元46,第M+1存储块13与第2M+1字线译码单元45和第2M+2字线译码单元46电性连接,第N字线子译码器40D包括第2N-1字线译码单元47和第2N字线译码单元48,第N存储块14与第2N-1字线译码单元47和第2N字线译码单元48电性连接。

在其中一个实施例中,在第一方向DR1上,第一感应放大子电路区块位于第一字线译码单元区块与第二字线译码单元区块之间;且在第二方向DR2上,第一感应放大子电路区块位于第一全局位线子译码器区块与第一局部位线译码单元区块之间。

可以理解的是,在本实施例中,第一感应放大子电路区块与第一字线译码单元区块和/或第二字线译码单元区块并不发生重叠,同理,第一感应放大子电路区块与第一全局位线子译码器区块和/或第一局部位线译码单元区块也不发生重叠。

在其中一个实施例中,在第一方向DR1上,第一感应放大子电路区块的投影与第一字线译码单元区块的投影和/或第二字线译码单元区块的投影至少部分重叠。

在其中一个实施例中,在第二方向DR2上,第一感应放大子电路区块的投影与第一字线译码单元区块的投影和/或第二字线译码单元区块的投影互不重叠。

在其中一个实施例中,第二芯片200还包括多条第一走线61,多条第一走线61与第一全局位线子译码器21和第一局部位线译码单元31至第2M局部位线译码单元34电性连接。

在其中一个实施例中,第二芯片200还包括多条第二走线62,多条第二走线62与第二全局位线子译码器22和第2M+1局部位线译码单元35至第2N局部位线译码单元38电性连接。

其中,第一走线61、第二走线62均可以为全局位线。这种设置相当于将存储块分为了两组(第一存储阵列10A、第二存储阵列10B),第一存储块11至第M存储块12为第一组存储块(第一存储阵列10A),第M+1存储块13至第N存储块14为第二组存储块(第二存储阵列10B)。第一走线61将第一组存储块电连接到第一全局位线子译码器21,第二走线62将第二组存储块电连接到第二全局位线子译码器22,这样将存储块分组的方式,配合三维键合工艺(即将第二芯片200在第三方向上堆叠/键合到第一芯片100)能够综合缩短各存储块到全局译码器/全局位线译码器20之间的连线,也减少了全局译码器/全局位线译码器20到局部译码器/局部位线译码器30之间的连线,使得芯片延迟大大降低。

在其中一个实施例中,第二芯片200还包括多条第三走线71,多条第三走线71与第一全局位线子译码器21和感应放大电路50电性连接。

在其中一个实施例中,第二芯片200还包括多条第四走线72,多条第四走线72与第二全局位线子译码器22和感应放大电路50电性连接。

其中,如图5所示,第一感应放大子电路51可以包括多个沿第一方向DR1排列的感应放大器,例如,感应放大器51A、感应放大器51B、感应放大器51C、感应放大器51D等等。第二感应放大子电路52也可以包括多个沿第一方向DR1排列的感应放大器,例如,感应放大器52A、感应放大器52B、感应放大器52C、感应放大器52D等等。其中,第一方向DR1可以为第一存储阵列10A或者第二存储阵列10B的位线排列方向。

其中,如图6所示,第三感应放大子电路53可以包括多个沿第一方向DR1排列的感应放大器,例如,感应放大器53A、感应放大器53B、感应放大器53C、感应放大器53D等等。第四感应放大子电路54也可以包括多个沿第一方向DR1排列的感应放大器,例如,感应放大器54A、感应放大器54B、感应放大器54C、感应放大器54D等等。

在其中一个实施例中,第N存储块14至第一存储块11沿第二方向DR2依次排列,第二方向DR2可以为第一存储阵列10A或者第二存储阵列10B的字线排列方向。

在其中一个实施例中,第一芯片100与第二芯片200沿第三方向DR3重叠或者堆叠,可以理解的是,第三方向DR3可以为第一芯片100与第二芯片200堆叠后的厚度方向。

在其中一个实施例中,逻辑控制电路还包括第三字线译码单元和第四字线译码单元,第三字线译码单元与第二存储块电性连接,第三字线译码单元所形成的第三字线译码单元区块位于第二俯视投影区域内;第四字线译码单元与第二存储块电性连接,第四字线译码单元所形成的第四字线译码单元区块位于第二俯视投影区域内;其中,在第一方向DR1上,第三字线译码单元区块的投影与第四字线译码单元区块的投影至少部分重叠;且第三字线译码单元区块、第四字线译码单元区块均位于第二全局位线子译码器区块与第四局部位线译码单元区块之间。

在其中一个实施例中,在第一方向DR1上,第二感应放大子电路区块位于第三字线译码单元区块与第四字线译码单元区块之间;且在第二方向DR2上,第二感应放大子电路区块位于第二全局位线子译码器区块与第四局部位线译码单元区块之间。

在其中一个实施例中,在第一方向DR1上,第二感应放大子电路区块的投影与第三字线译码单元区块的投影和/或第四字线译码单元区块的投影至少部分重叠。

在其中一个实施例中,在第二方向DR2上,第二感应放大子电路区块的投影与第三字线译码单元区块的投影和/或第四字线译码单元区块的投影互不重叠。

需要进行说明的是,第二感应放大子电路区块的投影与第三字线译码单元区块的投影和/或第四字线译码单元区块的投影互不重叠。其指:沿第二方向,第二感应放大子电路区块可以具有第二感应放大子电路区块的投影,第三字线译码单元区块可以具有第三字线译码单元区块的投影,第四字线译码单元区块可以具有第四字线译码单元区块的投影;且在第二方向上,第二感应放大子电路区块的投影与第三字线译码单元区块的投影和/或第四字线译码单元区块的投影在任一个垂直于第二方向的平面上均不重叠。

在其中一个实施例中,第一芯片100包括N个沿第二方向DR2依次排列的存储块,第一存储阵列10A包括M个存储块,第二存储阵列10B包括N-M个存储块,其中,M小于N,且M、N均为正整数;第一俯视投影区域为第M个存储块12在第二芯片200上的投影区域,第二俯视投影区域为第M+1个存储块13在第二芯片200上的投影区域;第一全局位线子译码器21与第一局部位线译码单元31至第2M局部位线译码单元34中的至少一个电性连接,第二全局位线子译码器22与第2M+1局部位线译码单元35至第2N局部位线译码单元38中的至少一个电性连接。

在其中一个实施例中,M等于取整后的N/2;且第二全局位线子译码器区块、第2M+1局部位线译码单元35形成的第2M+1局部位线译码单元区块、第2M局部位线译码单元34形成的第2M局部位线译码单元区块以及第一全局位线子译码器区块沿第二方向DR2依次相邻排列。

在其中一个实施例中,存储器件还包括多条第一走线61和多条第二走线62,多条第一走线61与第一全局位线子译码器21、第一局部位线译码单元31至第2M局部位线译码单元34电性连接;多条第二走线62与第二全局位线子译码器22、第2M+1局部位线译码单元35至第2N局部位线译码单元38电性连接。

在其中一个实施例中,在第二方向DR2上,第二感应放大子电路区块的投影与第三字线译码单元区块的投影和/或第四字线译码单元区块的投影互不重叠。

如图7所示,在其中一个实施例中,本实施例提供一种存储器件的制备方法,其包括以下步骤:

步骤S10:构造第一存储阵列、第二存储阵列于第一芯片,第一存储阵列包括至少一个第一存储块,第一存储块包括多条沿第一方向延伸的第一字线和多条沿第二方向延伸的第一位线,第二存储阵列包括至少一个第二存储块,第二存储块包括多条沿第一方向延伸的第二字线和多条沿第二方向延伸的第二位线。

步骤S20:构造逻辑控制电路于第二芯片,逻辑控制电路包括第一全局位线子译码器和第二全局位线子译码器,第一全局位线子译码器与至少一个第一存储块电性连接,第二全局位线子译码器与至少一个第二存储块电性连接,第二芯片具有一第一存储块的第一俯视投影区域和一第二存储块的第二俯视投影区域;第一全局位线子译码器形成的第一全局位线子译码器区块位于第一俯视投影区域内,第二全局位线子译码器形成的第二全局位线子译码器区块位于第二俯视投影区域内;且在第二方向上,第二俯视投影区域、第一俯视投影区域依次排列。

以及步骤S30:沿第三方向叠置第二芯片于第一芯片的上方。

可以理解的是,本实施例提供的制备方法,通过构造第一全局位线子译码器区块位于第一存储块所形成的第一俯视投影区域以及第二全局位线子译码器区块位于第二存储块所形成的第二俯视投影区域内,可以减小第一芯片与第二芯片堆叠后的占用面积,进而减小了存储器件的占用面积,有助于实现存储器件的最小化尺寸。

在其中一个实施例中,制备方法还包括:构造感应放大电路于逻辑控制电路;电性连接感应放大电路与第一全局位线子译码器的输出端、第二全局位线子译码器的输出端;以及配置感应放大电路所形成的感应放大电路区块位于第一俯视投影区域和/或第二俯视投影区域内。

在其中一个实施例中,制备方法还包括:构造第一感应放大子电路、第二感应放大子电路于感应放大电路;电性连接第一感应放大子电路与第一全局位线子译码器的输出端,且电性连接第二感应放大子电路与第二全局位线子译码器的输出端;以及配置第一感应放大子电路所形成的第一感应放大子电路区块位于第一俯视投影区域,且配置第二感应放大子电路所形成的第二感应放大子电路区块位于第二俯视投影区域。

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

以上对本申请实施例所提供的存储器件及其制备方法进行了详细介绍,本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例的技术方案的范围。