像素阵列基板和缺陷预防方法

文献发布时间:2023-06-19 13:46:35

技术领域

本发明涉及一种像素阵列基板、包括该像素阵列基板的图像传感器以及一种用于防止沉积在包括像素阵列的半导体基板上的薄膜中的缺陷的方法。

背景技术

在诸如独立数码相机、移动设备、汽车组件和医疗设备之类的商业产品中,相机模块包括图像传感器。图像传感器包括像素阵列以及,在围绕像素阵列的外围区域中,包括模拟设备。图像传感器包括半导体基板和基板背表面上的钝化层。钝化层由于材料引起的应力而易于产生气泡缺陷,特别是在大表面区域周围。气泡缺陷常常成为钝化层的破裂区域或剥离区域,这增加了外围模拟设备中的噪声,并因此降级了由图像传感器捕获的图像的质量。

发明内容

这里公开的实施例通过在外围区域中包括沟槽来防止气泡缺陷。本发明提供了一种像素阵列基板、包括该像素阵列基板的图像传感器以及一种用于防止沉积在包括像素阵列的半导体基板上的薄膜中的缺陷的方法。

在第一方面,像素阵列基板包括半导体基板和钝化层。半导体基板包括被外围区域包围的像素阵列。半导体基板的背表面在外围区域中形成延伸到半导体基板中的多个第一外围沟槽。钝化层在背表面上,并且衬于多个第一外围沟槽中的每个第一外围沟槽。

在实施例中,像素阵列基板还包括多个列间沟槽,每个列间沟槽位于所述像素阵列的相应的一对相邻像素列之间,相邻的列间沟槽之间的第一距离等于相邻的第一外围沟槽之间的距离。

在实施例中,所述多个第一外围沟槽中的每个第一外围沟槽是所述多个列间沟槽中的相应列间沟槽的延伸。

在实施例中,所述多个第一外围沟槽中的每个沟槽具有相对于包围所述沟槽的所述背表面的平面区域超过0.2微米的深度。

在实施例中,所述多个第一外围沟槽中的每个沟槽具有相对于包围所述沟槽的所述背表面的平面区域的比所述半导体基板的厚度小0.5微米和2.0微米之间的深度。

在实施例中,所述钝化层的厚度在40埃和500埃之间。

在实施例中,所述钝化层由高κ材料形成。

在实施例中,所述多个第一外围沟槽中的每个第一外围沟槽具有在0.15微米和0.25微米之间的宽度。

在实施例中,所述多个第一外围沟槽中的每个第一外围沟槽填充有绝缘材料。

在实施例中,所述背表面还在所述外围区域中形成延伸到所述半导体基板中的多个第二外围沟槽,所述多个第二外围沟槽中的每个第二外围沟槽垂直于所述多个第一外围沟槽中的每个第一外围沟槽,所述钝化层衬于所述多个第二外围沟槽中的每个第二外围沟槽。

在实施例中,像素阵列基板还包括多个行间沟槽,每个行间沟槽位于所述像素阵列的相应的一对相邻像素行之间,相邻的行间沟槽之间的第二距离等于相邻的第二外围沟槽之间的距离。

在实施例中,所述多个第二外围沟槽中的每个第二外围沟槽是所述多个行间沟槽中的相应行间沟槽的延伸。

在实施例中,所述多个第二外围沟槽中的每个沟槽具有相对于包围所述沟槽的所述背表面的平面区域的比所述半导体基板的厚度小0.5微米和2.0微米之间的深度。

在第二方面,提供了一种图像传感器。图像传感器包括根据第一方面的像素阵列基板;以及由多个微透镜形成的微透镜阵列,每个微透镜与所述像素阵列的相应光电二极管区域对准。

第三方面是一种用于防止沉积在包括像素阵列的半导体基板上的薄膜中的缺陷的方法。该方法包括在半导体基板的外围区域上形成多个沟槽以产生带沟槽的表面。外围区域包围像素阵列。带沟槽的表面(i)包括多个沟槽区域,每个沟槽区域形成多个沟槽中的相应沟槽,以及(ii)在每对相邻的沟槽之间,包括多个沟槽间表面中的相应沟槽间表面。该方法还包括在表面上沉积薄膜,使得薄膜覆盖每个沟槽间表面并保形地覆盖每个沟槽区域。

在实施例中,形成所述多个沟槽包括光刻蚀刻所述外围区域的表面,所述表面是所述半导体基板的背表面的一部分。

在实施例中,所述方法还包括:对所述薄膜进行退火;并且用氧化物材料和金属中的至少一种填充所述多个沟槽中的每个沟槽。

在实施例中,在所述形成步骤中,所述多个沟槽中的每个沟槽垂直于所述多个沟槽中的至少一个其他沟槽并与之相交,所述多个沟槽形成网格。

在实施例中,所述半导体基板包括被所述外围区域包围的中心区域,并且在所述形成步骤中,所述多个沟槽包括多个中心区域沟槽,所述多个中心区域沟槽各自横穿所述外围区域和所述中心区域,并且位于(i)所述像素阵列的一对相邻像素行之间或(ii)所述像素阵列的一对相邻像素列之间。

在实施例中,每个沟槽间表面是在所述多个沟槽中的两个相邻沟槽之间的所述半导体基板的背表面的相应平面区域。

附图说明

图1描绘了对场景进行成像的相机。

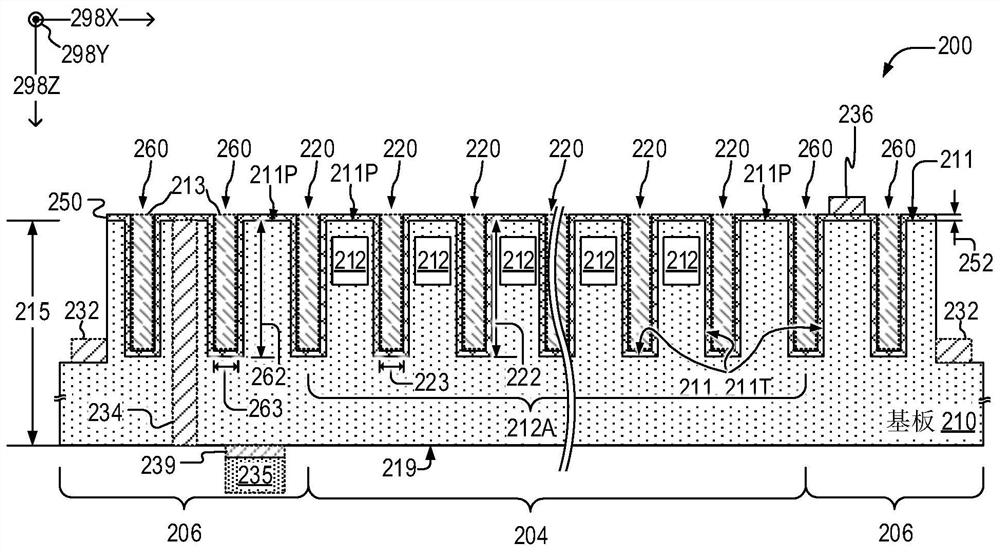

图2是实施例中的像素阵列基板的横截面示意图,并且图3是其平面图,该像素阵列基板是图1的相机的像素阵列基板的示例。

图4是在实施例中包括图2和3的像素阵列基板的图像传感器的横截面示意图。

图5是图示实施例中用于防止沉积在基板上的薄膜中的缺陷的方法的流程图。

具体实施方式

在整个说明书中对“一个示例”或“一个实施例”的引用是指结合该示例描述的特定特征、结构或特点包括在本发明的至少一个示例中。因此,在整个说明书中各处出现的短语“在一个示例中”或“在一个实施例中”不一定都是指同一个示例。此外,在一个或多个示例中,可以以任何合适的方式组合特定的特征、结构或特点。

为了便于描述,在本文中可以使用空间相对术语,诸如“在...下方”、“在...之下”、“下”、“在...下面”、“在...上方”、“上”等,以描述一个元件或特征与另一个(多个)元件或特征的关系,如图所示。将理解的是,除了附图中描绘的朝向之外,空间相对术语还意图涵盖设备在使用或操作中的不同朝向。例如,如果附图中的设备被翻转,那么被描述为在其他元件或特征“下方”或“之下”或“下面”的元件将被定向为在其他元件或特征“上方”。因此,术语“在...之下”和“在...下面”可以涵盖上方和下方两个朝向。可以以其他方式将设备定向(旋转九十度或以其他朝向),并相应地解释本文中使用的空间相对描述语。此外,还将理解的是,当一层被称为在两层“之间”时,它可以是两层之间的唯一层,或者也可以存在一个或多个中间层。

术语半导体基板可以是指使用诸如硅、硅-锗、锗、砷化镓及其组合之类的半导体形成的基板。术语半导体基板也可以指由一种或多种半导体形成的基板,该基板经历了在基板中形成区域和/或结的先前工艺步骤。半导体基板还可以包括各种特征,诸如掺杂和未掺杂的半导体、硅的外延层以及在基板上形成的其他半导体结构。

在整个说明书中,使用了几个技术术语。这些术语应具有其所属领域中的普通含义,除非在本文中专门定义或者它们的使用上下文明确地暗示为其他。应当注意的是,在本文档中,元素名称和符号可以互换使用(例如,Si与硅);但是,两者具有完全相同的含义。

图1描绘了对场景进行成像的相机190。相机190包括图像传感器192,图像传感器192包括像素阵列基板100。像素阵列基板100的组成元素可以包括硅和锗中的至少一种。像素阵列基板100包括像素阵列112A。图像传感器192可以是芯片级封装或板上芯片封装的一部分。

图2是像素阵列基板200的横截面示意图并且图3是其平面图,该像素阵列基板200是像素阵列基板100的示例。图2的横截面视图在图3中表示的平面1A中。图2中所示的横截面平行于由正交轴298X和298Z形成的平面,下文中称为x-z平面,正交轴298X和298Z各自正交于轴298Y。在本文中,x-y平面由正交轴298X和298Y形成,并且平行于x-y平面的平面被称为横向平面。除非另有说明,否则本文中对象的高度是指对象沿着轴298Z的范围。在本文中,对轴x,y或z的引用分别是指轴298X、298Y和298Z。而且,在本文中,水平平面平行于x-y平面,宽度是指对象沿着y轴的范围,并且竖直是指沿着z轴的方向。

像素阵列基板200包括半导体基板210和钝化层250。钝化层250可以由高κ材料形成,例如,介电常数κ大于或等于氮化硅的介电常数κ(κ≥7)的材料。在实施例中,钝化层250的示例材料包括氧化铝(Al

半导体基板210具有背表面211、前表面219,并且包括中心区域204和包围中心区域204的外围区域206。中心区域包括像素阵列212A,其是图1的像素阵列112A的示例。像素阵列212A包括多个像素,每个像素包括多个光电二极管区域212中的相应一个。在实施例中,光电二极管区域212包括被钉扎的光电二极管。每个像素还可以包括用于控制相关联像素的成像操作的一个或多个晶体管。每个光电二极管区域212被配置为响应于穿过半导体基板210的背表面211的入射光而光生并存储电荷。在一个实施例中,每个光电二极管区域212由掺杂注入物形成,该掺杂注入物具有与半导体基板210的第一导电类型(例如,p型)相反的第二导电类型(例如,n型)。在一些实施例中,每个光电二极管区域212被设置为,与前表面219相比,更靠近半导体基板210的背表面211。在实施例中,半导体基板210包括在表面219上或附近形成的设备栅235。在实施例中,栅氧化物层239在设备栅235和表面219之间。

像素阵列212A包括分别平行于x和y轴的多个像素行217和多个像素列218。为了说明的清楚,在图3中,并非所有像素行217和像素列218都由附图标记表示。将N

像素阵列基板200包括多个列间沟槽220,每个列间沟槽位于相应的一对相邻像素列218之间。像素阵列基板200还包括多个行间沟槽225,每个行间沟槽225位于相应的一对相邻像素行217之间。每个沟槽220和225是深沟槽隔离(DTI)结构的一部分,该结构被配置为将每个光电二极管区域212与其相邻的光电二极管区域212电隔离和/或光学隔离。多个列间沟槽220和多个行间沟槽225可以互连,以形成深沟槽网格结构,从而提供像素阵列212A中的光电二极管区域之间的隔离。

多个列间沟槽220和多个行间沟槽225中的每一个在半导体基板210的背表面211上形成,并且朝着前表面219在半导体基板210中延伸深度222。多个列间沟槽220和多个行间沟槽225中的每一个都具有衬于(lining)其内表面的钝化层250,该钝化层用于对沟槽侧壁上的缺陷提供钝化以减小暗电流。在实施例中,多个列间沟槽220和多个行间沟槽225中的每一个还具有绝缘材料213,诸如低κ电介质、金属氧化物或半导体氧化物(例如氧化硅),用于填充沟槽。在实施例中,多个列间沟槽220和多个行间沟槽225中的每一个具有导电材料,例如,金属填充沟槽以用于偏置。

在实施例中,半导体基板210在其上包括多个键合焊盘232。每个键合焊盘232电连接到至少一个像素行217或至少一个像素列218。

相邻的列间沟槽220被距离221隔开,该距离221可以等于像素阵列212A的像素间距。相邻的行间沟槽225被距离226隔开,该距离226可以等于像素阵列212A的像素节距。在本文中,除非另有说明,关于列间沟槽220的陈述同样适用于行间沟槽225。

在外围区域206中,背表面211形成朝着前表面219在半导体基板210中延伸深度262的多个第一外围沟槽,下文中称为外围沟槽260,并且或者准平行于或平行于像素列218。深度262可以与深度222相同或不同。在实施例中,深度262大于或等于深度222。在本文中,外围沟槽260准平行于像素列218意味着,与像素行217相比,外围沟槽260在更接近于平行于像素列218的方向上定向。钝化层250位于背表面211上,并衬于多个外围沟槽260中的每一个。

在实施例中,背表面211还形成多个第二外围沟槽,下文中称为外围沟槽265,除了它们与像素行217或者准平行或者平行之外,外围沟槽265类似于外围沟槽260。当外围沟槽265准平行于像素行217时,与列218相比,外围沟槽265在更接近于平行于像素行217的方向上定向。在实施例中,每个外围沟槽265垂直于每个外围沟槽260。在本文中并且除非另外说明,否则关于外围沟槽260的陈述同样适用于外围沟槽265。在实施例中,外围沟槽260和外围沟槽265彼此互连。

在实施例中,半导体基板210在外围沟槽260和/或265之间包括用于芯片堆叠的一个或多个硅通孔234。在实施例中,半导体基板210在外围沟槽260和/或265之间包括一个或多个背侧接地触点236。在实施例中,半导体基板210包括注入保护环结构237,例如,n型掺杂保护环和/或半导体基板210的周界周围的密封环238。注入保护环237结构可以包围像素阵列212A。为了维持上面提到的组件的正常运行,任何外围沟槽260和/或265与以下至少一个元件之间的工艺裕度(最小距离)会超过阈值,诸如一微米:硅通孔234、背侧接地触点236、环237和环238。

在实施例中,在相邻的外围沟槽260和/或265之间至少分配有一个半导体区域,用于形成芯片封装结构,诸如硅通孔234、背侧接地触点236、键合焊盘、密封环或保护环结构,以及注入保护环。可以基于形成芯片封装结构所需的工艺裕度来确定半导体区域的尺寸。

在实施例中,外围沟槽260和/或265不在半导体基板210的形成有用于防止水分或污染物进入内部像素电路系统和键合焊盘的密封环或保护环结构的区域中。

缺少外围沟槽260,钝化层250承受外围区域206中的应力,这导致上述的气泡缺陷和随后的图像质量下降。随着近年来随着像素阵列212A的像素数增加,外围区域206的尺寸增加,这些缺陷变得更加普遍。外围沟槽260通过减小这个应力来防止中心区域204附近的气泡缺陷。

相邻的外围沟槽260被距离261隔开。在实施例中,距离261等于距离221。相邻的外围沟槽265被距离266隔开。在实施例中,距离266等于距离226。

缺少外围沟槽260、265,钝化层250将具有大表面区域,其允许应力累积对气泡缺陷的释放。因此,可以认识到的是,外围沟槽260、265形成沟槽网格结构,沟槽网格结构将外围区域206中钝化层250的较大表面区域划分为释放应力并防止应力累积的小区域,从而消除了气泡缺陷。在实施例中,朝着前表面219深入半导体基板210的外围沟槽260、265的形成引入了氟原子和氢原子,这些氟原子和氢原子扩散到前表面,从而消除了氧化物-硅界面处的悬挂键,可以进一步降低暗电流和/或噪声,例如,在设备栅235中。

图3图示了外围沟槽260,该外围沟槽260沿着x轴从列间沟槽220横向偏移距离Δx。在实施例中,Δx等于零,使得当距离261等于距离221时,每个外围沟槽260与相应的列间沟槽220对准并且是其延伸。在这样的实施例中,每个列间沟槽220和与其对准的外围沟槽260形成单个沟槽。

图3图示了外围沟槽265,外围沟槽265在y方向上从行间沟槽225横向偏移距离Δy。在实施例中,Δy等于零,使得当距离266等于距离226时,每个外围沟槽265与相应的行间沟槽225对准并且是其延伸。在这样的实施例中,每个行间沟槽225和外围沟槽265对准并与其互连以形成单个沟槽。单个沟槽可以具有均匀的深度,即,其在像素阵列212A中的深度等于其在外围区域206中的深度。

在实施例中,每个外围沟槽260的深度262超过0.2微米,以确保足够的应力释放以防止气泡缺陷。深度262相对于在其一侧或两侧上与外围沟槽260相邻的背表面211的沟槽间表面区域211P。沟槽间表面区域211P可以是共面的。图2将沟槽260内的背表面211的区域表示为沟槽区域211T。

半导体基板210具有厚度215。在实施例中,列间沟槽220的深度222比厚度215小0.5微米与2.0微米之间,以确保足够的电隔离。在实施例中,深度262等于深度222,使得列间沟槽220和与其对准的外围沟槽260可以经由例如光刻同时制造。

每个列间沟槽220具有宽度223,其可以在0.10微米和0.25微米之间。每个外围沟槽260具有宽度263。在实施例中,宽度263等于宽度223,这使得外围沟槽260和220能够用具有均匀宽度特征的单个光刻掩模同时形成。

在实施例中,每个列间沟槽220填充有绝缘材料213,这有助于使每个光电二极管区域212与其相邻的光电二极管区域212隔离。在实施例中,列间沟槽220和外围沟槽260都填充有绝缘材料213。在实施例中,当在列间沟槽220中沉积绝缘材料213时,掩蔽外围区域206以防止绝缘材料213填充外围沟槽260没有技术上的好处。这种掩蔽仅使沉积工艺复杂化。为了图示的清楚,图3未表示绝缘材料213。

图4是图像传感器492的横截面示意图,该图像传感器是图1的图像传感器192的示例。图像传感器492包括像素阵列基板200和微透镜阵列470。微透镜阵列470由多个微透镜472形成,每个微透镜472与像素阵列212A的相应光电二极管区域212对准,用于将入射光引导到相应的光电二极管区域212上。在实施例中,图像传感器492包括在微透镜阵列470和像素阵列212A之间的滤色器阵列480。滤色器阵列480包括多个滤色器482,每个滤色器与相应的微透镜472和相应的像素212对准,以对通过相应微透镜472透射的光进行光谱过滤。

图5是图示用于防止沉积在包括像素阵列的半导体基板上的薄膜中的缺陷的方法500的流程图。方法500包括步骤510和520。在实施例中,方法500还包括步骤530。方法500可以在包括但不限于形成浅沟槽隔离结构、光电二极管区域的注入、浮动扩散、像素晶体管的源极/漏极、晶体管的栅极(例如,多晶硅栅极)和侧墙(spacer,或称为间隔件)的形成,以及触点和多层金属互连结构的形成的前侧工艺之后执行。

步骤510包括在半导体基板的外围区域上形成多个沟槽以产生带沟槽的表面。带沟槽的表面(i)包括多个沟槽区域,每个沟槽区域形成多个沟槽中的相应沟槽,以及(ii)在每对相邻沟槽之间,包括多个沟槽间表面中的相应沟槽间表面。外围区域包围像素阵列。在步骤510的示例中,外围沟槽260形成在半导体基板210的表面上,其中背表面211是包括沟槽区域211T和沟槽间表面区域211P的带沟槽的表面。

在实施例中,多个沟槽中的每个沟槽垂直于多个沟槽中的至少一个其他沟槽并与之相交,多个沟槽形成网格。例如,多个沟槽包括外围沟槽260和外围沟槽265。

在实施例中,半导体基板包括被外围区域包围的中心区域,并且步骤510中,多个沟槽包括多个中心区域沟槽。每个中心区域沟槽既横穿外围区域又横穿中心区域,并且位于(i)像素阵列的一对相邻像素行之间或(ii)像素阵列的一对相邻像素列之间。列间沟槽220和行间沟槽225是中心区域沟槽的示例。

在实施例中,步骤510包括步骤512。步骤512包括光刻蚀刻外围区域的表面。在步骤512的示例中,对背表面211进行光刻蚀刻以产生外围沟槽260和外围沟槽265中的至少一个。步骤512还可以产生列间沟槽220和行间沟槽225中的至少一个。步骤512可以包括用含氟的气体蚀刻剂蚀刻(例如,干法蚀刻)表面。使用氟蚀刻剂的益处在于,到达前表面219的氟原子通过消除像素栅极的氧化物层下方的悬挂键而减少了暗电流。

步骤520包括在外围区域上沉积薄膜,使得薄膜覆盖每个沟槽间表面,并保形地覆盖每个沟槽区域。在步骤520的示例中,钝化层250被沉积在背表面211上,例如通过原子层沉积(ALD)工艺,使得钝化层250覆盖每个沟槽间表面区域211P并保形地覆盖每个沟槽区域211T。

在实施例中,步骤520包括步骤525。步骤525包括使用氢退火工艺对薄膜进行退火以使薄膜致密并在列间沟槽220、行间沟槽225和外围沟槽260、265中的每一个上或包围其侧壁建立负电荷。退火工艺可以在300℃和400℃之间的温度下执行。所述氢退火的益处在于,与上面提到的氟原子一样,到达前表面219的氢原子通过进一步消除在氧化物-硅界面处(例如,在像素栅极和逻辑栅极的氧化物层与像素阵列基板100之间的界面处)的悬挂键而减少了暗电流。

步骤530包括用氧化物材料和金属(例如钨、铝、钛)中的至少一种填充多个沟槽中的每个沟槽。氧化物材料的示例包括半导体的氧化物(诸如二氧化硅)。在步骤530的示例中,每个外围沟槽260填充有绝缘材料213。当半导体基板210包括外围沟槽265时,步骤530还可以包括用绝缘材料213填充每个外围沟槽265。在步骤530的示例中,在单个步骤(诸如单个沉积步骤(例如,化学气相沉积工艺))中用绝缘材料填充沟槽220、沟槽225和沟槽260(和265,在适用时)中的每一个。此后可以应用化学机械抛光工艺。

特征的组合

上面描述的以及下面要求保护的特征可以以各种方式组合而不脱离其范围。以下列举的示例说明了一些可能的非限制性组合:

(A1)一种像素阵列基板,包括半导体基板和钝化层。半导体基板包括被外围区域包围的像素阵列。半导体基板的背表面在外围区域中形成延伸到半导体基板中的多个第一外围沟槽。钝化层在背表面上并且衬于多个第一外围沟槽中的每个第一外围沟槽。像素阵列包括多个像素。多个像素中的每个像素包括相应的光电二极管区域。

(A2)像素阵列基板(A1)还可以包括多个列间沟槽,每个列间沟槽位于像素阵列的相应的一对相邻像素列之间,相邻的列间沟槽之间的第一距离等于相邻的第一外围沟槽之间的距离。

(A3)在像素阵列基板(A2)中,多个第一外围沟槽中的每个第一外围沟槽可以是多个列间沟槽中的相应列间沟槽的延伸。

(A4)在像素阵列基板(A1)-(A3)中的任何一个中,多个第一外围沟槽中的每个沟槽可以具有相对于包围沟槽的背表面的平面区域超过0.2微米的深度。

(A5)在像素阵列基板(A1)-(A4)中的任何一个中,多个第一外围沟槽中的每个沟槽具有相对于包围沟槽的背表面的平面区域的可以比半导体基板的厚度小0.5微米和2.0微米之间的深度。

(A6)在像素阵列基板(A1)-(A5)中的任何一个中,钝化层的厚度可以在40埃和500埃之间。

(A7)在像素阵列基板(A1)-(A6)中的任何一个中,钝化层可以由高κ材料形成。

(A8)在像素阵列基板(A1)-(A7)中的任何一个中,多个第一外围沟槽中的每个第一外围沟槽可以具有在0.15微米和0.25微米之间的宽度。

(A9)在像素阵列基板(A1)-(A8)中的任何一个中,多个第一外围沟槽中的每个第一外围沟槽可以填充有绝缘材料。

(A10)在像素阵列基板(A1)-(A9)中的任何一个中,背表面还可以在外围区域中形成延伸到半导体基板中的多个第二外围沟槽,多个第二外围沟槽中的每个第二外围沟槽垂直于多个第一外围沟槽中的每个第一外围沟槽。钝化层衬于多个第二外围沟槽中的每个第二外围沟槽。

(A11)像素阵列基板(A10)还可以包括多个行间沟槽,每个行间沟槽位于像素阵列的相应的一对相邻像素行之间,相邻的行间沟槽之间的第二距离等于相邻的第二外围沟槽之间的距离。

(A12)在像素阵列基板(A11)中,多个第二外围沟槽中的每个第二外围沟槽可以是多个行间沟槽中的相应行间沟槽的延伸。

(A13)在像素阵列基板(A11)-(A12)中的任何一个中,多个第二外围沟槽中的每个沟槽具有相对于包围沟槽的背表面的平面区域的可以比半导体基板的厚度小0.5微米和2.0微米之间的深度。

(B1)一种图像传感器,包括像素阵列基板(A1)-(A13)中的任何一个,以及由多个微透镜形成的微透镜阵列,每个微透镜与像素阵列的相应光电二极管区域对准。

用于防止沉积在包括像素阵列的半导体基板上的薄膜中的缺陷的方法(C1)。方法(C1)包括在半导体基板的外围区域上形成多个沟槽以产生带沟槽的表面。外围区域包围像素阵列。带沟槽的表面(i)包括多个沟槽区域,每个沟槽区域形成多个沟槽中的相应沟槽,以及(ii)在每对相邻沟槽之间,包括多个沟槽间表面中的相应沟槽间表面。该方法还包括在表面上沉积薄膜,使得薄膜覆盖每个沟槽间表面并保形地覆盖每个沟槽区域。像素阵列包括多个像素。多个像素中的每个像素包括相应的光电二极管区域。

(C2)在方法(C1)中,形成多个沟槽可以包括光刻蚀刻外围区域的表面,该表面是半导体基板的背表面的一部分。

(C3)方法(C1)和(C2)中的任一个还可以包括对薄膜进行退火并且用氧化物材料和金属中的至少一种填充多个沟槽中的每个沟槽。

(C4)在方法(C1)-(C3)中的任何一个中,在形成多个沟槽的步骤中,多个沟槽中的每个沟槽可以垂直于多个沟槽中的至少一个其他沟槽并与之相交。多个沟槽可以形成网格。

(C5)在方法(C1)-(C4)中的任何一个中,半导体基板包括被外围区域包围的中心区域,并且在形成步骤中,多个沟槽包括多个中心区域沟槽,多个中心区域沟槽各自横穿外围区域和中心区域,并且位于(i)像素阵列的一对相邻像素行之间或(ii)像素阵列的一对相邻像素列之间。

(C6)在方法(C1)-(C5)中的任何一个中,每个沟槽间表面可以是在多个沟槽中的两个相邻沟槽之间的半导体基板的背表面的相应平面区域。

在不脱离本实施例的范围的情况下,可以在以上方法和系统中进行改变。因此应当注意的是,以上描述中包含或附图中所示的内容应当被解释为说明性的,而不是限制性的。在本文中,并且除非另外指出,否则短语“在实施例中”等同于短语“在某些实施例中”,并且并不是指所有实施例。以下权利要求书旨在覆盖本文描述的所有一般和具体特征,以及本方法和系统的范围的所有陈述,就语言而言,可以认为其介于两者之间。