信息处理系统以及信息处理系统的控制方法

文献发布时间:2023-06-19 18:29:06

技术领域

本公开涉及信息处理系统以及信息处理系统的控制方法。

背景技术

近年来,在安装到嵌入系统的处理器中,伴随对应用的复杂化以及高速化的需求高涨,通过提高每一个核的动作频率、多核化、图形处理单元(GPU;Graphics ProcessingUnit)、内置专用加速器等来搭载多个运算器等,谋求提高性能。

另外,作为减少功耗的构造之一的具有动态电压频率控制(DVFS;DynamicVoltage and Frequency Scaling)功能的处理器也得到开发。DVFS功能是通过使处理器具有数种动作频率以及动作电压并根据处理器的负荷状况变更处理器的动作频率以及动作电压的省电机构实现的。

伴随安装于嵌入系统的处理器的进化,吞吐量变大。另一方面,在嵌入系统中,作为必要条件要求散热控制以及装置的小型化。因此,要求满足应用的性能必要条件的同时进行处理器的省电控制。

以往,作为处理器的省电控制,已知:监视处理器的负荷状况,在处理器的负荷状况是高负荷的情况下,使处理器以高的频率动作,在处理器的负荷状况是低负荷的情况下,使处理器以低的频率动作的控制方法。专利文献1提出根据与存储器性能有关的统计信息,在存储器频带宽度在性能方面处于支配地位的情况下进行降低运算能力的控制的方法。专利文献2提出比较中央处理单元(CPU;Central Processing Unit)的运算量和向高速缓存存储器的存取量,在后者处于支配地位的情况下使处理器的省电机构有效的方法。

现有技术文献

专利文献

专利文献1:国际公开第2008/120274号

专利文献2:日本特开2008-40734号公报

发明内容

在由专利文献1提出的方法中,仅在处理器的内部利用与存储器存取有关的统计信息,所以存在无法进行适合于运算应用的算法的具有高的精度的电力性能控制这样的问题。另外,在该方法中,不利用运算应用的运算强度,所以存在在省电控制中产生延迟,特别在需要高的运算性能的情况下,处理器的频率仍低这样的问题。另外,在该方法中,停留在控制处理器的动作频率以及命令发行宽度,所以存在不进行多核的通/断(ON/OFF)控制以及主存储装置的动作频率的控制,无法进行充分的省电控制这样的问题。

在由专利文献2提出的方法中,关于通过计算机执行的执行代码,在CPU的执行比率高的区域中不进行性能电力控制,所以存在在主存储装置中消耗必要以上的电力这样的问题。

本公开是鉴于这些问题而完成的。本公开的目的在于能够进行适合于运算应用的算法的性能电力控制。另外,本公开的目的在于防止性能电力控制的延迟。

本公开涉及信息处理系统。

信息处理系统具备执行块运算强度数据区域、屋顶线模型数据存储部、运算强度数据取得部、以及性能电力控制部。

执行块运算强度数据区域保持构成在具备具有省电机构的处理器以及主存储装置的计算机系统的动作环境下动作的运算应用的各执行块的运算强度数据。

屋顶线模型数据存储部保持与处理器的动作频率和核数以及主存储装置的动作频率对应的屋顶线模型。

运算强度数据取得部从执行块运算强度数据区域取得各执行块的运算强度数据。

性能电力控制部根据屋顶线模型以及各执行块的运算强度数据,进行处理器的动作频率和核数以及主存储装置的动作频率的控制。

本公开还面向信息处理系统的控制方法。

根据本公开,根据构成运算应用的各执行块的运算强度数据进行性能电力控制。由此,能够进行适合于运算应用的算法的性能电力控制。另外,根据预先定义的运算强度数据前馈地进行性能电力控制。由此,能够防止性能电力控制的延迟。

本公开的目的、特征、方案以及优点通过以下的详细的说明和附图将变得更加明确。

附图说明

图1是示意性地图示实施方式1的信息处理系统的硬件结构的框图。

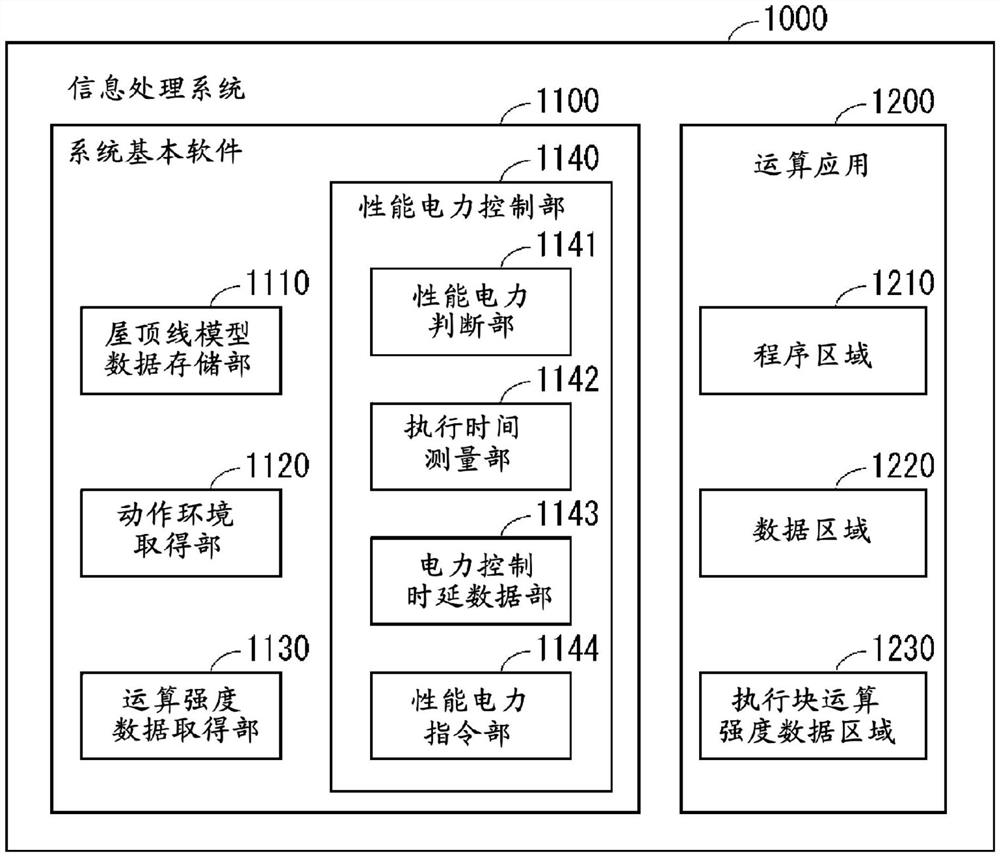

图2是示意性地图示实施方式1的信息处理系统的功能结构的框图。

图3是图示安装于实施方式1的信息处理系统的系统基本软件的动作的流程的流程图。

图4是图示保持于设置于实施方式1的信息处理系统的屋顶线存储部的屋顶线模型的例子的图。

图5是图示构成保持于设置于实施方式1的信息处理系统的屋顶线存储部的屋顶线模型的、处理器的可选择的动作频率以及核数的组合和浮动小数点运算的性能的上限值的关系的图。

图6是图示构成保持于设置于实施方式1的信息处理系统的屋顶线存储部的屋顶线模型的、主存储装置的可选择的动作频率和频带宽度的关系的图。

图7是图示保持于设置于实施方式1的信息处理系统的执行块运算强度数据区域的信息的例子的图。

图8是图示设置于实施方式1的信息处理系统的性能电力判断部的动作的流程的流程图。

图9是图示通过实施方式1的信息处理系统进行的、执行块是存储加强型的情况下的省电控制的方针的例子的图。

图10是图示通过实施方式1的信息处理系统进行的、执行块是运算加强型的情况下的省电控制的方针的例子的图。

图11是图示实施方式1的信息处理系统中的为了进行各控制所花费的开销时间的例子的图。

图12是图示设置于实施方式1的信息处理系统的电力控制时延数据部以及性能电力指令部的动作的过程的图。

图13是图示设置于实施方式2的信息处理系统的性能电力判断部的动作的流程的流程图。

图14是图示通过实施方式2的信息处理系统进行的、执行块是存储加强型的情况下的省电控制的方针的例子的图。

图15是图示通过实施方式2的信息处理系统进行的、执行块是存储加强型的情况下的省电控制的方针的例子的图。

图16是图示通过实施方式2的信息处理系统进行的、执行块是运算加强型的情况下的省电控制的方针的例子的图。

图17是图示通过实施方式2的信息处理系统进行的、执行块是运算加强型的情况下的省电控制的方针的例子的图。

(附图标记说明)

10:计算机系统;11:处理器;12:主存储装置;13:辅助存储装置;1000:信息处理系统;1100:系统基本软件;1200:运算应用;1110:屋顶线模型数据存储部;1120:动作环境取得部;1130:运算强度数据取得部;1140:性能电力控制部;1141:性能电力判断部;1142:执行时间测量部;1143:电力控制时延数据部;1144:性能电力指令部;1210:程序区域;1220:数据区域;1230:执行块运算强度数据区域。

具体实施方式

<实施方式1>

图1是示意性地图示实施方式1的信息处理系统的硬件结构的框图。

如图1图示,实施方式1的信息处理系统1000具备计算机系统10。

如图1图示,在计算机系统10中,具备处理器11、主存储装置12以及辅助存储装置13。

处理器11包括中央处理单元(CPU;Central Processing Unit)、图形处理单元(GPU;Graphics Processing Unit)、数字信号处理器(DSP;Digital Signal Processor)等。处理器11具备省电机构。省电机构动态地变更处理器11的动作频率和/或核数。

主存储装置12是随机存取存储器(RAM;Random Access Memory)等。

辅助存储装置13是硬盘驱动器、固态驱动器、RAM盘等。

图2是示意性地图示实施方式1的信息处理系统的功能结构的框图。

如图2图示,在信息处理系统1000中,安装系统基本软件1100以及运算应用1200。

系统基本软件1100以及运算应用1200在计算机系统10的动作环境下动作。系统基本软件1100也可以是操作系统。对于运算应用1200的算法不存在制约。该算法是进行以恒定周期执行的自动驾驶车辆的车辆控制的算法等。

如图2图示,信息处理系统1000具备屋顶线模型(roofline model)数据存储部1110、动作环境取得部1120、运算强度数据取得部1130以及性能电力控制部1140。这些要素通过由处理器1执行从辅助存储装置13载入到主存储装置12的系统基本软件1100来构成。

屋顶线模型数据存储部1110保持与计算机系统10有关的性能信息。

动作环境取得部1120取得计算机系统10的当前的动作环境。

运算强度数据取得部1130从下述的执行块运算强度数据区域1230,取得构成运算应用1200的各执行块的运算强度数据。

性能电力控制部1140根据保持的性能信息以及取得的各执行块的运算强度数据,进行性能电力控制。

在实施方式1中,保持的与计算机系统10有关的性能信息包括与处理器11的动作频率和核数以及主存储装置12的动作频率对应的屋顶线模型。另外,取得的计算机系统10的当前的动作环境包括处理器11的当前的动作频率和核数以及主存储装置12的当前的动作频率。另外,根据性能信息以及各执行块的运算强度数据进行性能电力控制包括根据包含于性能信息的屋顶线模型以及各执行块的运算强度数据进行处理器11的动作频率和核数以及主存储装置12的动作频率的控制。使用计算机系统10的当前的动作环境包括使用包含于计算机系统10的当前的动作环境的处理器11的当前的动作频率和核数以及主存储装置12的当前的动作频率。

性能电力控制部1140具备性能电力判断部1141、执行时间测量部1142、电力控制时延数据(power control latency data)部1143以及性能电力指令部1144。

性能电力判断部1141根据保持的屋顶线模型以及各执行块的运算强度数据,决定性能电力控制的方针。

执行时间测量部1142测量各执行块的执行时间。

电力控制时延数据部1143根据在使性能电力指令部1144进行性能电力控制的情况下花费的开销时间,判定是否使性能电力指令部1144进行性能电力控制。

性能电力指令部1144依照决定的性能电力控制的方针,输出控制指令。性能电力指令部1144在由电力控制时延数据部1143判定为使性能电力指令部1144进行性能电力控制的情况下,输出控制指令。

在实施方式1中,决定的性能电力控制的方针包括处理器11的动作频率和核数以及主存储装置12的动作频率。另外,依照决定的性能电力控制的方针包括:依照包含于决定的性能电力控制的方针的处理器11的动作频率和核数以及主存储装置12的动作频率。另外,关于输出控制指令,为了进行处理器11的动作频率和核数以及主存储装置12的动作频率的控制而进行。

如图2图示,信息处理系统1000具备程序区域1210、数据区域1220以及执行块运算强度数据区域1230。这些要素确保于主存储装置12以及辅助存储装置13的至少一方。

程序区域1210保持构成运算应用1200的程序。

数据区域1220保持构成运算应用1200的变量、排列等。

执行块运算强度数据区域1230保持构成运算应用1200的各执行块的运算强度数据以及各执行块的截止时间。各执行块的截止时间表示必须结束各执行块的处理的时间。

在信息处理系统1000中,根据构成运算应用1200的各执行块的运算强度数据,进行性能电力控制。由此,能够进行适合于运算应用1200的算法的性能电力控制。

另外,在信息处理系统1000中,根据预先定义的运算强度数据前馈地进行性能电力控制。由此,能够防止性能电力控制的延迟。

另外,在信息处理系统1000中,进行主存储装置12的动作频率的控制。由此,能够抑制由主存储装置12消耗必要以上的电力。

图3是图示安装于实施方式1的信息处理系统的系统基本软件的动作的流程的流程图。

系统基本软件1100执行图3图示的步骤S100至S105。

在步骤S100中,动作环境取得部1120取得计算机系统10的当前的动作环境。此时,动作环境取得部1120取得处理器11的当前的动作频率和核数以及主存储装置12的当前的动作频率。

在接着的步骤S101中,动作环境取得部1120选择与取得的计算机系统10的当前的动作环境对应的屋顶线模型。

根据步骤S100以及S101,能够参照与计算机系统10的当前的动作环境对应的屋顶线模型。

在接着的步骤S102中,运算强度数据取得部1130取得接下来执行的执行块的运算强度数据。

在接着的步骤S103中,性能电力控制部1140对照选择的屋顶线模型和取得的执行块的运算强度数据。另外,性能电力控制部1140选择计算机系统10的动作环境。此时,性能电力控制部1140选择处理器11的动作频率和核数以及主存储装置12的动作频率。

在接着的步骤S104中,性能电力控制部1140判定是否在将计算机系统10的动作环境从当前的动作环境变更为在步骤S103中选择的动作环境的情况下,由于控制延迟,执行块的执行时间超过截止时间。该控制延迟是由于在将计算机系统10的动作环境从当前的动作环境变更为选择的动作环境的情况下发生的开销时间发生的。

性能电力控制部1140在判定为执行块的执行时间超过截止时间的情况下,不执行步骤S105而结束动作。另一方面,性能电力控制部1140在判定为执行块的执行时间不超过截止时间的情况下,在执行步骤S105后结束动作。

在步骤S105中,性能电力控制部1140进行性能电力控制。此时,性能电力控制部1140将处理器11的动作频率和核数以及主存储装置12的动作频率设定为其被选择的值。

图4是图示在设置于实施方式1的信息处理系统的屋顶线存储部中保持的屋顶线模型的例子的图。在该图中,在横轴上示出运算强度。另外,在纵轴上示出浮动小数点运算的性能。

屋顶线模型针对一个计算机系统10存在一个,具有与设置于一个计算机系统10的处理器11以及主存储装置12对应的内容。关于处理器11的可选择的运算性能中的各运算性能以及主存储装置12的可选择的存储器性能中的各存储器性能,屋顶线模型规定针对运算强度的浮动小数点运算的性能的上限值。屋顶线模型也可以规定浮动小数点运算的性能以外的性能的上限值。处理器11的运算性能是处理器11的动作频率以及核数的组合等。主存储装置12的存储器性能是主存储装置12的动作频率等。在处理器11的运算性能是处理器11的动作频率以及核数的组合,主存储装置12的存储器性能是主存储装置12的动作频率的情况下,能够参照与处理器11的动作频率和核数的组合以及主存储装置12的动作频率对应的屋顶线数据。在图4图示的例子中,关于处理器11的可选择的各动作频率“2.6GHz”、“2.4GHz”、“1.8GHz”以及“1.0GHz”以及主存储装置12的与可选择的动作频率对应的各频带宽度“25.4GB/s”、“16.4GB/s”以及“10.6GB/s”,屋顶线模型规定针对运算强度的浮动小数点运算的性能的上限值。根据屋顶线模型,能够根据构成运算应用1200的执行块的运算强度,视觉上判别在执行该执行块时的浮动小数点运算的性能中处理器11的运算性能以及主存储装置12的存储器性能中的哪一个是支配性的。屋顶线模型的详情记载于SamuelWilliams,Andrew Waterman and David Patterson,"Roofline:An Insightful VisualPerformance Model for Floating-Point Programs and Multicore,(2009)"。

图5是图示构成保持于设置于实施方式1的信息处理系统的屋顶线存储部的屋顶线模型的、处理器的可选择的动作频率以及核数的组合和浮动小数点运算的性能的上限值的关系的图。

如上所述,关于处理器11的可选择的运算性能中的各运算性能,屋顶线模型规定针对运算强度的浮动小数点运算的性能的上限值。但是,在关于处理器11的可选择的运算性能中的各运算性能规定的针对运算强度的浮动小数点运算的性能的上限值中,浮动小数点运算的性能的上限值不依赖于运算强度。因此,通过关于处理器11的可选择的运算性能中的各运算性能规定浮动小数点运算的性能的上限值,能够关于处理器11的可选择的运算性能中的各运算性能规定针对运算强度的浮动小数点运算的性能的上限值。例如,通过图5图示的处理器11的可选择的动作频率以及核数的组合和浮动小数点运算的性能的上限值的关系,能够关于处理器11的可选择的动作频率以及核数的组合中的各组合规定针对运算强度的浮动小数点运算的性能的上限值。

图6是图示构成在设置于实施方式1的信息处理系统的屋顶线存储部中保持的屋顶线模型的、主存储装置的可选择的动作频率和频带宽度的关系的图。

如上所述,关于主存储装置12的可选择的存储器性能中的各存储器性能,屋顶线模型规定针对运算强度的浮动小数点运算的性能的上限值。但是,主存储装置12的频带宽度与主存储装置12的动作频率具有1对1的关系。因此,关于可选择的频带宽度中的各频带宽度规定针对运算强度的浮动小数点运算的性能的上限值,准备图6图示的主存储装置的可选择的动作频率和频带宽度的关系,由此能够关于主存储装置12的可选择的动作频率中的各动作频率规定针对运算强度的浮动小数点运算的性能的上限值。

图7是图示在设置于实施方式1的信息处理系统的执行块运算强度数据区域中保持的信息的例子的图。

如图7图示,执行块运算强度数据区域1230保持各执行块的执行地址、各执行块的运算强度数据以及各执行块的截止时间。

根据图7图示的信息,能够进行以更细的粒度考虑了性能以及功耗的性能电力控制。另外,用户无需加工运算应用1200的源代码文件,而能够取得期望的执行块的运算强度数据。

在制作图7图示的信息时,预先制作这样的文件,该文件包括:能够确定执行块的信息和运算强度数据以及截止时间成对的数据。该文件被制作成与运算应用1200的源代码文件独立的文件。能够确定执行块的信息是与执行块相当的函数的名称等。

接下来,进行编译,根据运算应用1200的源代码文件以及制作的文件,制作运算应用1200的执行形式文件。在制作的执行形式文件中采用可执行以及可链接的格式(ELF;Executable and Linkable Format)的情况下,也可以将各执行块的运算强度数据专用的分段(section)在执行形式文件中新设定为执行块运算强度数据区域1230。在该情况下,新设定的分段的信息被追加到ELF头部以及分段头部。

在进行编译时,根据能够确定执行块的信息,确定程序区域1210内的对应的机器语言部分,在确定的机器语言部分中,插入使得发生软件中断的命令。使得发生软件中断的命令在处理器11为x86系处理器的情况下是INT3命令等。使得发生软件中断的命令能够将原来的命令的最初的字节作为断点进行置换。另外,取得确定的机器语言部分的执行地址,将取得的执行地址追加到执行块运算强度数据区域1230。

与这些独立地,在执行运算应用1200之前,将执行包含于性能电力控制部1140的一连串的处理的中断处理器登记到中断描述符表格内的对应的中断编号。

由此,在通过系统基本软件1100将运算应用1200载入到主存储装置12并通过处理器11执行时,每当来到各块时发生软件中断。在UNIX(注册商标)环境中,通过exec存储器,开始运算应用1200的载入以及执行。例如,在使得发生软件中断的命令是INT3命令的情况下,将SIGTRAP信号通知给系统基本软件1100。在系统基本软件1100中,与发生软件中断连动地,起动预先登记于中断描述符表格内的中断处理器,执行包含于性能电力控制部1140的一连串的处理。此时,运算强度数据取得部1130根据各执行块的执行地址,取得各执行块的运算强度数据以及各执行块的截止时间。此时,运算强度数据取得部1130根据当前执行的地址,确定载入于主存储装置12的与该地址对应的执行块,取得确定的执行块的运算强度数据以及该执行块的截止时间。另外,运算强度数据取得部1130将取得的各执行块的运算强度数据以及各执行块的截止时间送给性能电力判断部1141。

图8是图示设置于实施方式1的信息处理系统的性能电力判断部的动作的流程的流程图。

性能电力控制部1140从屋顶线模型数据存储部1110接受与当前的动作环境对应的屋顶线模型,从运算强度数据取得部1130接受接下来执行的执行块的运算强度数据以及截止时间后,执行图8图示的步骤S200至S207。

在步骤S200中,性能电力判断部1141在接受的屋顶线模型上描绘接受的执行块的运算强度数据。另外,性能电力判断部1141对照屋顶线模型和执行块的运算强度数据。

在接着的步骤S201中,性能电力判断部1141判定该执行块是否为存储加强型(memory-intensive)。性能电力判断部1141判定主存储装置12的存储器性能以及处理器11的运算性能的哪一个是运算应用1200的性能方面的限速因素,在判定为主存储装置12的存储器性能是限速因素的情况下,判定为该执行块是存储加强型,在判定为处理器11的运算性能是限速因素的情况下,判定为该执行块并非存储加强型、即判定为是运算加强型。

在判定为该执行块是存储加强型的情况下,执行步骤S202至S204。在判定为该执行块并非存储加强型的情况下,执行步骤S205至S207。

在步骤S202中,性能电力判断部1141提高主存储装置12的动作频率。此时,性能电力判断部1141从在屋顶线模型数据存储部1110中保持的主存储装置12的可选择的动作频率,选择比主存储装置12的当前的动作频率大的动作频率。

在接着的步骤S203中,性能电力判断部1141更新屋顶线模型。此时,性能电力判断部1141根据选择的主存储装置12的动作频率,更新屋顶线模型。

在接着的步骤S204中,性能电力判断部1141以使屋顶线模型的梯度部与屋顶线模型的平坦部之间的不连续点位于运算强度上的方式,降低处理器11的动作频率和/或核数。此时,性能电力判断部1141从在屋顶线模型数据存储部1110中保持的处理器11的可选择的动作频率和/或核数,选择比处理器11的当前的动作频率和/或核数小的动作频率和/或核数。

屋顶线模型的梯度部存在于主存储装置12的存储器性能成为限速因素的运算强度的范围。屋顶线模型的平坦部存在于处理器11的运算性能成为限速因素的运算强度的范围。

在步骤S205中,性能电力判断部1141提高处理器11的动作频率和/或核数。此时,性能电力判断部1141从在屋顶线模型数据存储部1110中保持的处理器11的可选择的动作频率和/或核数,选择比处理器11的当前的动作频率和/或核数大的动作频率和/或核数。

在接着的步骤S206中,性能电力判断部1141更新屋顶线模型。此时,性能电力判断部1141根据选择的处理器11的动作频率和/或核数,更新屋顶线模型。

在接着的步骤S207中,性能电力判断部1141以使屋顶线模型的梯度部与屋顶线模型的平坦部之间的不连续点位于运算强度上的方式,降低主存储装置12的动作频率。此时,性能电力判断部1141从在屋顶线模型数据存储部1110中保持的主存储装置12的可选择的动作频率,选择比主存储装置12的当前的动作频率小的动作频率。

图9是图示通过实施方式1的信息处理系统进行的、执行块是存储加强型的情况下的省电控制的方针的例子的图。

在图9图示的省电控制的方针的例子中,针对由虚线图示的当前的主存储装置12的存储器性能以及处理器11的运算性能,决定将成为执行块被执行时的性能的障碍的主存储装置12的存储器性能提高到由实线梯度部图示的主存储装置12的存储器性能,来满足性能要求。另外,决定以使梯度部与平坦部之间的不连续点位于运算强度上的方式将处理器11的运算性能降低到由实线平坦部图示的处理器11的运算性能,来实现省电化。由此,以使主存储装置12的存储器性能以及处理器11的运算性能转移到由实线图示的主存储装置12的存储器性能以及处理器11的运算性能的方式,选择主存储装置12的存储器性能以及处理器11的运算性能。

图10是图示通过实施方式1的信息处理系统进行的、执行块是运算加强型的情况下的省电控制的方针的例子的图。

在图10图示的省电控制的方针的例子中,针对由虚线图示的当前的主存储装置12的存储器性能以及处理器11的运算性能,决定将成为执行块被执行时的性能的障碍的处理器11的运算性能提高到由实线平坦部图示的处理器11的运算性能,来满足性能要求。另外,决定以使梯度部与平坦部之间的不连续点位于运算强度上的方式将主存储装置12的存储器性能降低到由实线梯度部图示的主存储装置12的存储器性能,来实现省电化。由此,以使主存储装置12的存储器性能以及处理器11的运算性能转移到由实线图示的主存储装置12的存储器性能以及处理器11的运算性能的方式,选择主存储装置12的存储器性能以及处理器11的运算性能。

根据图9以及图10图示的省电控制的方针,能够在满足必要的性能要求的同时进行省电化。

图11是图示实施方式1的信息处理系统中的为了进行各控制所花费的开销时间的例子的图。

预先定义有图11图示的为了进行各控制所花费的开销时间。为了进行该各控制而花费的开销时间包括处理器11的动作频率、处理器11的核的通/断以及主存储装置12的动作频率的控制花费的开销时间。

图12是图示设置于实施方式1的信息处理系统的电力控制时延数据部以及性能电力指令部的动作的过程的图。

如图12图示,与通过系统基本软件1100实施的性能电力控制有关的处理是通过软件中断在执行构成运算应用的各执行块之前执行的。

在执行与通过系统基本软件1100实施的性能电力控制有关的处理之后,执行时间测量部1142通过在该处理的前后取得当前的时刻,能够测量各执行块的执行时间。电力控制时延数据部1143保持测量的各执行块的执行时间。另外,电力控制时延数据部1143根据测量的各执行块的执行时间、和图11图示的为了进行各控制所花费的开销时间,判断是否进行性能电力控制。在实施方式1中,电力控制时延数据部1143在前一个周期中的执行块的执行时间以及开销时间的合计未超过由运算强度数据取得部1130取得的该执行块的截止时间的情况下,将关于该执行块进行性能电力控制的命令输出给性能电力指令部1144。另一方面,在不是这样的情况下,电力控制时延数据部1143将关于该执行块不进行性能电力控制的命令输出给性能电力指令部1144。

由此,能够在遵守各执行块的截止时间的同时,关于各执行块进行性能电力控制。

<实施方式2>

以下,说明实施方式2与实施方式1的不同点。关于未说明的点,在实施方式2中也采用在实施方式1中采用的结构。

在实施方式1中,仅基于构成运算应用1200的各执行块的运算强度数据,根据与计算机系统10的当前的动作环境对应的屋顶线模型来进行性能电力控制。该动作环境是处理器11的动作频率和核数以及主存储装置12的动作频率。但是,执行运算应用1200时的实际的性能未必与通过屋顶线模型表示的计算机系统10的界限性能一致。

因此,在实施方式2中,除了构成运算应用1200的各执行块的运算强度数据以外,还利用执行运算应用1200时的实际的运算性能,由此实现具有更高的精度的性能电力控制。以下,将被利用的该运算性能称为“实际运算性能”。

各执行块的实际运算性能可通过如下方式来求出:将根据由运算强度数据取得部1130取得的各执行块的运算强度数据确定的浮动小数点运算的总数除以由电力控制时延数据部1143保持的各执行块的执行时间。

图13是图示设置于实施方式2的信息处理系统的性能电力判断部的动作的流程的流程图。

性能电力控制部1140执行图13图示的步骤S300至S309。

在步骤S300中,性能电力判断部1141在接受的屋顶线模型上描绘接受的执行块的运算强度数据。另外,性能电力判断部1141对照屋顶线模型和执行块的运算强度数据。

在接着的步骤S301中,性能电力判断部1141判定该执行块是否为存储加强型。

在判定为该执行块是存储加强型的情况下,执行步骤S302至S305。在判定为该执行块并非存储加强型的情况下,执行步骤S306至S309。

在步骤S302中,性能电力判断部1141判定该执行块的实际运算性能是否达到当前的动作环境中的主存储装置12的存储器性能的峰值性能。

在判定为该执行块的实际运算性能达到主存储装置12的存储器性能的峰值性能的情况下,执行步骤S303至S305。在判定为该执行块的实际运算性能未达到存储器性能的峰值性能的情况下,执行步骤S305。

在步骤S303中,性能电力判断部1141提高主存储装置12的动作频率。此时,性能电力判断部1141从在屋顶线模型数据存储部1110中保持的主存储装置12的可选择的动作频率,选择比主存储装置12的当前的动作频率大的动作频率。

在接着的步骤S304中,性能电力判断部1141更新屋顶线模型。此时,性能电力判断部1141根据选择的主存储装置12的动作频率,更新屋顶线模型。

在接着的步骤S305中,性能电力判断部1141以使屋顶线模型的梯度部与屋顶线模型的平坦部之间的不连续点位于运算强度上的方式,降低处理器11的动作频率和/或核数。此时,性能电力判断部1141从在屋顶线模型数据存储部1110中保持的处理器11的可选择的动作频率和/或核数,选择比处理器11的当前的动作频率和/或核数小的动作频率和/或核数。

在步骤S302至S305中,该执行块的实际运算性能未达到主存储装置12的存储器性能的峰值性能的情况下,关于主存储装置12的动作频率,判断为当前的动作环境满足主存储装置12的存储器性能的必要条件,不进行其选择。

在步骤S306中,性能电力判断部1141判定该执行块的实际运算性能是否达到当前的动作环境中的处理器11的运算性能的峰值性能。

在判定为该执行块的实际运算性能达到处理器11的运算性能的峰值性能的情况下,执行步骤S307至S309。在判定为该执行块的实际运算性能未达到处理器11的运算性能的峰值性能的情况下,执行步骤S309。

在步骤S307中,性能电力判断部1141提高处理器11的动作频率和/或核数。此时,性能电力判断部1141从在屋顶线模型数据存储部1110中保持的处理器11的可选择的动作频率和/或核数,选择比处理器11的当前的动作频率和/或核数大的动作频率和/或核数。

在接着的步骤S308中,性能电力判断部1141更新屋顶线模型。此时,性能电力判断部1141根据选择的处理器11的动作频率和/或核数,更新屋顶线模型。

在接着的步骤S309中,性能电力判断部1141以使屋顶线模型的梯度部与屋顶线模型的平坦部之间的不连续点位于运算强度上的方式,降低主存储装置12的动作频率。此时,性能电力判断部1141从在屋顶线模型数据存储部1110中保持的主存储装置12的可选择的动作频率,选择比主存储装置12的当前的动作频率小的动作频率。

在步骤S306至S309中,该执行块的实际运算性能未达到处理器11的运算性能的峰值性能的情况下,关于处理器11的动作频率以及核数,判断为当前的动作环境满足处理器11的运算性能的必要条件,不进行其选择。

图14以及图15是图示通过实施方式2的信息处理系统进行的、执行块是存储加强型的情况下的省电控制的方针的例子的图。

在图14图示的省电控制的方针的例子中,该执行块的实际运算性能达到当前的动作环境中的主存储装置12的存储器性能的峰值性能。因此,将成为执行该执行块时的性能的障碍的主存储装置12的存储器性能提高到由实线梯度部图示的存储器性能,来满足性能要求。另外,以使梯度部与平坦部之间的不连续点位于运算强度上的方式,将处理器11的运算性能降低到由实线平坦部图示的运算性能,来实现省电化。由此,主存储装置12的存储器性能以及处理器11的运算性能转移到由实线图示的各性能。

在图15图示的省电控制的方针的例子中,该执行块的实际运算性能未达到当前的动作环境中的主存储装置12的存储器性能的峰值性能。因此,维持未成为执行该执行块时的性能的障碍的主存储装置12的存储器性能。另外,以使梯度部与平坦部之间的不连续点位于运算强度上的方式,将处理器11的运算性能降低到由实线平坦部图示的处理器11的运算性能,来实现省电化。由此,主存储装置12的存储器性能以及处理器11的运算性能转移到由实线图示的各性能。

图16以及图17是图示通过实施方式2的信息处理系统进行的、执行块是运算加强型的情况下的省电控制的方针的例子的图。

在图16图示的省电控制的方针的例子中,该执行块的实际运算性能达到当前的动作环境中的处理器11的运算性能的峰值性能。因此,将成为执行该执行块时的性能的障碍的处理器11的运算性能提高到由实线平坦部图示的处理器11的运算性能,来满足性能要求。另外,以使梯度部与平坦部之间的不连续点位于运算强度上的方式,将主存储装置12的存储器性能降低到由实线梯度部图示的主存储装置12的存储器性能,来实现省电化。由此,主存储装置12的存储器性能以及处理器11的运算性能转移到由实线图示的各性能。

在图17图示的省电控制的方针的例子中,该执行块的实际运算性能未达到当前的动作环境中的处理器11的运算性能的峰值性能。因此,维持未成为执行该执行块时的性能的障碍的处理器11的运算性能。另外,以使梯度部与平坦部之间的不连续点位于运算强度上的方式,将主存储装置12的存储器性能降低到由实线梯度部图示的主存储装置12的存储器性能,来实现省电化。由此,主存储装置12的存储器性能以及处理器11的运算性能转移到由实线图示的各性能。

此外,能够自由地组合各实施方式,或者使各实施方式适宜地变形、省略。

虽然详细说明了实施方式,但上述说明在所有方案中仅为例示,实施方式不限于此。应理解可设想未例示的无数的变形例。

- 低压智能配电网络信息处理系统及其控制方法

- 信息处理系统、用于控制信息处理系统的控制方法和程序

- 信息处理系统、控制设备和控制信息处理系统的方法