快速选择输出的现场可编程门阵列芯片与设置方法

文献发布时间:2023-06-19 18:32:25

技术领域

本申请属于现场可编程门阵列(Field programmable gate array,FPGA)领域,涉及利用FPGA外部的测试仪器快速检测被测装置的方法。

背景技术

在FPGA原型验证阶段,经常有需要用外部的测试仪器(例如示波器或者逻辑分析仪)查看并分析端口信号或焊垫(pad)上波形。在FPGA内的被测装置(device under test,DUT)可能具有不同的硅产品知识产权(silicon intellectual property,SIP,以下简称为IP)的多个模块,需要对不同的IP的输出端口的信号进行外部测试。在调试时,也可能需要根据调试状态,经常变换查看不同的端口信号,频繁的切换,给测试带来不便。

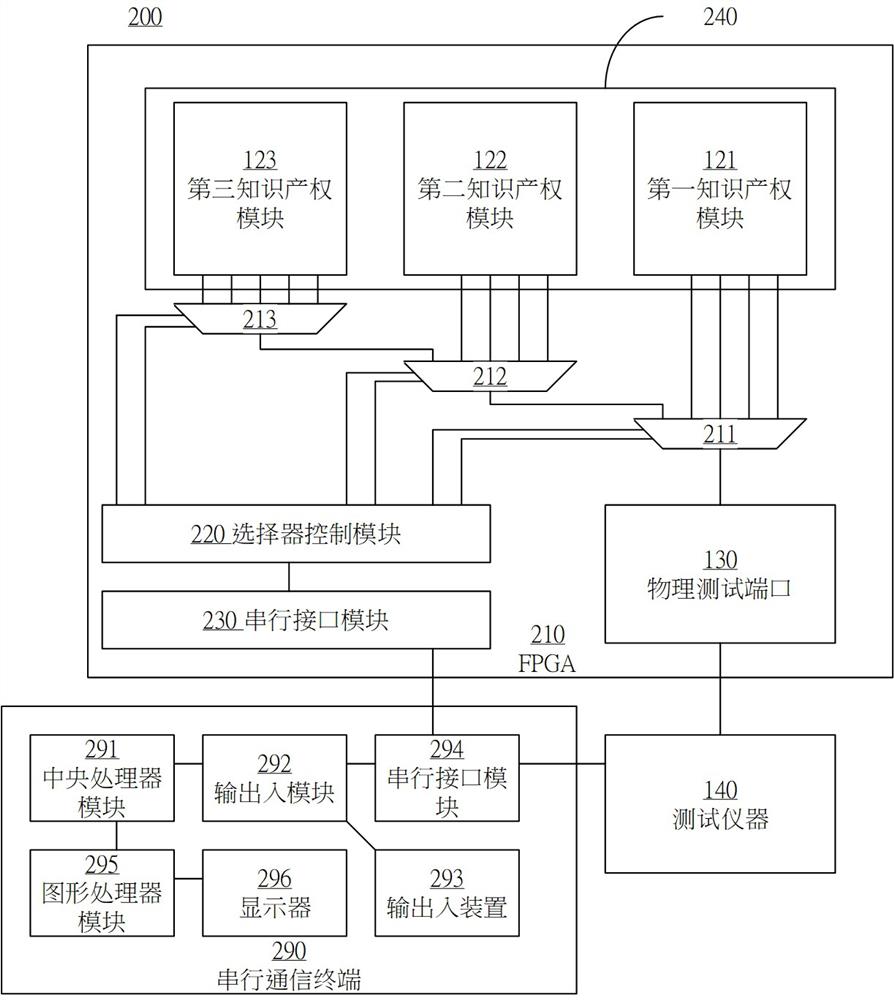

请参考图1A所示,其为现有技术中利用外部的测试仪器对FPGA进行验证的系统100的方块示意图。在图1A的验证系统100当中,包含一个FPGA芯片110。在FPGA芯片当中,烧录有一个被测装置120。该被测装置120可以包含不同的IP模块。如图1A所示,该被测装置120包含了三个IP模块,分别是第一知识产权模块121、第二知识产权模块122、第三知识产权模块123。

每一个知识产权模块可以具备特定的一或多个功能。在本申请当中,也可以将具有某些相关功能的逻辑电路模块,称为功能模块。虽然知识产权模块的定义可能更加具体化,其实施方式也可能已经针对芯片制造厂的设备与制程做出特化,但申请人认为本领域普通技术人员可以理解到,在FPGA芯片的知识产权模块与功能模块是可以互通、互用、互换的,都指涉具有某些功能的逻辑电路模块。

要测试具有某些功能的逻辑电路模块,必然需要将该模块的某一个或某些输出信号引出到FPGA芯片之外,连接到测试仪器进行调试。如图1A所示,FPGA芯片110内部具有一个以上的用于物理测试端口(port)130,该端口130可以透过焊垫与管脚(pin),连接到FPGA芯片110外部的测试仪器140。

在图1A所示的验证系统100当中,测试人员所欲测试的是第一知识产权模块121的输出信号,因此将该第一知识产权模块121的输出连接到用于物理测试该端口130。然而,当测试人员想要改测第二知识产权模块122的输出信号时,必须透过重新烧录来调整端口130所连接的输出信号。

如图1B所示,其为现有技术中利用外部的测试仪器对FPGA进行验证的系统100的方块示意图。从图1A改换成图1B的连接方式,需要放弃原有的部分端口信号,且变更一次需要重新综合成生FPGA bit文件,根据FPGA芯片的不同规模,短则数小时,长则十几小时,时间成本也较大。

由于调试需要频繁地烧录FPGA芯片,因此亟需一种在不修改原有各功能模块连接逻辑的基础上,就可以透过设置指令引导被测装置内部的输出信号接到外部的测试仪器,以便观察其输出信号的波形、时序和/或分析其逻辑状态。

发明内容

本申请是为了解决现有技术中的不足而提出的一种快速选择输出以连接外部测试仪器的FPGA芯片,目的是在不修改原有各功能模块连接逻辑的基础上,就可以透过设置指令引导被测装置内部的输出信号接到外部的测试仪器,以便观察其输出信号的波形、时序和/或分析其逻辑状态。

为了实现上述目的,本申请采用了如下技术方案:

根据本申请实施例,提供一种快速选择连接外部测试仪器的FPGA芯片,其特征在于,包含:用于连接该FPGA芯片外部的测试仪器的物理测试端口;多个功能模块,分别包含提供不同功能的逻辑电路与多个输出;选择器结构,包含M级的选择器,每一个该选择器包含多个输入埠与一个选择器输出,每一个该选择器根据选择输入信号将该多个输入埠之一连接到该选择器输出,该多个功能模块的该多个输出分别连接到该M级的选择器的该多个输入埠之一,其中第i级选择器的输出连接到第i-1级选择器的该多个输入埠之预设输入埠,其中1 较佳地,为了持续输出信号至该测试仪器,其特征在于,其中该第1级选择器的致能输入信号固定连接到表示启动的电位。 较佳地,为了方便设置选择器的选择输入信号,其特征在于,其中该选择器控制模块更包含对应到每一个该选择器的选择信号寄存器,每一个该选择器的该选择输入信号是来自于所对应的该选择信号寄存器的内容。 较佳地,为了简化选择器结构的设计,其特征在于,其中每一个该选择器都具有N个该输入埠,N为大于1的正整数。 较佳地,为了适应不同形式的连接指令,其特征在于,其中该连接指令包含指定所有该输入埠其中的第x个输入埠,该选择器控制模块选择该第1级至第k-1级选择器的该预设输入埠与该第k级选择器的第j个输入埠,其中1 较佳地,为了让每一个功能模块对应到一个选择器,其特征在于,其中该多个功能模块中的第x个功能模块的该多个输出分别连接到该M级的选择器中的第x个选择器的该多个输入埠,其中1<=x<=M,x为正整数。 较佳地,为了适应不同形式的连接指令,其特征在于,其中该连接指令包含指定该多个功能模块中的第k个功能模块的第j个输出,该选择器控制模块选择该第1级至第k-1级选择器的该预设输入埠与该第k级选择器的第j个输入埠,其中1 较佳地,为了适应不同的功能模块具有不同数量的输出,其特征在于,其中上述的第i级选择器具有N 较佳地,为了确保测试仪器不会在选择的期间收到错误的输出信号,其特征在于,其中该选择器控制模块在选择该M级的选择器的该多个输入埠的其中之一之前,先将该M级的选择器分别对应的致能输入信号设置为关闭;以及该选择器控制模块在选择该M级的选择器的该多个输入埠的其中之一之后,将该第1级至该第k级选择器分别对应的致能输入信号设置为启动。 较佳地,为了方便设置选择器的致能输入信号,其特征在于,其中该选择器控制模块更包含对应到每一个该选择器的致能信号寄存器,每一个该选择器的该致能输入信号是来自于所对应的该致能信号寄存器的内容。 根据本申请实施例,提供一种快速选择输出以连接外部测试仪器的FPGA芯片的逻辑电路,其特征在于,包含上述的选择器结构、串行接口模块以及选择器控制模块。 根据本申请实施例,提供一种快速选择输出以连接外部测试仪器的FPGA芯片的设置方法,其中该FPGA芯片包含用于连接该FPGA芯片外部的测试仪器的物理测试端口;多个功能模块,分别包含提供不同功能的逻辑电路与多个输出;选择器结构,包含M级的选择器,每一个该选择器包含多个输入埠与一个选择器输出,每一个该选择器根据选择输入信号将该多个输入埠之一连接到该选择器输出,该多个功能模块的该多个输出分别连接到该M级的选择器的该多个输入埠之一,其中第i级选择器的输出连接到第i-1级选择器的该多个输入埠之预设输入埠,其中1 较佳地,为了简化选择器结构的设计,其特征在于,其中每一个该选择器都具有N个该输入埠,N为大于1的正整数,其中该连接指令包含指定所有该输入埠其中的第x个输入埠,其中上述的选择该M级的选择器的所有该输入埠的其中之一为该第k级选择器的第j个输入埠,其中1 较佳地,为了让每一个功能模块对应到一个选择器,其中该多个功能模块中的第x个功能模块的该多个输出分别连接到该M级的选择器中的第x个选择器的该多个输入埠,其中1<=x<=M,x为正整数,其中该连接指令包含指定该多个功能模块中的第k个功能模块的第j个输出,其特征在于,其中上述的选择该M级的选择器的所有该输入埠的其中之一为该第k级选择器的第j个输入埠,其中1<=k<=M,k为正整数,j为正整数,该设置方法更包含:选择该第1级至第k-1级选择器的该预设输入埠与该第k级选择器的第j个输入埠。 较佳地,为了简化设置选择输入信号的过程,其特征在于,更包含:将对应到该第i个选择器的选择信号寄存器的内容设置为对应到j。 较佳地,为了适应不同的功能模块具有不同数量的输出,其特征在于,其中上述的第i级选择器具有N 较佳地,为了确保测试仪器不会在选择的期间收到错误的输出信号,其特征在于,在上述的选择该M级的选择器的该多个输入埠的其中之一之前,先将该M级的选择器分别对应的致能输入信号设置为关闭;以及在上述的选择该M级的选择器的该多个输入埠的其中之一之后,将该第1级至该第k级选择器分别对应的致能输入信号设置为启动。 较佳地,为了简化设置致能输入信号的过程,其特征在于,其中上述的将该M级的选择器的致能输入信号设置为关闭的步骤更包含:将对应到该第M个选择器所分别对应的致能信号寄存器的内容设置为关闭;以及上述的将该第1级至该第k级选择器的致能输入信号设置为启动的步骤更包含:将对应到该第k个选择器所分别对应的致能信号寄存器的内容设置为启动。 由于采用上述方案,本申请的有益效果为: 一、物理测试端口与测试仪器之间的连接关系是固定的,不需要频繁地为测试仪器跳接线路进行操作。 二、降低了选择器结构的复杂度,便于在FPGA芯片的设计选择器结构,降低设计FPGA芯片的综合难度。 三、被测试的多个输出可以依照功能模块或IP模块进行分类,便于查表测试。 四、不受到单一个选择器的规模限制,可以依照需求不断地在旧设计上迭加新的功能模块或IP模块,只需要简单地迭加新的选择器在旧的选择器结构之上。 五、可以利用寄存器来控制每一个选择器的选择信号与致能信号的配置,方便灵活操作,无须额外的设备,降低测试的时间与成本。 附图说明 图1A为现有技术中利用外部的测试仪器对FPGA进行验证的系统100的方块示意图。 图1B为现有技术中利用外部的测试仪器对FPGA进行验证的系统100的方块示意图。 图2为根据本申请实施例的FPGA芯片验证系统200的方块示意图。 图3为根据本申请实施例的选择器300的示意图。 图4为根据本申请实施例的FPGA芯片连接外部物理测试端口的设置方法400的流程示意图。 图5为根据本申请实施例的步骤420的更详细的流程示意图。 图6为根据本申请实施例的步骤420的更详细的流程示意图。 图7为根据本申请实施例的步骤420的更详细的流程示意图。 具体实施方式 下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所得到的所有其它实施方式,都属于本申请所保护的范围。 本申请之说明书和权利要求以及图式中的术语“第一”“第二”“第三”等(如果存在)用于区别类似之对象,而不必用于描述特定的顺序或先后次序。应当理解,该等描述之对象在适当情况下可以互换。在本申请之描述中,“复数个”之含义是两个或两个以上,除非另有明确具体地限定。此外,术语“包括”和“具有”以及它们的任何变形,意图在于覆盖不排它的包含。图式中所示的一些方框图是功能实体,不一定必须与物理或逻辑上独立的实体相对应。可以采用软件形式来实现该等功能实体,或在一个或复数个硬件电路或集成电路中实现该等功能实体,或在不同网络和/或处理器装置和/或微控制器装置中实现该等功能实体。 在本申请之描述中,需要理解的是,术语“中心”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示之方位或位置关系为基于附图所示之方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指之装置或组件必须具有特定之方位、以特定之方位构造和操作,是故不能理解为对本申请之限制。 在本申请之描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,亦可以为可拆卸连接,或一体地连接;可以为机械连接,亦可以为电连接或可以相互通讯;可以为直接相连,亦可以藉由中间媒介间接相连,可以为两个组件内部之连通或两个组件之相互作用关系。对于本领域之普通技术人员而言,可以根据具体情况理解前述术语在本申请中之具体含义。 为使本申请之目的、特征和优点能够更加明显易懂,下面结合图式和具体实施方式对本申请作进一步详细之说明。 请参考图2所示,其为根据本申请实施例的FPGA芯片验证系统200的方块示意图。该FPGA芯片验证系统200包含一个FPGA芯片210,其内含一个被测装置240。和图1A和图1B所示的被测装置120一样,该被测装置240包含有彼此互连的第一知识产权模块121、第二知识产权模块122、第三知识产权模块123。同样地,和图1A和图1B所示的FPGA芯片110一样,该FPGA芯片110包含用于物理测试的端口130。该端口130可以透过焊垫与管脚,连接到FPGA芯片110外部的测试仪器140(例如示波器或者逻辑分析仪)。 该FPGA芯片210可以包含多层级的选择器结构、负责控制该选择器结构的选择器控制模块220、与连接到外部串行通信终端290的串行接口模块230。如图2所示的实施例,该FPGA芯片210包含三级的选择器结构。本领域普通技术人员可以理解到该选择器结构可以包含M级的选择器,每一级只有一个选择器,M为大于1的正整数。M级的选择器结构包含第一级至第M级的选择器。第一级的选择器211的输出信号连接到上述的端口130。除此之外,其余的第i级选择器的输出信号连接到第i-1级选择器的多个输入埠其中之一,其中1 < i <=M,i为正整数。 在一实施例当中,为了方便设计起见,所有各级的选择器可以具有相同数量的输入埠。举例来说,每一级的选择器皆具有N个输入埠,N为大于1的正整数。每一个选择器包含第一个至第N个输入埠。 在另一个实施例当中,任两个选择器可以具有不同数量的输入埠。举例来说,每一级选择器的输入埠数量可以表示为大于1的正整数N 在该实施例当中,某一个选择器对应到一个IP模块或功能模块。因此,该选择器的Ni个输入埠当中,有Ni-1个输入埠连接到对应的IP模块的输出,剩下的一个输入埠连接到下一级选择器的输出。 当被测装置240在调试过程当中,新增了一个IP模块时,可以在原本的M级的选择器结构当中,新增一个第M+1级的选择器,其具有N 请参考图3所示,其为根据本申请实施例的选择器300的示意图。该选择器300可以是烧录在FPGA芯片内的逻辑电路。该选择器300具有单一个输出330与N个输入埠340,自输入埠340-1至340-N,其中N为大于1的正整数。 该选择器300具有另外两个控制输入,其分别为致能输入信号(EN) 320与选择输入信号(SEL) 310。当致能输入信号320为启动(asserted)时,选择器300会进入工作状态,将被选择的输入埠340所收到的信号传送到输出330。当致能输入信号320为关闭时,选择器300会进入闲置不工作的状态,较为省电节能。 该选择输入信号310用于选择该N个输入埠340其中之一。在某些实施例当中,可以令N个输入埠340当中的第一个输入埠340-1用于连接下一级选择器的输出信号330。在另一个实施例当中,可以令N个输入埠340当中的最后一个输入埠340-N用于连接下一级选择器的输出信号330。 在一些实施例当中,用于连接下一级选择器的输出信号330的输出端口340可以是预设的输出埠340。当重新接电并且收到代表启动的致能输入信号320之后,选择器300会选定预设的输出埠340。在另一些实施例当中,可以在该选择输入信号310输入代表清除(clear)选择的信号,选择器300会选定预设的输出埠340。 在某些实施例当中,每一级选择器300可以对应到一个选择信号寄存器。该选择输入信号320用于连接到该选择信号寄存器,选择器300根据其内容来选择多个输入埠340的其中之一。在某些实施例当中,每一级选择器300可以对应到一个致能信号寄存器。该致能输入信号310用于连接到该致能信号寄存器,选择器300根据其内容来选择启动或关闭本身。 回到图2,选择器控制模块220用于连接每一级选择器的选择输入信号310与致能输入信号320,例如选择器211、212与213。在某些实施例当中,可以省略连接第一级选择器211的致能输入信号320,因为其余各级选择器都要依赖第一级选择器211,所以该第一级选择器211可以保持在工作状态,其致能输入信号320可以持续地连接到启动电位。选择器控制模块220可以设置每一级选择器对应的选择信号寄存器的内容,就如同透过选择输入信号310控制该选择器的输入埠选择一般。 该选择器控制模块220可以透过该串行接口模块230,自串行通信终端290接收测试人员的连接指令。在该连接指令的参数组当中,包含了要连接哪一个IP模块的哪一个输出到该端口130或该测试仪器140。因此,该选择器控制模块220可以保持一张对照表,用于对照参数组内的参数,以便设置各级选择器的选择输入信号310(或选择信号寄存器)与致能输入信号320。 在某些实施例当中,每一级选择器完全对应到某一个IP模块时,该连接指令的参数组可以包含两个参数。第一个参数用于指定某一个IP模块,亦即隐含地指定某一级选择器。第二个参数用于指定该IP模块的某一个输出。 在另一些实施例当中,该连接指令的参数组可以包含两个参数。第一个参数用于指定某一级选择器。第二个参数用于指定该选择器的某一个输入。 在其他实施例当中,当M级选择器中的每一个选择器的输入埠数量皆为N时,这个选择器结构总共具有M x N个输入埠,其序号是从1到M x N。因此,该连接指令的参数组可以包含一个输入埠序号作为参数。 在一些实施例当中,每一个IP模块的每一个输出都具有名称,该对照表包含每一个输出名称与其对应的选择器和对应的输入埠。该连接指令的参数组可以包含一个输出名称。 对照表可以位在非佚失性(non-volatile)的存储器内,该选择器控制模块220可以存取该存储器内的对照表,进而得到对应的选择器与输入埠。另一种做法是,该对照表可以被烧录为FPGA芯片210当中的一种逻辑电路,该选择器控制模块220可以将参数组输入该逻辑电路,而得到对应的选择器与输入埠。 该串行接口模块230利用串行接口与串行通信终端290进行通信。该串行接口可以是符合工业串行接口标准的UART (RS-232、RS-422、RS-423、RS-485)、IEEE 1394、SerialSCSI、USB系列接口,也可以是自定义规格的串行(serial)接口。本申请并不限定该串行接口的形式。 该串行通信终端290可以是具有人机接口的计算器,例如桌上型计算器、膝上型计算器、可携型计算器、平板型计算器、智能手机、智能个人数字助理等。该串行通信终端290可以包含中央处理器模块291,其包含至少一个中央处理器芯片,用于执行操作系统(Operating System)与在该操作系统上运行的应用程序(Application),以便控制该串行通信终端290。该操作系统可以如市面上的UNIX系列的操作系统(LINUX、Harmony、MacOS、HP-UX、AIX)、窗口系列操作系统或其他种类的实时(real-time)操作系统。本申请并不限定该串行通信终端290的中央处理器与操作系统的型式。 该串行通信终端290可以包含图形处理器模块295与显示器296,用于显示操作系统与应用程序的内容。该串行通信终端290可以包含输出入模块292,其使用工业标准总线或接口来连接各种输出入装置293。例如,该输出入模块292可以是PCI、PCI-Express、SCSI、serial SCSI、或USB等总线控制器。该输出入装置293可以包含键盘、鼠标、触摸板、轨迹球、触控屏幕、麦克风、摄像头、有线或无线网络连接装置等。该串行接口模块294可以是符合工业串行接口标准的UART (RS-232、RS-422、RS-423、RS-485)、IEEE 1394、Serial SCSI、USB系列接口,也可以是自定义规格的串行(serial)接口,其用于和该FPGA芯片210的该串行接口模块230彼此连接。 测试人员可以透过该输出入装置293,例如键盘、触摸板、鼠标、轨迹球等输入设备,将连接指令输入到该串行通信终端290。接着,该串行通信终端290可以将该连接指令透过该串行接口模块294与230,传送到该选择器逻辑电路220。然后,该选择器逻辑电路220可以根据上述的对照表,对选择器结构内的各级选择器进行设置。 在图2所示的实施例当中,该测试仪器140也可以透过该串行接口模块294连接到该串行通信终端290。在某些实施例当中,当该测试仪器140开始自该物理测试端口130取得信号的波形或其他数据时,该测试仪器140会透过该串行接口模块294通知该串行通信终端290所执行的软件。举例来说,逻辑分析仪可以将所接收到的信号的逻辑状态依序传送到该串行通信终端290。 请参考图4所示,其为根据本申请实施例的FPGA芯片连接外部物理测试端口的设置方法400的流程示意图。该设置方法400可以适用于图2所示的FPGA芯片验证系统200,特别是由选择器控制模块220来实现该控制方法400。当任两个步骤之间没有因果关系时,本申请并不限定这两个步骤执行顺序。控制方法400自步骤410开始。 步骤410:自串行接口模块,接收来自串行通信终端的连接指令。 步骤420:根据对照表,找出该连接指令的参数组对应到选择器结构的第k级选择器的第j个输入埠,其中1 可选的步骤425:将第1级至第M级选择器的致能输入信号设置为关闭。这是为了预防在选择新的输入时,测试仪器收到错误的信号输出,所以先把选择器结构全部关闭。 步骤430:将第1级至第k-1级选择器的选择输入信号设置为默认输入埠,将该第k级选择器的选择输入信号设置为该第j个输入埠。 步骤440:将该第1级至该第k级选择器的致能输入信号设置为启动。为了省电的缘故,步骤440还可以包含将第k+1级至第M级选择器的致能输入信号设置为关闭。 步骤:450:当完成步骤430与440之后,透过该串行接口模块,回传设置成功的讯息至该串行通信终端。 在其他的实施例当中,当步骤420找不到对应的选择器或输出埠时,可以透过该串行接口模块,回传参数组错误的讯息至该串行通信终端。 请参考图5所示,其为根据本申请实施例的步骤420的更详细的流程示意图。当任两个步骤之间没有因果关系时,本申请并不限定这两个步骤执行顺序。步骤510:根据该对照表的第一部分,找出该参数组的功能模块参数对应到该第k个选择器。步骤520:根据该对照表的第二部分,找出该参数组的功能模块的输出端口参数对应到该第k个选择器的该第j个输入埠。 请参考图6所示,其为根据本申请实施例的步骤420的更详细的流程示意图。当任两个步骤之间没有因果关系时,本申请并不限定这两个步骤执行顺序。步骤610:找出该参数组当中的该第k个选择器。步骤620:找出该参数组当中的该第j个输入埠。 请参考图7所示,其为根据本申请实施例的步骤420的更详细的流程示意图。当任两个步骤之间没有因果关系时,本申请并不限定这两个步骤执行顺序。步骤710:根据该选择器结构中每一个选择器都具有N个输入埠,找出该参数组的第x个输入埠与N的商数所对应的该第k级选择器。步骤720:找出该参数组的该第x个输入埠与N的余数所对应的该第j个输入埠。 根据本申请实施例,提供一种快速选择连接外部测试仪器的FPGA芯片,其特征在于,包含:用于连接该FPGA芯片外部的测试仪器的物理测试端口;多个功能模块,分别包含提供不同功能的逻辑电路与多个输出;选择器结构,包含M级的选择器,每一个该选择器包含多个输入埠与一个选择器输出,每一个该选择器根据选择输入信号将该多个输入埠之一连接到该选择器输出,该多个功能模块的该多个输出分别连接到该M级的选择器的该多个输入埠之一,其中第i级选择器的输出连接到第i-1级选择器的该多个输入埠之预设输入埠,其中1 较佳地,为了持续输出信号至该测试仪器,其特征在于,其中该第1级选择器的致能输入信号固定连接到表示启动的电位。 较佳地,为了方便设置选择器的选择输入信号,其特征在于,其中该选择器控制模块更包含对应到每一个该选择器的选择信号寄存器,每一个该选择器的该选择输入信号是来自于所对应的该选择信号寄存器的内容。 较佳地,为了简化选择器结构的设计,其特征在于,其中每一个该选择器都具有N个该输入埠,N为大于1的正整数。 较佳地,为了适应不同形式的连接指令,其特征在于,其中该连接指令包含指定所有该输入埠其中的第x个输入埠,该选择器控制模块选择该第1级至第k-1级选择器的该预设输入埠与该第k级选择器的第j个输入埠,其中1 较佳地,为了让每一个功能模块对应到一个选择器,其特征在于,其中该多个功能模块中的第x个功能模块的该多个输出分别连接到该M级的选择器中的第x个选择器的该多个输入埠,其中1<=x<=M,x为正整数。 较佳地,为了适应不同形式的连接指令,其特征在于,其中该连接指令包含指定该多个功能模块中的第k个功能模块的第j个输出,该选择器控制模块选择该第1级至第k-1级选择器的该预设输入埠与该第k级选择器的第j个输入埠,其中1 较佳地,为了适应不同的功能模块具有不同数量的输出,其特征在于,其中上述的第i级选择器具有N 较佳地,为了确保测试仪器不会在选择的期间收到错误的输出信号,其特征在于,其中该选择器控制模块在选择该M级的选择器的该多个输入埠的其中之一之前,先将该M级的选择器分别对应的致能输入信号设置为关闭;以及该选择器控制模块在选择该M级的选择器的该多个输入埠的其中之一之后,将该第1级至该第k级选择器分别对应的致能输入信号设置为启动。 较佳地,为了方便设置选择器的致能输入信号,其特征在于,其中该选择器控制模块更包含对应到每一个该选择器的致能信号寄存器,每一个该选择器的该致能输入信号是来自于所对应的该致能信号寄存器的内容。 根据本申请实施例,提供一种快速选择输出以连接外部测试仪器的FPGA芯片的逻辑电路,其特征在于,包含上述的选择器结构、串行接口模块以及选择器控制模块。 根据本申请实施例,提供一种快速选择输出以连接外部测试仪器的FPGA芯片的设置方法,其中该FPGA芯片包含用于连接该FPGA芯片外部的测试仪器的物理测试端口;多个功能模块,分别包含提供不同功能的逻辑电路与多个输出;选择器结构,包含M级的选择器,每一个该选择器包含多个输入埠与一个选择器输出,每一个该选择器根据选择输入信号将该多个输入埠之一连接到该选择器输出,该多个功能模块的该多个输出分别连接到该M级的选择器的该多个输入埠之一,其中第i级选择器的输出连接到第i-1级选择器的该多个输入埠之预设输入埠,其中1 较佳地,为了简化选择器结构的设计,其特征在于,其中每一个该选择器都具有N个该输入埠,N为大于1的正整数,其中该连接指令包含指定所有该输入埠其中的第x个输入埠,其中上述的选择该M级的选择器的所有该输入埠的其中之一为该第k级选择器的第j个输入埠,其中1 较佳地,为了让每一个功能模块对应到一个选择器,其中该多个功能模块中的第x个功能模块的该多个输出分别连接到该M级的选择器中的第x个选择器的该多个输入埠,其中1<=x<=M,x为正整数,其中该连接指令包含指定该多个功能模块中的第k个功能模块的第j个输出,其特征在于,其中上述的选择该M级的选择器的所有该输入埠的其中之一为该第k级选择器的第j个输入埠,其中1<=k<=M,k为正整数,j为正整数,该设置方法更包含:选择该第1级至第k-1级选择器的该预设输入埠与该第k级选择器的第j个输入埠。 较佳地,为了简化设置选择输入信号的过程,其特征在于,更包含:将对应到该第i个选择器的选择信号寄存器的内容设置为对应到j。 较佳地,为了适应不同的功能模块具有不同数量的输出,其特征在于,其中上述的第i级选择器具有N 较佳地,为了确保测试仪器不会在选择的期间收到错误的输出信号,其特征在于,在上述的选择该M级的选择器的该多个输入埠的其中之一之前,先将该M级的选择器分别对应的致能输入信号设置为关闭;以及在上述的选择该M级的选择器的该多个输入埠的其中之一之后,将该第1级至该第k级选择器分别对应的致能输入信号设置为启动。 较佳地,为了简化设置致能输入信号的过程,其特征在于,其中上述的将该M级的选择器的致能输入信号设置为关闭的步骤更包含:将对应到该第M个选择器所分别对应的致能信号寄存器的内容设置为关闭;以及上述的将该第1级至该第k级选择器的致能输入信号设置为启动的步骤更包含:将对应到该第k个选择器所分别对应的致能信号寄存器的内容设置为启动。 本申请具有数个优点,包含了: 一、物理测试端口与测试仪器之间的连接关系是固定的,不需要频繁地为测试仪器跳接线路进行操作。 二、降低了选择器结构的复杂度,便于在FPGA芯片的设计选择器结构,降低设计FPGA芯片的综合难度。 三、被测试的多个输出可以依照功能模块或IP模块进行分类,便于查表测试。 四、不受到单一个选择器的规模限制,可以依照需求不断地在旧设计上迭加新的功能模块或IP模块,只需要简单地迭加新的选择器在旧的选择器结构之上。 五、可以利用寄存器来控制每一个选择器的选择信号与致能信号的配置,方便灵活操作,无须额外的设备,降低测试的时间与成本。 以上所述,仅为本申请较佳的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,根据本申请的技术方案及其申请构思加以等同替换或改变,都应涵盖在本申请的保护范围之内。

- 配置现场可编程门阵列的装置及方法、现场可编程门阵列

- 配置现场可编程门阵列的装置及方法、现场可编程门阵列