碳化硅金属氧化物半导体闸极式半导体装置

文献发布时间:2023-06-19 19:07:35

技术领域

本发明关于一种碳化硅半导体装置,且特别关于一种碳化硅金属氧化物半导体闸极式(MOS-gated)半导体装置。

背景技术

碳化硅(Silicon Carbide,SiC)是新兴的功率半导体材料。由于碳化硅的宽能带间隙而具有优于传统硅功率装置的优越性能,包括对电场的高介电强度及低本质载子浓度。

碳化硅的高介电强度使漂移层的理论单极性特征导通电阻远低于硅的极限,而低的本质载子浓度则使碳化硅功率装置在高温下仍可稳定运作。

为了满足对于电源供应器的电磁干扰(Electromagnetic Interference,EMI)规范之要求,通常在硅基超接面金氧半场效电晶体(Super-Junction MOSFET,SJ-MOSFET)的闸极连接一具有较高外部闸极电阻值(Rg,ext)的外部闸极电阻,以抑制在开关瞬变期间闸极电压(Vg)和漏源电压(Vds)因高电压变化率(dV/dt)而引起的振荡。碳化硅金氧半场效电晶体(SiC MOSFET)因作为宽能隙半导体而可在较小尺寸的晶片上提供同等导通电阻的功效。举例来说,在导通电阻相同的条件下,650V的SiC MOSFET的晶片尺寸可以缩小到硅基SJ-MOSFET的1/4至1/20。内部闸极电阻值(Rg,int)是MOSFET闸极的等效串联电阻(equivalent series resistance,ESR),通常与MOSFET的晶片尺寸成反比关系,即晶片尺寸越小时,内部闸极电阻值(Rg,int)越大。据此,SiC MOSFET的内部闸极电阻值(Rg,int)通常高于具有相似导通电阻的硅基SJ-MOSFET。由于在开关瞬态期间SiC MOSFET压变化率(dV/dt)的峰值远低于具有相同开关耗损的硅基SJ-MOSFET,因此可以使用电阻值小或零电阻的外部闸极电阻而无须担心EMI的效能。基于MOSFET的开关耗损P

P

较高的内部闸极电阻值(Rg,int)可能在一定的程度上限制SiC MOSFET可以达到的最佳性能。

同时,对于一些开关频率相对较低而需要并联多个MOSFET才能达到更高功率水平的装置,可能会需要更高的内部闸极电阻值(Rg,int)以使MOSFET间的不平衡的开关(unbalanced switching)最小化。因此,需要更简单且经济的方式依据装置需求来降低或调整内部闸极电阻值(Rg,int)。

发明内容

本发明的目的在于改善习知碳化硅半导体装置的效能。

为达上述目的,本发明提供一种碳化硅金属氧化物半导体闸极式(MOS-gated)半导体装置,包括:一碳化硅基板;一漂移层,设置在该碳化硅基板上,该漂移层具有一第一导电类型且包含一主表面;一第一掺杂区,设置在该漂移层中,该第一掺杂区具有一与第一导电类型相反的第二导电类型,其中,该第一掺杂区和该漂移层形成复数个第一p-n接面和复数个接面场效电晶体(Junction Gate Field-Effect Transistor,JFET)区域,该第一掺杂区包含复数个基体部、复数个第一延伸部、以及复数个第一连接部,该些第一延伸部沿一第二水平方向延伸且彼此并排间隔设置,该些基体部和该些第一连接部沿该第一水平方向延伸且交替排列于该些第一延伸部之间;一第二掺杂区,设置于该第一掺杂区内,该第二掺杂区具有该第一导电类型,且该第二掺杂区和该第一掺杂区形成复数个第二p-n接面,其中,该第二掺杂区和该第一掺杂区之间定义出复数个沿着该主表面上的通道区;复数个第三掺杂区,设置于该第一掺杂区的该些基体部中,该些第三掺杂区具有该第二导电类型,且该些第三掺杂区被该第二掺杂区环绕;一闸极绝缘层,形成在该主表面上;一闸电极,形成在该闸极绝缘层上,包括一闸极总线区和一主动区,其中,该闸电极的该主动区包含复数个闸电极开口,相邻的两个闸电极开口间隔的一最小闸极宽度(W

W

其中,L

附图说明

图1A是本发明一实施例碳化硅MOS-gated半导体装置的俯视示意图。

图1B是图1A的部分放大示意图。

图1C是图1B的部分放大示意图。

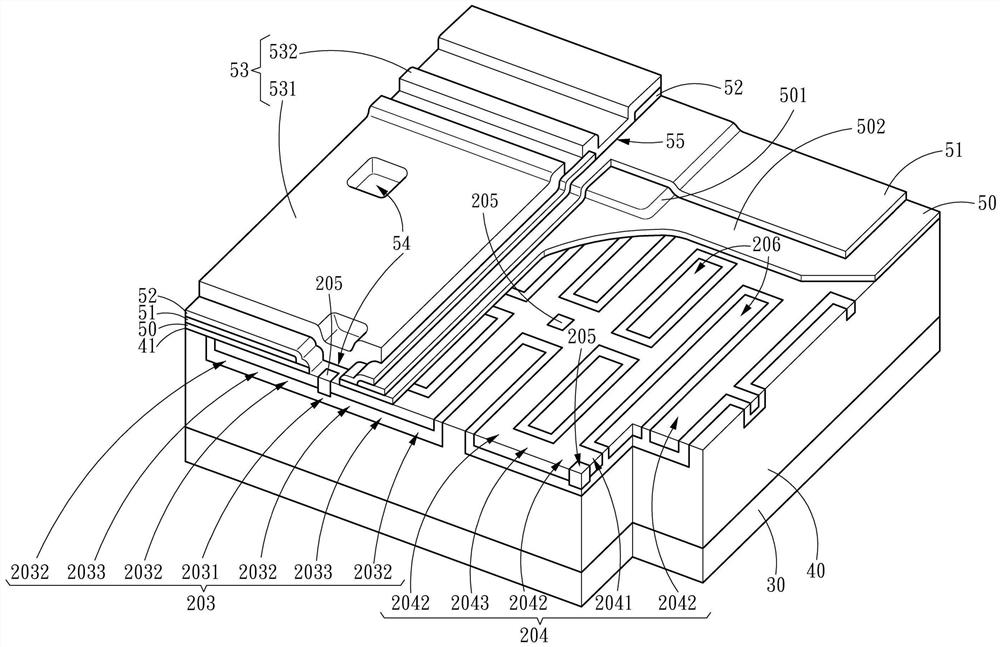

图2A是本发明一实施例碳化硅MOS-gated半导体装置的截面透视图。

图2B是该闸电极和该闸电极开口的俯视示意图。

图2C是该飘移层中的该第一掺杂区的俯视示意图。

图2D是该第一掺杂区中的该第二掺杂区和该第三掺杂区的俯视示意图。

图3至图9为本发明不同实施例碳化硅MOS-gated半导体装置的示意图。

图10为本发明一实施例碳化硅MOS-gated半导体装置的俯视图。

具体实施方式

以下揭露内容和图式提供有关本发明实施例或范例的详细内容。以下详细描述提供许多不同的实施例或范例以实施本案的不同特征。然而,这些特定的范例并非用以限定该些实施例必需要有所载的具体细节才能实践。

以下的揭露内容提供许多不同的实施例或范例以实施本案的不同特征。当然,这些特定的范例并非用以限定。例如,若是本发明实施例叙述了一第一特征部件形成于一第二特征部件之上或上方,即表示其可能包含上述第一特征部件与上述第二特征部件是直接接触的实施例,亦可能包含了有附加特征部件形成于上述第一特征部件与上述第二特征部件之间,而使上述第一特征部件与第二特征部件可能未直接接触的实施例。此外,以下所揭露之不同实施例可能重复使用相同的参考符号及/或标记。这些重复系为了简化与清晰的目的,并非用以限定所讨论的不同实施例及/或结构之间有特定的关系。

此外,其中可能用到与空间相关用词,例如「上方」、「下方」、「较低的」及类似的用词,这些空间相关用词系为了便于描述图示中一个(些)元件或特征部件与另一个(些)元件或特征部件之间的关系,除了图示中描绘的方位关系外,这些空间相关用词涵括使用中或操作中的装置之不同方位。该装置可以其他方式定位,且可使用同样的这些空间相关用词相应地解释。

在本文中,对各种实施例的描述中所使用的术语只是为了描述特定示例的目的,而并非旨在进行限制。除非上下文另外明确地表明,或刻意限定元件的数量,否则本文所用的单数形式“一”、“一个”及“该”也包含复数形式。另应理解的是,尽管在本文中在特定情况利用“第一”、“第二”等用语描述各种元件,但这些元件不受这些用语的限制,这些术语仅用于区分不同的元件。

尽管一些实施例以特定顺序来执行步骤,但是仍可以另一合理之顺序来执行这些步骤。对于不同的实施例,以下说明的某些特征可以替换或消除。应理解的是,一些额外的操作可以在所叙述的方法之前、之中或之后执行,并且在该方法的其他实施例中,某些操作可以被替换或省略。

图1A和图1B为本发明一实施例的一碳化硅金属氧化物半导体闸极式(MOS-gated)半导体装置中的一闸电极的俯视图。该闸电极包含一闸极总线区10和一主动区20。在图1A所示的实施例中,该闸极总线区10仅包括一个设置在该主动区20的一中心区域21的闸极垫区域。该闸极垫区域具有与该主动区20相邻的四个侧边10a、10b、10c、10d。该主动区20包括复数个形成在该主动区20内的闸电极开口201。如图1B所示,该主动区20可被分成依序排列的复数个重复的单元晶胞20a。该些重复的单元晶胞20a沿一第一水平方向X重复排列以形成复数个行(如图中所示R1至R6),且相邻的两行沿一第二水平方向Y交错排列,其中,相邻的该些单元晶胞20a交替地错位一位移D。于一实施例中,该位移D为该些单元晶胞20a的长度(pitch)的一半。

图1C为对应于图1B中该主动区20局部放大的俯视图,且为从一漂移层的顶面观察的视角。于此实施例中,对应于该碳化硅MOS-gated半导体装置的该主动区20的该漂移层包括形成在该漂移层上方的一第一掺杂区203、一第二掺杂区204和复数个第三掺杂区205,该漂移层和该第二掺杂区204具有一第一导电类型,该第一掺杂区203和该些第三掺杂区205具有一第二导电类型,该第二导电类型与第一导电类型相反。

请参阅图1C和图2A,图2A为本发明该碳化硅MOS-gated半导体装置的截面透视图,此为结构示意图,仅部分地说明该碳化硅MOS-gated半导体装置的结构。该碳化硅MOS-gated半导体装置包括一基板30、一漂移层40、一第一掺杂区203、一第二掺杂区204、复数个第三掺杂区205、一闸极绝缘层50、一闸电极层51、一层间介电层52和一金属层53。该基板30为一具有n型重掺杂(n+)的碳化硅基板。该漂移层40为n型轻掺杂(n-)形成于该基板30上。在本实施例中,该第一导电类型为n型轻掺杂(n-),该第二导电类型为p型。

该第一掺杂区203形成于与一主表面41相邻的该漂移层40中,且是透过例如将铝离子植入到氮掺杂的n型SiC漂移层中而形成。

该第二掺杂区204形成在该第一掺杂区203中,形成的方法例如将高剂量的磷离子植入该漂移层40中,并与p型的该第一掺杂区203形成复数个p-n接面,使该第二掺杂区204在邻接该主表面41的上部区域中被该第一掺杂区203包围。

该第三掺杂区205形成的方法例如将高剂量铝离子植入该漂移层40中,使该第三掺杂区205邻近该第二掺杂区204的一源极部分2041a且与该第一掺杂区203接触。

该闸极绝缘层50形成在该漂移层40的该主表面41上,形成的方法例如透过碳化硅的热氧化或二氧化硅的沉积,再于具有含氮气体的环境中退火,含氮气体包括但不限于氮气(N

请参阅图2B,为图1B中的其中一单元晶胞20a的示意图,说明该闸电极层51和该闸电极开口201。该闸电极层51的材料是采用例如提供低薄膜电阻的退化态n型或p型重掺杂的多晶硅(degenerate n-type or p-type poly-silicon),透过沉积形成于该闸极绝缘层50上,且该闸电极层51的一部分透过干式蚀刻而形成该闸电极开口201。在形成该闸电极开口201后,沉积该层间介电层52以在该闸极绝缘层50和该金属层53之间形成隔离,该层间介电层52的材料包括硼硅玻璃(Borosilicate Glass,BSG)、磷硅玻璃(PhosphosilicateGlass,PSG)、硼磷硅玻璃(Borophosphosilicate Glass,BPSG)、二氧化硅(SiO

请参阅图2A,在该些源极接触54之后形成至少一个闸极接触55。该金属层53沉积在该层间介质层52上并填入到该些源极接触54和该闸极接触55中。举例来说,该金属层53为一透过化学气相沈积(chemical vapor deposition,CVD)或物理气相沈积(physicalvapor deposition,PVD)形成的金属层,包含AlCu、AlSiCu、Al、Ti、TiN、TiW等。该金属层53的一第一部分531和一第二部分532透过干式蚀刻、湿式蚀刻或干式蚀刻和湿式蚀刻的组合分离,再将包括二氧化硅(SiO

在一实施例中,该闸电极层51的该闸极总线区10包括一闸极垫区域,且该金属层53的该第二部分532设置于该闸极垫区域上方且电性耦接于该闸电极层51(图未示),其中,该第二部分532的形状为一圆角矩形或一圆形。

在另一实施例中,该闸电极层51的该闸极总线区10包括一闸极垫区域和复数个闸极流道区域,且该金属层53的该第二部分532设置在闸极垫区域和该些闸极流道区域上方,并且电耦合至该闸电极层51以降低闸极电阻(图未示)。

参阅图2A和图2C,其中图2C显示其中一单元晶胞20a的该第一掺杂区203。该第一掺杂区203包括复数个基体部2031、复数个第一延伸部2032、以及复数个第一连接部2033。该些基体部2031、该些第一延伸部2032、以及该些第一连接部2033相互连接以在该漂移层40中形成一类网状结构。该些第一延伸部2032沿该第二水平方向Y延伸。此外,该些第一延伸部2032彼此并排且间隔设置。该些基体部2031和该些第一连接部2033沿该第一水平方向X延伸且交替排列于任意两个该第一延伸部2032之间。在一实施例中,部分的该些基体部2031和该些第一连接部2033沿该第一水平方向X延伸以形成复数个二维连接的H型结构。在任意两个该第一延伸部2032之间形成复数个接面场效电晶体(Junction Gate Field-Effect Transistor,JFET)区域206。在该第一掺杂区203内形成该第二掺杂区204后,复数个通道区207在相邻于该主表面41的一第一p-n接面和一第二p-n接面之间形成,其中,该第一p-n接面是由该第一掺杂区203和该第二掺杂区204所形成,该第二p-n接面是由该第一掺杂区203和该漂移层40所形成,如图1C和图2D所示。

请参阅图2A和图2D,该第二掺杂区204包括复数个源极部2041、复数个第二延伸区域2042、以及复数个第二连接部2043。该些第二延伸区域2042和该些第二连接部2043分别形成于该些第一延伸部2032和该些第一连接部2033内。该些源极部2041形成于该些基体部2031内。该第二掺杂区204是以图2A所示的方式形成于该第一掺杂区203中,以让该第一掺杂区203部分地位于该第二掺杂区204下方并且部分地延伸邻接该漂移层40的该主表面41。

当从上方往下观察时,每一该源极部2041位于其中一单元晶胞20a的中心位置。于该第一掺杂区203的布局类似,该些源极部2041和该些第二连接部2043沿该第一水平方向X延伸且交替排列于任意两个第二延伸部2042之间。于一实施例中,部分的该些源极部2041和该些第二连接部2043沿该第一水平方向X延伸以形成复数个二维连接的H型结构。

每一该第三掺杂区205形成在其中一单元晶胞20a的中心位置,该中心位置与该第二掺杂区204的该些源极部2041相邻并与该第一掺杂区203接触。

复参阅图1B、图1C、图2A和图2D,在本发明中,相邻的两个闸电极开口201间隔一最小闸极宽度(W

W

L

根据本发明的一实施例,该闸极总线区10只包含一个闸极垫区域,且该碳化硅MOS-gated半导体装置的闸极电阻可基于该闸极垫区域相对于该主动区20的位置进行调整。

于图1A所示的实施例中,该闸极垫区域被该主动区20环绕,且该闸极垫区域的四边10a、10b、10c、10d与该主动区20连接。图3至图9为本发明的该碳化硅MOS-gated半导体装置的不同实施例。于图3所示的实施例中,该闸极垫区域10’沿一边缘22设置,且该闸极垫区域10’的三个侧边10a、10b、10d与该主动区20连接。于图4所示的实施例中,该闸极垫区域10’沿一边角23设置,且该闸极垫区域10’的两个侧边10a、10d与该主动区20连接。于图1A、图3和图4中的该碳化硅MOS-gated半导体装置分别具有一第一闸极电阻、一第二闸极电阻、以及一第三闸极电阻。该第一闸极电阻低于该第二闸极电阻,该第二闸极电阻低于该第三闸极电阻。例如,一具有以图1A所示设置的该闸极垫区域10’的碳化硅MOSFET的闸极电阻为5欧姆,一具有以图4所示设置的该闸极垫区域10’的碳化硅MOSFET的闸极电阻为15欧姆,然而上述两种碳化硅MOSFET的该主动区20的面积完全相同。

于图5所示的另一实施例中,该闸极总线区10设置在该主动区20的该中心区域21,且该闸极总线区10包含一闸极垫区域10’和一闸极流道区域11,该闸极流道区域11自该闸极垫区域10’沿该第一水平方向X延伸。该闸极流道区域11用于进一步降低该闸极电阻,但须使用更大的晶片面积以及耗费更多成本。于图6所示的另一实施例中,该闸极总线区10设置在该主动区20的该中心区域21,且该闸极总线区10包含一闸极垫区域10’和四个闸极流道区域11a、11b、11c、11d。于图7所示的另一实施例中,该闸极总线区10设置在该主动区20的该中心区域21,且该闸极总线区10包含一闸极垫区域10’和一闸极流道区域11,该闸极流道区域11自该闸极垫区域10’沿该第二水平方向Y延伸。于图8所示的另一实施例中,该闸极总线区10设置在该主动区20的该中心区域21,且该闸极总线区10包含一闸极垫区域10’和一闸极流道区域11,该闸极流道区域11围绕该主动区20设置。该闸极流道区域11可设置在该碳化硅MOS-gated半导体装置的一外围区域,该外围区域对应该碳化硅MOS-gated半导体装置的终端区,并且在该主动区20之外。如此,该主动区20便可以不用牺牲其面积来设置该闸极流道区域11,进而最小化设置该闸极流道区域11对晶面总面积尺寸和成本的影响。于图9所示的另一实施例中,该闸极总线区10包含一个以上的闸极垫区域10’,且在该主动区20的该中心区域21分布三个闸极垫区域101、102、103。

图10为本发明一实施例的该碳化硅MOS-gated半导体装置。于替代实施例中,该些重复的单元晶胞20a可沿该第二水平方向Y重复排列以形成多列(图示中C1至C11),且相邻的列彼此交错排列,其中,相邻的任两该单元晶胞20a以一位移交替错位地设置。

- 碳化硅半导体装置及碳化硅半导体装置的制造方法

- 金属互连,制造金属互连的方法,半导体装置和制造半导体装置的方法

- 碳化硅沟槽式金属氧化物半导体场效应晶体管

- 具有优化层的碳化硅金属氧化物半导体(MOS)装置中的电场屏蔽