跨电气域可移植性的高速SPI总线接口

文献发布时间:2023-06-19 19:20:08

技术领域

本发明电路电子技术领域,尤其涉及一种跨电气域可移植性的高速SPI总线接口。

背景技术

SPI总线是一种常用的标准串行总线接口,具有结构简单、占用引脚和逻辑资源少、灵活性高等特点,常被用于跨电气域处理器间CCDL场景。目前,传统跨电气域间SPI总线接口主要存在两方面的问题:

(1)隔离器的传输延时导致跨电气域间SPI总线接口速率较低,严重影响处理器间CCDL的带宽;

(2)隔离器品类不一,传输延时从十几纳秒到几十纳秒不等,导致SPI总线控制逻辑在跨平台间的移植性差。

因此,针对跨电气域间SPI总线接口速率低,移植性差的问题,设计一种跨电气域可移植的高速SPI总线接口,提升SPI总线接口的通讯速率和通用性具有重要意义。

发明内容

有鉴于此,本发明提供一种跨电气域可移植性的高速SPI总线接口,至少部分解决现有技术中SPI总线接口在数据交互时通讯速率和通用性较低的问题。

一种跨电气域可移植性的高速SPI总线接口,适用于SPI主设备与SPI从设备间的数据交互,包含四线制SPI总线的MCSN、MCLK、MOSI和MISO信号及SCSN和SCLK两路信号,其中:

在SPI主设备在SPI总线传输开始后将片选信号MCSN置为低,SPI主设备输出SPI总线时钟信号MCLK,SPI主设备在MCLK的下降沿时刻移位输出SPI串行数据信号MOSI,SPI从设备在MCLK的上升沿时刻移位采集SPI串行数据信号MOSI,SPI从设备依据MCLK产生输出SCLK,并在SCLK的下降沿时刻移位输出SPI串行数据信号MISO;

在SPI从设备在SPI总线输出结束后将SCSN置为高,SPI主设备在SCLK的上升沿时刻移位采集SPI串行数据信号MISO,SPI主设备在采集到SCSN上升沿后将MCSN置为高,SPI总线传输结束。

有益效果:

跨电气域的通用化SPI总线接口较典型四线制SPI总线接口多了SCSN和SCLK两路信号,在通讯发生后,SPI从设备依据MCLK信号产生SCLK信号,同时移位输出MISO信号,SPI主设备在SCLK信号的上升沿时刻移位采集MISO信号,有效消除了隔离器芯片的传输延时的影响,提高主从SPI设备间的传输速率,实现跨平台间移植,显著提高了SPI总线的通用化水平,可广泛应用与工业领域。

附图说明

为了更清楚地说明本公开实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

图1为典型四线制SPI总线接口架构图;

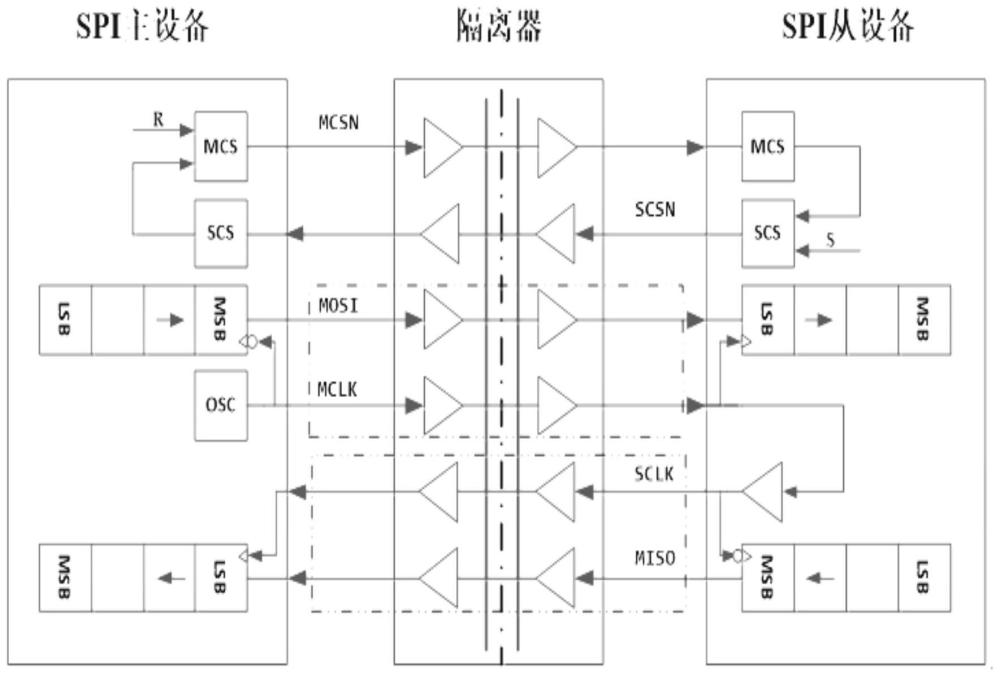

图2为跨电气域可移植的高速SPI总线接口架构图。

具体实施方式

下面结合附图对本公开实施例进行详细描述。

以下通过特定的具体实例说明本公开的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本公开的其他优点与功效。显然,所描述的实施例仅仅是本公开一部分实施例,而不是全部的实施例。本公开还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本公开的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。基于本公开中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本公开保护的范围。

要说明的是,下文描述在所附权利要求书的范围内的实施例的各种方面。应显而易见,本文中所描述的方面可体现于广泛多种形式中,且本文中所描述的任何特定结构及/或功能仅为说明性的。基于本公开,所属领域的技术人员应了解,本文中所描述的一个方面可与任何其它方面独立地实施,且可以各种方式组合这些方面中的两者或两者以上。举例来说,可使用本文中所阐述的任何数目个方面来实施设备及/或实践方法。另外,可使用除了本文中所阐述的方面中的一或多者之外的其它结构及/或功能性实施此设备及/或实践此方法。

如图2所示的跨电气域可移植性的高速SPI总线接口,适用于SPI主设备与SPI从设备间的数据交互,包含四线制SPI总线的MCSN、MCLK、MOSI和MISO信号及SCSN和SCLK两路信号,即为,在典型四线制SPI总线接口多设置了SCSN和SCLK两路信号,其中:

在SPI主设备在SPI总线传输开始后将片选信号MCSN置为低,SPI主设备输出SPI总线时钟信号MCLK,SPI主设备在MCLK的下降沿时刻移位输出SPI串行数据信号MOSI,SPI从设备在MCLK的上升沿时刻移位采集SPI串行数据信号MOSI,SPI从设备依据MCLK产生输出SCLK,并在SCLK的下降沿时刻移位输出SPI串行数据信号MISO;

在SPI从设备在SPI总线输出结束后将SCSN置为高,SPI主设备在SCLK的上升沿时刻移位采集SPI串行数据信号MISO,SPI主设备在采集到SCSN上升沿后将MCSN置为高,SPI总线传输结束。

本发明的方法,更多的适用于有隔离器的情况,如图2所示,SCSN信号和SCLK信号由SPI从设备产生输出,经过隔离器之后输入到SPI主设备。

作为本案所提供的具体实施方式,在SPI总线传输开始时,SPI主设备将MCSN信号置为低;SPI主设备在检测到SCSN信号的上升沿时将MSCN信号置为高。SPI从设备在检测到MCSN信号的下降沿时将SCSN信号置为低;SPI从设备在MISO移位输出结束后将SCSN信号置为高。

作为本案所提供的具体实施方式,SPI从设备依据MCLK信号输出SCLK信号,当SPI从设备检测到MCLK信号的上升沿时将SCLK信号置为高,当SPI从设备检测到MCLK信号的下降沿时将SCLK信号置为低。

作为本案所提供的具体实施方式,SPI从设备在SCLK信号的下降沿时刻移位输出MISO信号,并且,SPI主设备在SCLK信号的上升沿时刻移位采集MISO信号。

发明能够适用于跨电气域FPGA间的CCDL场景。跨电气域的通用化SPI总线接口较典型四线制SPI总线接口多了SCSN和SCLK两路信号,在通讯发生后,SPI从设备依据MCLK信号产生SCLK信号,同时移位输出MISO信号,SPI主设备在SCLK信号的上升沿时刻移位采集MISO信号,有效消除了隔离器芯片的传输延时的影响,提高主从SPI设备间的传输速率,实现跨平台间移植,显著提高了SPI总线的通用化水平,可广泛应用与工业领域。

首先,结合图1描述在跨电气域场景中,典型四线制SPI总线接口存在的问题。当SPI总线通讯开始时,SPI主设备将片选信号MCSN置为低,产生串行时钟信号MCLK,并在MCLK的下降沿时刻移位输出串行数据信号MOSI;MCSN、MCLK和MOSI同时经过隔离器输入到SPI从设备,SPI从设备在MCSN为低,且检测到MCLK的上升沿时移位采集MOSI,SPI从设备在MCSN为低,且检测到MCLK的下降沿时移位输出串行数据MISO;SPI主设备在MCLK的上升沿时刻移位采集MISO;在采集结束后,SPI主设备将MCSN置为高,SPI通讯结束。

一方面,SPI主设备产生串行时钟信号MCLK,MCLK通过隔离器输入到SPI从设备,其传输延时为Δt,SPI从设备检测到MCLK的下降沿相对于SPI主设备发生MCLK时刻的延时为Δt;另一方面,SPI从设备在检测到MCLK的下降沿时刻移位输出MISO,MISO经过隔离器输入到SPI主设备,其传输延时为Δt,SPI主设备在MCLK的上升沿时刻移位采集MISO,MISO相对于SPI主发设备发生MCLK时刻的延时为2×Δt,此时SPI主设备能正确采集MISO的前提是MCLK的周期大于4×Δt,通常Δt在几十纳秒的量级,这使得跨电气域间SPI总线通讯的速率难以突破10Mbps。并且电气隔离芯片类中繁多,其传输延时也不尽相同,导致SPI总线控制逻辑在不同平台间难以移植,通用性水平较低。

针对上述跨电气域场景中,典型四线制SPI总线接口传输速率低,且移植性差的问题,本发明设计了一种跨电气域可移植的高速SPI总线接口,下面结合图2进行讲述。本发明所述跨电气域可移植的高速SPI总线接口包含MCSN、SCSN、MCLK、MOSI、SCLK和MISO,比典型四线制SPI总线接口多了SCSN和SCLK两路信号。SPI主设备在SPI总线传输开始后将片选信号MCSN置为低;SPI主设备输出SPI总线时钟信号MCLK,SPI主设备在MCLK的下降沿时刻移位输出SPI串行数据信号MOSI;SPI从设备在MCLK的上升沿时刻移位采集SPI串行数据信号MOSI,SPI从设备依据MCLK产生输出SCLK,并在SCLK的下降沿时刻移位输出SPI串行数据信号MISO,SPI从设备在SPI总线输出结束后将SCSN置为高;SPI主设备在SCLK的上升沿时刻移位采集SPI串行数据信号MISO,SPI主设备在采集到SCSN上升沿后将MCSN置为高,SPI总线传输结束。其中,SCSN信号和SCLK信号由SPI从设备产生输出,经过隔离器之后输入到SPI主设备。在SPI总线传输开始时,SPI主设备将所述MCSN信号置为低;SPI主设备在检测到SCSN信号的上升沿时将所述MSCN信号置为高。SPI从设备在检测到MCSN信号的下降沿时将所述SCSN信号置为低;SPI从设备在MISO移位输出结束后将所述SCSN信号置为高。SPI从设备依据MCLK信号输出所述SCLK信号,当SPI从设备检测到MCLK信号的上升沿时将SCLK信号置为高,当SPI从设备检测到MCLK信号的下降沿时将SCLK信号置为低。SPI从设备在SCLK信号的下降沿时刻移位输出所述MISO信号;SPI主设备在所述SCLK信号的上升沿时刻移位采集所述MISO信号。

在通讯发生后,SPI从设备在依据MCLK完成MISO移位输出的同时产生SCLK,MISO与SCLK同时经过隔离芯片输入到SPI主设备,SPI主设备再依据SCLK的上升沿完成对MISO的移位采集,此时,SCLK相对于MISO的延时可忽略,有效消除了隔离器芯片的传输延时的影响,提高主从SPI设备间的传输速率,实现跨平台间移植,显著提高了SPI总线的通用化水平。

以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以权利要求的保护范围为准。

- 一种片上网络的跨时钟域高速数据通信接口电路

- 一种片上网络的跨时钟域高速数据通信接口电路