一种晶圆级芯片的扇入型封装结构的制作方法

文献发布时间:2024-01-17 01:28:27

技术领域

本发明涉及一种晶圆级芯片的扇入型封装结构的制作方法,属于半导体封装技术领域。

背景技术

倒装芯片具有良好的电性能、散热性能已经被广泛在半导体领域。现有技术CN203707108U公开了一种硅基圆片级封装结构,请参考图1,图1为现有技术一种硅基圆片级封装结构的剖面示意图,其包括硅基本体110和带有若干个电极210的IC芯片200,每一电极210上设置若干个金属柱/金属块300,IC芯片200的另一面通过贴片胶700与硅基本体110连接;塑封层将IC芯片200、金属柱/金属块300和贴片胶700封装于其内,金属柱/金属块300的端面露出塑封层,并在其端面设置布线走向独立的再布线金属层500,图中再布线金属层500由一层介电层510和一层金属层520构成为例,相邻的再布线金属层500向电极210外侧延伸,并在再布线金属层500的终端的表面设置焊球凸点600。由于介电层510的介电材料为低温固化材料,这种材料与金属的结合力不佳,在后期使用中容易出现介电层510与金属柱/金属块300分层;这种分层会导致金属布线与金属柱结合部位受到很大的应力,从而产生分层或断裂;特别是对于高密度封装产品,再布线金属层500的金属线路与金属柱的互连面积较小时,金属线路与金属柱结合部位非常容易失效。

同时,金属柱/金属块300的侧壁出现氧化难以发现,氧化层较厚时包覆材料与金属柱/金属块300出现分层,导致包覆材料(塑封层)不能很好的起到缓冲应力的作用,应力经金属柱/金属块300传递到IC芯片200表面,造成芯片表面开裂;特别高密度布线需要减小金属柱/金属块300尺寸时,塑封层与金属分层及金属柱/金属块300尺寸减小同时导致的芯片表面应力集中效应更显著。这些影响因素相互作用、甚至叠加,极大的降低了产品的可靠性。

发明内容

为了克服现有方法的不足,本发明提供一种提升产品的可靠性的晶圆级芯片的扇入型封装结构的制作方法。

本发明的技术方案:

本发明提供了一种晶圆级芯片的扇入型封装结构的制作方法如下:

步骤一,提供晶圆,所述晶圆的硅基本体的上表面内预先设置复数个芯片电极;步骤二,多次利用微影光刻及电镀工艺在晶圆的芯片电极上形成下大上小的金属阶梯微凸台;

步骤三,在晶圆上方用塑封料包覆所有的金属阶梯微凸台形成塑封层;

步骤四,利用减薄工艺,减薄塑封层,露出金属阶梯微凸台的上表面;

步骤五,利用金属再布线工艺形成不连续的再布线金属层,所述再布线金属层包括复数个多层金属图形层单体和填充其间的介电层;

步骤六,所述介电层的上表面内半嵌入金属凸块,所述金属图形层向下与金属阶梯微凸台电信连接,所述金属图形层向上与金属凸块电信连接;

步骤七,在所述金属凸块上形成焊料连接件;

步骤八,切割形成复数颗独立的晶圆级芯片的扇入型封装结构单体。

作为可选的技术方案,步骤二中,所述多次利用微影光刻及电镀工艺在晶圆的芯片电极上形成下大上小的金属阶梯微凸台的工艺如下:依次利用微影光刻及电镀工艺在芯片电极上形成微金属层I,所述微金属层I的横截面尺寸≤芯片电极的横截面尺寸,多次重复所述微影光刻及电镀工艺工艺,逐渐缩小光刻胶图案层开口的尺寸,形成复数个依次固连的微金属层。

作为可选的技术方案,在所述微金属层上重复所述微影光刻及电镀工艺,缩小光刻胶图案层开口的尺寸的同时增加光刻胶图案层的厚度,形成依次固连的微金属柱。

作为可选的技术方案,所述金属阶梯微凸台的阶梯数≥2;

作为可选的技术方案,步骤二中,所述金属阶梯微凸台的阶梯数为3个、4个或5个。

作为可选的技术方案,步骤五中,所述金属图形层单体左右选择性连续。

作为可选的技术方案,步骤五中,所述金属图形层单体的个数与芯片电极的个数一一对应。

作为可选的技术方案,步骤七中,所述焊料连接件包括焊球或焊料凸块。

作为可选的技术方案,步骤八中,所述晶圆级芯片的扇入型封装结构单体包含硅基本体,所述硅基本体的上表面内预先设置复数个芯片电极,所述芯片电极上设置金属阶梯微凸台,所述金属阶梯微凸台包括若干层从下往上尺寸依次减小的微金属层和/或若干个尺寸依次减小的微金属柱,所述微金属层和/或微金属柱依次固连,所述金属阶梯微凸台的阶梯数≥2,用塑封料包覆所有的金属阶梯微凸台形成塑封层,所述塑封层露出金属阶梯微凸台的上表面,所述塑封层上设置再布线金属层,所述再布线金属层包括多层的电信连接的金属图形层单体和填充其间的介电层,所述金属图形层单体可以选择性连续,或者其个数可以与芯片电极的个数一一对应,所述再布线金属层的金属部分向下通过金属阶梯微凸台的上表面与金属阶梯微凸台实现电信连接,其金属部分向上设置半嵌入介电层的金属凸块,实现与金属凸块电信连接,再在金属凸块上形成焊料连接件。

作为可选的技术方案,所述金属阶梯微凸台第一阶梯的横截面尺寸≤芯片电极的横截面尺寸。

有益效果

本发明提出一种晶圆级芯片的扇入型封装结构的制作方法,即采用微影光刻及电镀工艺形成具有下大上小结构的金属阶梯微凸台,使其上的再布线金属层的介电层与金属阶梯微凸台的接触面尽量减小,形成互锁结构,扩大了介电材料与包覆材料(即塑封层)的结合面积,及时吸收介电材料与金属阶梯微凸台之间的分层应力,有利于控制分层的产生,确保再布线金属层与金属阶梯微凸台的电性连接,同时也降低了传递到芯片表面的应力,提升了产品的可靠性的。

附图说明

图1为现有技术公开的晶圆级芯片的扇入型封装结构的剖面结构的示意图;

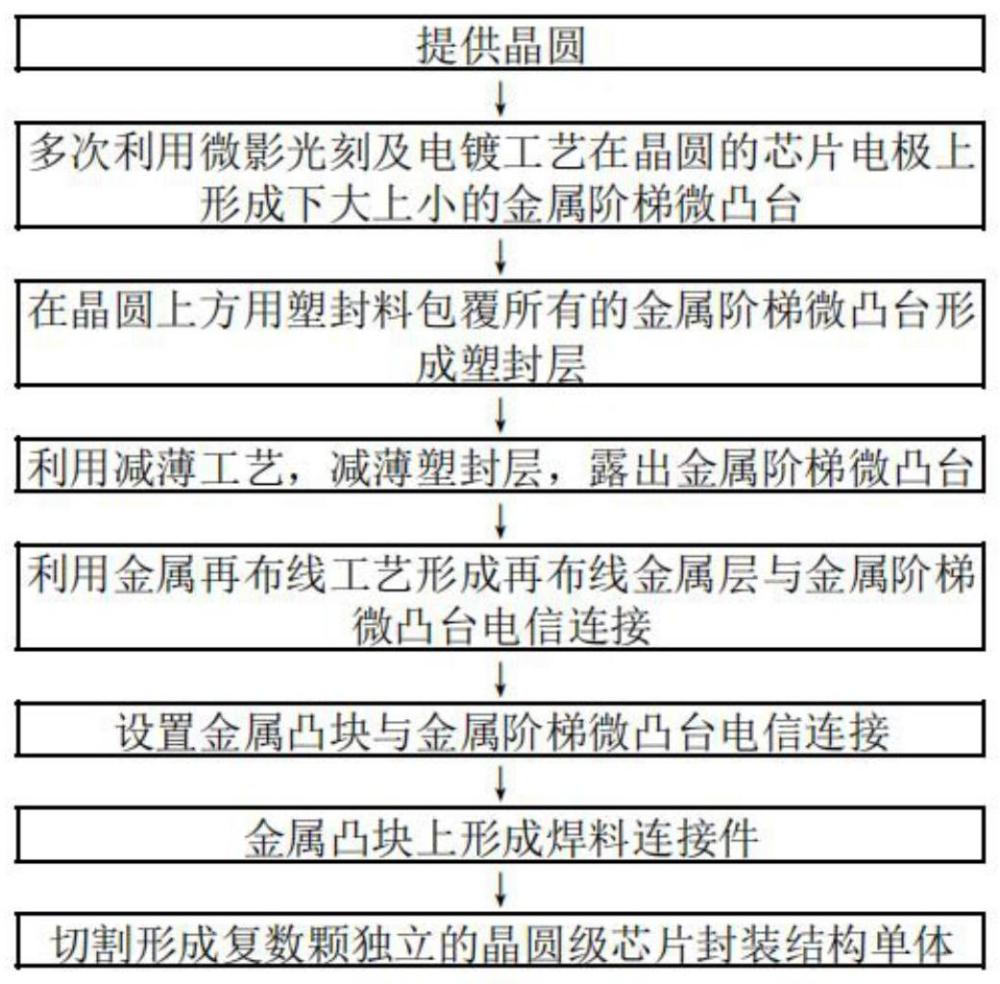

图2为本发明一种晶圆级芯片的扇入型封装结构的制作方法的流程示意图;

图3为本发明一种晶圆级芯片的扇入型封装结构的剖面结构的实施例的示意图;

图4为图3中金属图形层单体左右选择性连续的示意图;

图5A至图5J为本发明一种晶圆级芯片的扇入型封装结构的制作方法的实施例的工艺过程的流程图;

其中:

晶圆100

晶圆的硅基本体101

芯片电极102

凸台底部2031

凸台中部2032

凸台中部的横截面20321

凸台顶部2033

金属线201

劈刀型腔202

介电层Ⅰ401

金属图形层单体402

介电层Ⅱ403

金属凸块404

焊球500。

实施方式

下面结合附图和实施例对本申请作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与有关发明相关的部分。

需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本申请。

如图2所示,本发明一种晶圆级芯片的扇入型封装结构的制作方法:

步骤S101,提供晶圆;

步骤S102,多次利用微影光刻及电镀工艺在晶圆的芯片电极上形成下大上小的金属阶梯微凸台;

步骤S103,在晶圆上方用塑封料包覆所有的金属阶梯微凸台形成塑封层;

步骤S104,利用减薄工艺,减薄塑封层,露出金属阶梯微凸台;

步骤S105,利用金属再布线工艺形成再布线金属层与金属阶梯微凸台电信连接;步骤S106,设置金属凸块与金属阶梯微凸台电信连接;

步骤S107,金属凸块上形成焊料连接件;

步骤S108,切割形成复数颗独立的晶圆级芯片的扇入型封装结构单体。

具体地,本发明一种晶圆级芯片的扇入型封装结构,如图3所示,其包含硅基本体101、金属阶梯微凸台、再布线金属层与焊料连接件。硅基本体101的上表面内预先设置复数个芯片电极102。其中,所述金属阶梯微凸台包括若干层从下往上尺寸依次减小的微金属层和/或若干个尺寸依次减小的微金属柱,微金属层和/或微金属柱依次固连。金属阶梯微凸台的阶梯数≥2。微金属层和微金属柱的横截面形状与芯片电极102的横截面形状一致,如:如果芯片电极102的横截面形状为长方形,则微金属层和微金属柱的横截面形状也为长方形。微金属层和微金属柱的横截面形状与芯片电极102的横截面形状可以不一致,如:如果芯片电极102的横截面形状为长方形,则微金属层和微金属柱的横截面形状可以为圆形。金属阶梯微凸台第一阶梯的横截面尺寸≤芯片电极102的横截面尺寸。图3中以二阶金属阶梯微凸台示意:在芯片电极102上设置第一阶梯,第一阶梯为微金属层I2041,微金属层I2041的横截面尺寸小于芯片电极102的横截面尺寸;在微金属层I2041上设置第二阶梯,第二阶梯为微金属柱2042,微金属柱2042的尺寸小于微金属层I2041的尺寸,微金属柱2042与微微金属层I2041固定连接;用塑封料包覆所有的金属阶梯微凸台形成塑封层301,塑封层301露出金属阶梯微凸台的上表面,图中以微金属柱的上表面20421示意。

再布线金属层设置在塑封层301上,如图3中所示,再布线金属层包括多层的电信连接的金属图形层单体和填充其间的介电层。图中再布线金属层包括介电层Ⅰ401、若干个金属图形层单体402和介电层Ⅱ403示意,金属图形层单体可以选择性连续,如图4所示,或者其个数可以与芯片电极102的个数一一对应。介电层Ⅰ401与介电层Ⅱ403可以为一体结构。再布线金属层的金属部分向下通过金属阶梯微凸台的上表面与金属阶梯微凸台实现电信连接,其金属部分向上设置半嵌入介电层的金属凸块404,实现与金属凸块404电信连接,再在金属凸块404上形成焊球500、焊料凸块等焊料连接件,图中以焊球500示意。

本发明一种晶圆级芯片的扇入型封装结构的制作方法,如图5A至图5G所示,其工艺过程如下:

步骤一,见图5A,提供晶圆100,所述晶圆的硅基本体101的上表面内预先设置复数个芯片电极102;

步骤二,见图5B至图5F,依次利用微影光刻及电镀工艺在芯片电极102上形成微金属层I2041,微金属层I2041的横截面尺寸≤芯片电极102的横截面尺寸。微影光刻工艺使用激光曝光设备,可以制造出亚微米精度的精细图案。多次重复微影光刻及电镀工艺,并逐渐缩小其光刻胶图案层开口的尺寸,形成下大上小的金属阶梯微凸台。一般的,金属阶梯微凸台的阶梯数为2个、3个、4个或5个,且依次固连,如图5C和图5D所示。或者,在微金属层I2041上重复上述微影光刻及电镀工艺,缩小光刻胶图案层开口的尺寸的同时增加光刻胶图案层的厚度,形成微金属层和微金属柱依次固连的金属阶梯微凸台,图中微金属柱2042的横截面尺寸小于微金属层I2041的尺寸,如图5E所示;或者,根据需要多次重复上述工艺,得到合适的微金属层的层数和微金属柱的叠加个数的金属阶梯微凸台,微金属层的层数以2层或3层为佳,金属柱的个数以1个或2个为佳,如图5F所示。

步骤三,见图5G,在晶圆100上方用塑封料包覆所有的金属阶梯微凸台形成塑封层301,图中选择图5E进行示意;

步骤四,见图5H,利用减薄工艺,减薄塑封层301,露出金属阶梯微凸台的上表面,金属阶梯微凸台的剩余高度根据实际情况确定,图中金属阶梯微凸台的上表面以第二阶梯的微金属柱或微金属层的上表面20421示意。

步骤五,见图5I,利用成熟的金属再布线工艺在塑封层301上形成再布线金属层,再布线金属层包括复数个多层金属图形层单体和填充其间的介电层,多层金属图形层单体内部的金属图形层上下电信连接。多层金属图形层单体的个数与芯片电极102一一对应或者多层金属图形层单体左右选择性连接。图5I中再布线金属层包括介电层Ⅰ401、若干个多层金属图形层单体402和介电层Ⅱ403示意,介电层Ⅰ401与介电层Ⅱ403可以为一体结构。

步骤六,见图5I,金属凸块404半嵌入再布线金属层的介电层的上表面内,再布线金属层向下与金属阶梯微凸台电信连接,向上与金属凸块404电信连接;步骤七,见图5I,在金属凸块404上形成焊球500、焊料凸块等焊料连接件,图中以焊球500示意。

步骤八,见图5J,切割形成复数颗独立的晶圆级芯片的扇入型封装结构单体。

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明实施例揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求的保护范围为准。

- 一种晶圆级封装红外探测器及其制作方法

- 一种晶圆级封装红外探测器及其制作方法

- 一种晶圆级扇出封装方法以及封装结构

- 一种晶圆级封装结构及其封装方法

- 一种扇出型晶圆级芯片的封装方法及其封装结构

- 一种扇出型晶圆级芯片封装结构及封装方法