一种高性能晶体驱动电路

文献发布时间:2023-06-19 09:41:38

技术领域

本发明涉及集成电路技术领域,特别是涉及一种高性能晶体驱动电路。

背景技术

晶体驱动器自上世纪20年代问世以来,其理论研究与制造水平都得到了飞速发展,各项性能指标显著提升。作为一种是时钟频率源,与其他类型的振荡器相比,晶体振荡器以其优异的Q值、频率精度、稳定度等,广泛应用于军工以及民用消费电子领域。而在集成电路领域,为了使晶体频率信号有效、合理地传输至芯片核心,IO接口集成电路地作用至关重要。随着对晶体驱动电路要求越来越高,低电源供电成为趋势,尤其低至单节干电池供电更是设计现有结构的瓶颈。

发明内容

本发明的主要目的在于提供一种高性能晶体驱动电路,旨在解决现有技术中的问题。

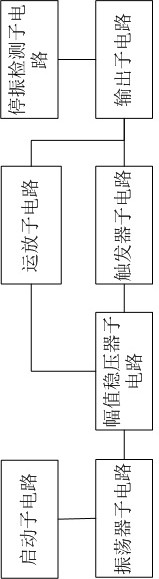

为实现上述目的,本发明提供一种高性能晶体驱动电路,所述高性能驱动电路包括启动子电路、幅值稳压器子电路、振荡器子电路、运放子电路、触发器子电路和输出子电路;所述启动子电路连接于所述幅值稳压器子电路并为后续电路提供启动电压,所述幅值稳压器子电路连接于所述振荡器子电路,通过所述幅值稳压器子电路进行调节以降低所述振荡器子电路输出信号的幅值,所述运放子电路连接于所述振荡器子电路和输出子电路,所述运放子电路将所述振荡器子电路的输出信号进行放大、并由所述输出子电路输出;所述触发器子电路连接于所述振荡器子电路和所述输出子电路,所述振荡器子电路接收到有源时钟信号时,所述触发器子电路接通并对所述有源时钟信号进行整形后发送至所述输出子电路。

优选地,所述高性能驱动电路还包括停振检测子电路,所述停振检测子电路连接于所述输出子电路、接收所述输出子电路的输出信号,并输出检测结果。

优选地,所述触发器子电路包括第一信号输入端、第二信号输入端、第三信号输入端和第一输出端;

所述第一信号输入端连接于第一使能信号端以接收第一使能信号;所述第二信号输入端通过第一反相器连接于所述第一使能信号端,用以接收所述第一使能信号的反向信号;所述第三信号输入端连接于所述振荡器子电路,所述第一输出端连接于所述输出子电路。

优选地,所述触发器子电路为施密特触发器。

优选地,所述启动子电路连接于所述第一使能信号端,所述启动子电路接收所述第一使能信号端输入的第一使能信号以为后续电路提供启动电压。

优选地,所述振荡器子电路包括晶体,所述晶体的一端连接有第一电容、另一端连接有第二电容和第一NMOS管,所述第一NMOS管的漏极连接于所述稳压器子电路、源极连接于所述第一电容和所述第二电容、栅极连接于稳压器子电路。

本发明的高性能晶体驱动电路包括启动子电路、幅值稳压器子电路、振荡器子电路、运放子电路、触发器子电路和输出子电路,通过触发器子电路使得电路可选有源输入、无源晶体输入两种模式,当振荡器子电路输入有源时钟信号时,触发器子电路处理该有源时钟信号后发送至输出子电路。

附图说明

图1为本发明高性能晶体驱动电路的原理示意图;

图2为本发明高性能晶体驱动电路中振荡器子电路的原理示意图;

图3为本发明高性能晶体驱动电路中幅值稳压器子电路的原理示意图;

图4为本发明高性能晶体驱动电路中停振检测子电路的原理示意图;

图5为本发明高性能晶体驱动电路中启动子电路的原理示意图;

图6为本发明高性能晶体驱动电路中触发器子电路的原理示意图;

图7为本发明实施例中无源输入工作模式的原理示意图;

图8为本发明实施例中有源输入工作模式的原理示意图。

本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

下面结合附图对本发明进一步说明。

一种高性能晶体驱动电路,如图1所示,所述高性能驱动电路包括启动子电路、幅值稳压器子电路、振荡器子电路、运放子电路、触发器子电路和输出子电路;所述启动子电路连接于所述幅值稳压器子电路并为后续电路提供启动电压,所述幅值稳压器子电路连接于所述振荡器子电路,通过所述幅值稳压器子电路进行调节以降低所述振荡器子电路输出信号的幅值,所述运放子电路连接于所述振荡器子电路和输出子电路,所述运放子电路将所述振荡器子电路的输出信号进行放大、并由所述输出子电路输出;所述触发器子电路连接于所述振荡器子电路和所述输出子电路,所述振荡器子电路接收到有源时钟信号时,所述触发器子电路接通并对所述有源时钟信号进行整形后发送至所述输出子电路。

如图2所示,所述振荡器子电路包括晶体,所述晶体的一端连接有第一电容、另一端连接有第二电容和第一NMOS管,所述第一NMOS管的漏极连接于所述稳压器子电路、源极连接于所述第一电容和所述第二电容、栅极连接于稳压器子电路。

优选地,所述晶体为32.768K晶体。

本发明实施例包括有启动子电路幅值稳压器子电路、振荡器子电路、运放子电路、触发器子电路和输出子电路,用以驱动32.768K晶体,在一些实施例中,可选择有源输入或者无源晶体输入两种模式。在无源输入模式下,本发明实施例具有极低的功耗,在常温常压TT corner,负载电容18p下,消耗电流仅150nA,建立时间100ms,稳定时间300ms,时钟频率占空比50%正负2%,具有极好的性能。

如图3所示,幅值稳压器子电路包括第一PMOS管Mp1、第二PMOS管Mp2、第三PMOS管Mp3、第四PMOS管Mp4、第五PMOS管Mp5、第六PMOS管Mp6和第三电容C3、第四电容C4、第五电容C5和第六电容C6,所述第一PMOS管Mp1分别连接于电源和第二PMOS管Mp2,所述第三PMOS管Mp3通过第三电容C3连接于所述振荡器子电路中的所述第一NMOS管Mn1,所述第四PMOS管Mp4通过第四电容C4连接于电源,所述第五PMOS管Mp5连接于第四PMOS管Mp4、并通过第五电容C5连接于电源,所述第六PMOS管Mp6连接于所述第五PMOS管Mp5和第六电容C6、并通过第一电阻R1连接于电源。

幅值稳压器子电路在工作状态下,当没有激励时,第六PMOS管Mp6的栅电压相当低,会有一个大电流流过第一NMOS管Mn1。当振荡器子电路开始工作时候,越来越多的电流流过第三PMOS管Mp3,从而,使第六PMOS管Mp6的栅电压增高。一段时间后,第三PMOS管Mp3、第一NMOS管Mn1上电流开始减少。为了能达到均衡,稳压器子电路维持了振荡器工作所需要的最小电流。

第一PMOS管Mp1的源极连接于电源、栅极和漏极连接于第二PMOS管Mp2的源极;所述第二PMOS管Mp2的漏极连接有第二NMOS管Mn2、栅极连接于第四PMOS管Mp4和第五PMOS管Mp5的栅极;所述第三PMOS管Mp3的栅极连接于所述第三电容C3的一端、源极连接于电源、漏极连接有第三NMOS管Mn3,所述第三电容C3的另一端连接于所述第一NMOS管Mn1的栅极;所述第四PMOS管Mp4的源极连接于所述第五PMOS管Mp5的漏极、漏极连接于所述第四电容C4;所述第五PMOS管Mp5的源极连接于所述第五电容C5、漏极连接于所述第六电容C6和所述第六PMOS管Mp6的栅极;所述第六PMOS管Mp6的源极连接于所述第一电阻R1、漏极连接有第四NMOS管Mn4。

第二NMOS管Mn2的漏极连接于所述第二PMOS管Mp2的漏极和栅极、源极接地、栅极连接于所述第三NMOS管Mn3和所述第四NMOS管Mn4的栅极并同时连接于所述第六PMOS管Mp6的漏极,所述第三NMOS管Mn3的漏极连接于所述第三PMOS管Mp3的漏极、源极接地,所述第四NMOS管Mn4的漏极连接于所述第六PMOS管Mp6的漏极、源极接地。

优选地,所述高性能驱动电路还包括停振检测子电路,所述停振检测子电路连接于所述输出子电路、接收所述输出子电路的输出信号,并输出检测结果。便于用户判断高性能驱动电路的工作状态。

具体地,如图4所示,停振检测子电路通过其CLK_IN端连接于输出子电路并接收时钟信号,停振检测子电路再通过其TOUT端输出检测结果。当停振检测子电路的CLK_IN端接收到输出子电路输出的时钟信号时,停振检测子电路检测到时钟并在其TOUT端输出指示信号“1”;当振荡器子电路的晶体停止振荡,CLK_IN端没有接收到时钟信号时,TOUT端输出指示信号“0”;即可通过判断停振检测子电路输出的指示信号“1”或指示信号“0”来判断高性能驱动电路是否停振。

优选地,所述启动子电路连接于第一使能信号端XTAL_EN,所述启动子电路接收第一使能信号端XTAL_EN输入的第一使能信号以为后续电路提供启动电压。

如图5所示,所述启动子电路包括连接于第一使能信号端XTAL_EN的第七PMOS管Mp7、第八PMOS管Mp8,以及连接于所述第八PMOS管Mp8的第九PMOS管Mp9、连接于所述第九PMOS管Mp9的第十PMOS管Mp10;所述启动子电路还包括连接于第一PMOS管Mp1的第二电阻R2、连接于所述第二电阻R2的第五NMOS管Mn5和第七电容C7,以及连接于所述第十PMOS管Mp10的第六NMOS管Mn6;所述启动子电路的输出端连接于所述第十PMOS管Mp10和第六NMOS管Mn6,以向所述幅值稳压器子电路提供启动电压。

当第一使能信号由高到低切换时,第七PMOS管Mp7和第八PMOS管Mp8开始导通,通过对第七电容C7充放电实现输出端XO电平从高逐渐到低,实现启动目的。

第七PMOS管Mp7和所述第八PMOS管Mp8的栅极连接于所述第一使能信号端XTAL_EN,所述第一使能信号端XTAL_EN接收使能信号以导通所述第七PMOS管Mp7和所述第八PMOS管Mp8;所述第七PMOS管Mp7的源极连接于电源、漏极连接于所述第二电阻R2的一端,所述第二电阻R2的另一端连接于所述第九PMOS管Mp9的栅极、所述第十PMOS管Mp10的栅极、所述第五NMOS管Mn5的漏极和第七电容C7的一端,所述第七电容C7的另一端接地;所述第八PMOS管Mp8的源极连接于电源、漏极连接于所述第九PMOS管Mp9的源极;所述第九PMOS管Mp9的漏极连接于所述第十PMOS管Mp10的源极、所述第十PMOS管Mp10的漏极连接于所述第六NMOS管Mn6的漏极;所述第五NMOS管Mn5和所述第六NMOS管Mn6的源极接地、栅极相互连接并连接于第一使能信号端XTAL_EN。

优选地,所述触发器子电路包括第一信号输入端、第二信号输入端、第三信号输入端和第一输出端;所述第一信号输入端连接于第一使能信号端XTAL_EN以接收第一使能信号;所述第二信号输入端通过第一反相器连接于所述第一使能信号端XTAL_EN,用以接收所述第一使能信号的反向信号;所述第三信号输入端连接于所述振荡器子电路,所述第一输出端连接于所述输出子电路。

优选地,所述触发器子电路为施密特触发器。

如图6所示,触发器子电路包括依次连接的第一场效应管M1、第二场效应管M2、第三场效应管M3、第四场效应管M4、第五场效应管M5和第六场效应管M6,还包括连接于所述第二场效应管M2和第三场效应管M3的第七场效应管M7,以及连接于第四场效应管M4、第五场效应管M5和第七场效应管M7的第八场效应管M8。

具体地,第一场效应管M1的栅极通过反相器连接于第一使能信号端,用以接收所述第一使能信号的反向信号XTAL_ENN。第六场效应管M6的栅极连接于第一使能信号端XTAL_EN以接收第一使能信号。第三场效应管M3、第四场效应管M4、第七场效应管M7和第八场效应管M8连接于输出子电路的输入端Sout。

优选地,输出子电路接收运放子电路和触发器子电路发送的信号进行选择输出。

在具体实施例中,输出子电路为MUX选择器结构的输出子电路。当运放子电路和触发器子电路的信号发送至输出子电路时,通过设置第二使能信号MUX_SEL来选择输出。

在具体实施例中,本发明高性能驱动电路包括有源输入和无源输入两种工作模式。

如图7所示,在无源输入工作模式下,本实施例32.728K晶体连接于X0端和X1端之间,并挂上负载电容C0、C1,其中C0=C1=10p,第一使能信号XTAL_EN在电源上电后1ns由高变为低,第二使能信号MUX_SEL为低。其工作原理为:当第一使能信号XTAL_EN上电之后,幅值稳压子电路接通并使得晶体管Mn获得一个起始电流,这时候晶体管Mn与晶体共振,在X0端和X1端可以测到幅值很大的正弦波信号,即振荡器子电路的输出信号;X0端的正弦波信号反馈发送至到幅值稳压子电路,经过幅值稳压子电路的稳压调节作用,降低了流过晶体管Mn的漏极电流,进而降低X0端的幅值;并且,X0端的正弦波信号通过耦合电容Cc送给运放子电路,以对该信号的幅值进行放大并增加驱动能力;经过运放放大的信号送到输出子电路,经过输出子电路选择输出32.768K时钟,此时停振检测子电路检测到有时钟信号,输出检测信号“1”。

如图8所示,在有源输入工作模式下,在X0端输入有源32.768K时钟,第一使能信号XTAL_EN为高,第二使能信号MUX_SEL为高。其工作原理为:当XO端输入有源32.768K时钟时,触发器子电路接通,并把时钟信号发送至输出子电路,经过输出子电路选择输出32.768K时钟,与无源输入工作模式一样,此时停振检测电路检测到有时钟信号,输出检测信号“1”。

应当理解的是,以上仅为本发明的优选实施例,不能因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

- 一种高性能晶体驱动电路

- 一种高性能光电功能晶体硼酸钙氧铥晶体及其生长与应用