半导体装置以及其形成方法

文献发布时间:2023-06-19 11:52:33

技术领域

本发明是有关于一种半导体装置,且特别是有关于高电子迁移率晶体管装置(high electron mobility transistor,HEMT)以及其形成方法。

背景技术

高电子迁移率晶体管,又称为异质结构场效应晶体管(heterostructure fieldeffect transistor,HFET)或调制掺杂场效应晶体管(modulation-doped field effecttransistor,MODFET),为一种场效应晶体管,其由具有不同能隙(energy gap)的半导体材料组成。在邻近不同半导体材料之间的界面处会产生二维电子气层。由于二维电子气的高电子移动性,高电子迁移率晶体管装置可具有高击穿电压、高电子迁移率、低导通电阻及低输入电容等优点,因而适合用于高功率元件上。

虽然现存的高电子迁移率晶体管装置可大致满足它们原先预定的用途,但其仍未在各个方面皆彻底地符合需求。发展出可进一步改善高电子迁移率晶体管装置的效能及可靠度的结构及制造方法仍为目前业界致力研究的课题之一。

发明内容

根据本发明一些实施例,提供一种半导体装置,半导体装置包含基板、栅极电极、第一介电层、源极场板、第二介电层、源极电极以及漏极电极。栅极电极设置于基板上。第一介电层设置于栅极电极上且具有第一凹槽以及第二凹槽。源极场板设置于第一介电层上,且延伸设置于第一凹槽以及第二凹槽内。第二介电层设置于源极场板上。源极电极设置于第二介电层上且与源极场板电连接。漏极电极设置于第二介电层上,且漏极电极与源极电极设置于栅极电极的相对两侧。并且,第一凹槽与第二凹槽位于栅极电极与漏极电极之间。

根据本发明一些实施例,提供一种半导体装置的形成方法,半导体装置的形成方法包含以下步骤:提供基板;形成栅极电极于基板上;形成第一介电层于栅极电极上;移除第一介电层的一部分,以于第一介电层中形成第一凹槽;移除第一介电层的另一部分,以于第一介电层中形成第二凹槽,其中第一凹槽与第二凹槽相连;顺应性地形成源极场板于第一介电层上,其中源极场板延伸于第一凹槽以及第二凹槽内;形成第二介电层于源极场板上;形成源极电极于第二介电层上,其中源极电极与源极场板电连接;以及形成漏极电极于第二介电层上,其中漏极电极与源极电极位于栅极电极的相对两侧。

为让本发明的特征明显易懂,下文特举出实施例,并配合所附图式,作详细说明如下,其他注意事项,请参照技术领域。

附图说明

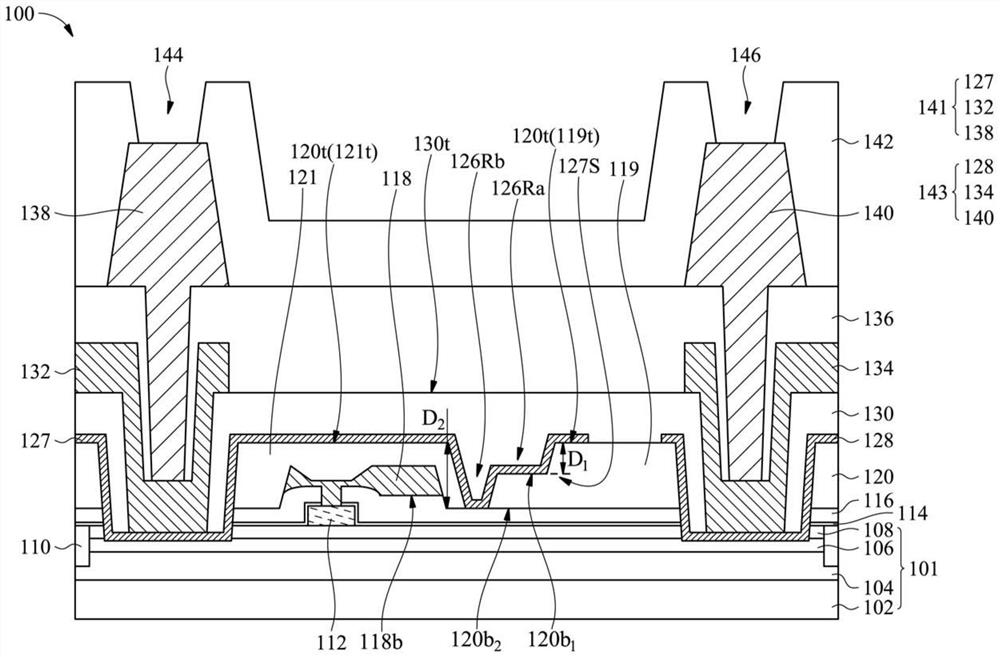

图1A至图1H显示根据本发明一些实施例中,半导体装置于工艺中各个阶段的剖面结构示意图;

图2显示根据本发明一些实施例中,半导体装置的剖面结构示意图。

符号说明

100、200 半导体装置;

101 基板;

102 基底;

104 缓冲层;

106 通道层;

108 阻挡层;

110 隔离结构;

112 化合物半导体层;

114、116、120、130、136 介电层;

116t、120t、121t、119t、130t 顶表面;

118 栅极电极;

118b 闸底面;

119 第一部分;

120b

120b

121 第二部分;

121’ 第三部分;

122、124 通孔;

126Ra 第一凹槽;

126Rb 第二凹槽;

127 源极场板;

127S 阶梯状结构;

128 导电层;

132 源极电极;

134 漏极电极;

138 源极接触件;

140 漏极接触件;

141 源极结构;

142 保护层;

143 漏极结构;

144、146 开口;

D

具体实施方式

以下针对本发明实施例的半导体装置以及其形成方法作详细说明。应了解的是,以下的叙述提供许多不同的实施例或例子,用以实施本发明一些实施例的不同态样。以下所述特定的元件及排列方式仅为简单清楚描述本发明一些实施例。当然,这些仅用以举例而非本发明的限定。此外,在不同实施例中可能使用类似及/或对应的标号标示类似及/或对应的元件,以清楚描述本发明。然而,这些类似及/或对应的标号的使用仅为了简单清楚地叙述本发明一些实施例,不代表所讨论的不同实施例及/或结构之间具有任何关联性。

本发明实施例可配合图式一并理解,本发明的图式亦被视为揭露说明的一部分。应理解的是,本发明的图式并未按照比例绘制,事实上,可能任意的放大或缩小元件的尺寸以便清楚表现出本发明的特征。应理解的是,图式的元件或装置可以发明所属技术领域的相关技术人员所熟知的各种形式存在。此外实施例中可能使用相对性用语,例如“较低”或“底部”或“较高”或“顶部”,以描述图式的一个元件对于另一元件的相对关系。可理解的是,如果将图式的装置翻转使其上下颠倒,则所叙述在“较低”侧的元件将会成为在“较高”侧的元件。

再者,当述及一第一材料层位于一第二材料层上或之上时,可能包括第一材料层与第二材料层直接接触的情形或第一材料层与第二材料层之间可能不直接接触,亦即第一材料层与第二材料层之间可能间隔有一或更多其它材料层的情形。但若第一材料层直接位于第二材料层上时,即表示第一材料层与第二材料层直接接触的情形。

此外,应理解的是,虽然在此可使用用语“第一”、“第二”、“第三”等来叙述各种元件、组件、或部分,这些元件、组件或部分不应被这些用语限定。这些用语仅是用来区别不同的元件、组件、区域、层或部分。因此,以下讨论的一第一元件、组件、区域、层或部分可在不偏离本发明的教示的情况下被称为一第二元件、组件、区域、层或部分。

除非另外定义,在此使用的全部用语(包含技术及科学用语)具有与本发明所属技术领域的相关技术人员通常理解的相同涵义。能理解的是,这些用语例如在通常使用的字典中定义用语,应被解读成具有与相关技术及本发明的背景或上下文一致的意思,而不应以一理想化或过度正式的方式解读,除非在本发明实施例有特别定义。

根据本发明一些实施例,提供的半导体装置包含延伸于介电层的凹槽内的场板(field plate),设置于凹槽内的场板可屏蔽栅极电极,降低电场对栅极电极的干扰。此外,根据本发明一些实施例,半导体装置的场板可具有阶梯状(stepped shape)结构,藉此可减少场板设置的数量,降低栅极电极与漏极区之间产生的电容,以及简化工艺。

图1A至图1H显示根据本发明一些实施例中,半导体装置100于工艺中各个阶段的剖面结构示意图。应理解的是,可于形成半导体装置100的工艺进行前、进行中及/或进行后提供额外的操作。在不同的实施例中,所述的一些阶段可以被取代或删除。可添加额外特征于半导体装置100,在不同的实施例中,以下所述的半导体装置100的部分特征可以被取代或删除。

请参照图1A,根据一些实施例,提供基底102。基底102可为块状(bulk)半导体基底或包含不同材料的复合基底。在一些实施例中,基底102可包含半导体基底、玻璃基底、或陶瓷基底、蓝宝石(sapphire)基底、其它合适的基底、或前述的组合。在一些实施例中,基底102可包含绝缘体上覆半导体(semiconductor-on-insulator,SOI)基底,其经由在绝缘层上设置半导体材料所形成。

详细而言,在基底102为半导体基底的一些实施例中,基底102可由元素半导体材料形成,例如硅(Ge)、锗(Ge)、或其它合适的元素半导体材料。在一些实施例中,基底102可由化合物半导体材料形成,例如,碳化硅(SiC)、氮化铝(AlN)、氮化镓(GaN)、砷化镓(GaAs)、砷化铟(InAs)、磷化铟(InP)、或前述的组合。在一些实施例中,基底102可由合金半导体材料,例如,硅化锗(SiGe)、碳化硅锗(SiGeC)、磷化砷镓(GaP)、磷化铟镓(InGaP)、或前述的组合。此外,基底102可为经掺杂的(例如,以p型或n型掺质进行掺杂)或未经掺杂的。

如图1A所示,根据一些实施例,可形成缓冲层104于基底102上方,以缓解基底102与缓冲层104上的膜层之间的晶格差异,提升结晶品质。在一些实施例中,缓冲层104的材料可包含III-V族化合物半导体材料,例如III族氮化物。举例而言,在一些实施例中,缓冲层104的材料可包含氮化镓(GaN)、氮化铝(AlN)、氮化铝镓(AlGaN)、氮化铝铟(AlInN)、其它合适的缓冲材料、或前述的组合。在一些实施例中,可藉由化学气相沉积(chemical vapordeposition,CVD)工艺、分子束外延工艺、液相外延工艺、其它合适的工艺、或前述的组合形成缓冲层104。前述化学气相沉积工艺例如可包含低压化学气相沉积(low pressurechemical vapor deposition,LPCVD)工艺、低温化学气相沉积(low temperaturechemical vapor deposition,LTCVD)工艺、快速升温化学气相沉积(rapid thermalchemical vapor deposition,RTCVD)工艺、等离子增强型化学气相沉积(plasma enhancedchemical vapor deposition,PECVD)工艺、或原子层沉积(atomic layer deposition,ALD)工艺。

此外,虽然于图1A所绘示的实施例中,缓冲层104直接形成于基底102上,但在另一些实施例中,可于形成缓冲层104之前,于基底102上形成成核层(未绘示),以进一步缓解缓冲层104与基底102之间的晶格差异,提升结晶品质。在一些实施例中,成核层的材料可包含III-V族化合物半导体材料,例如III族氮化物。

根据一些实施例,接着,可形成通道层106于缓冲层104上方。在一些实施例中,通道层106的材料可包含一或多种III-V族化合物半导体材料,例如III族氮化物。举例而言,在一些实施例中,通道层106的材料可包含氮化镓(GaN)、氮化铝镓(AlGaN)、氮化铟镓(InGaN)、氮化铝镓铟(AlGaInN)、其它合适的材料、或前述的组合。此外,通道层106可为经掺杂的(例如,以p型或n型掺质进行掺杂)或未经掺杂的。在一些实施例中,可藉由前述化学气相沉积工艺、分子束外延工艺、液相外延工艺、其它合适的工艺、或前述的组合形成通道层106。

根据一些实施例,接着,可形成阻挡层108于通道层106上方,以于通道层106及阻挡层108之间的界面产生二维电子气(two-dimensional electron gas,2DEG)。在一些实施例中,阻挡层108的材料可包含III-V族化合物半导体材料,例如III族氮化物。举例而言,在一些实施例中,阻挡层108可包含氮化铝(AlN)、氮化铝镓(AlGaN)、氮化铝铟(AlInN)、氮化铝镓铟(AlGaInN)、其它合适的材料、或前述的组合。阻挡层108可包含单层或多层结构,且阻挡层108可为经掺杂的(例如,以p型或n型掺质进行掺杂)或未经掺杂的。在一些实施例中,可藉由前述化学气相沉积工艺、分子束外延工艺、液相外延工艺、其它合适的工艺、或前述的组合形成阻挡层108。

此外,为了简化叙述,可以将基底102、缓冲层104、通道层106以及阻挡层108统称为基板101。

根据一些实施例,接着,可进一步形成隔离结构110于基板101中。具体而言,在一些实施例中,可于基板101上设置遮罩层(未绘示),接着使用上述遮罩层作为刻蚀遮罩进行刻蚀工艺,以于基板101中形成沟槽。举例而言,遮罩层可包含光阻,例如,正型光阻(positive photoresist)或负型光阻(negative photoresist)。在一些实施例中,遮罩层可包含硬遮罩,且硬遮罩的材料可包含氧化硅(SiO

此外,在一些实施例中,前述刻蚀工艺可包含干式刻蚀工艺、湿式刻蚀工艺、或前述的组合。举例而言,干式刻蚀工艺可包含反应性离子刻蚀(reactive ion etch,RIE)、感应耦合式等离子体(inductively-coupled plasma,ICP)刻蚀、中子束刻蚀(neutral beametch,NBE)、电子回旋共振式(electron cyclotron resonance,ERC)刻蚀、其他合适的刻蚀工艺、或前述的组合。再者,湿式刻蚀工艺可使用例如氢氟酸(hydrofluoric acid,HF)、氢氧化铵(ammonium hydroxide,NH

根据一些实施例,接着,可于沟槽中沉积绝缘材料以形成隔离结构110。在一些实施例中,可藉由金属有机化学气相沉积工艺、原子层沉积工艺、分子束外延工艺、液相外延工艺、其它合适的工艺、或前述的组合沉积绝缘材料。在一些实施例中,绝缘材料可包含例如氧化硅的氧化物、例如氮化硅的氮化物、其它合适的材料、或前述的组合。

根据一些实施例,接着,可形成化合物半导体层112于阻挡层108上方,以空乏栅极结构下方的二维电子气,达成半导体装置的常关(normally-off)状态。在一些实施例中,可藉由前述化学气相沉积工艺、分子束外延工艺、液相外延工艺、其它合适的工艺、或前述的组合,形成化合物半导体层112的材料于阻挡层108上方。在一些实施例中,化合物半导体层112的材料可包含u型、n型或p型掺杂的氮化镓,并且可使用掺质进行掺杂。

根据一些实施例,接着,可进行图案化工艺以根据预定设置栅极的位置调整化合物半导体层112的位置。在一些实施例中,图案化工艺包含于形成化合物半导体层112的材料层上形成遮罩层(未绘示),然后刻蚀移除未被遮罩层覆盖的材料层的部分,以形成化合物半导体层112。关于遮罩层的材料、形成方式以及刻蚀工艺的详细内容如同前文所述,于此便不再赘述。

根据一些实施例,接着,可顺应性地(conformally)形成介电层114于阻挡层108、隔离结构110以及化合物半导体层112上。在一些实施例中,介电层114的材料可包含氧化硅、氮化硅、氮氧化硅、氧化铝、氮化铝、其它合适的低介电常数介电材料、或前述的组合。在一些实施例中,可藉由前述化学气相沉积工艺、旋转涂布工艺、其它合适的工艺、或前述的组合形成介电层114。

根据一些实施例,接着,可形成介电层116于介电层114上。在一些实施例中,介电层116的材料以及形成方法可与前述介电层114的材料以及形成方法相同或相似,于此便不再赘述。根据一些实施例,可依照实际需求设置介电层114及/或介电层116。

根据一些实施例,接着,可对介电层114以及介电层116进行图案化工艺,以移除一部分的介电层114和介电层116,形成暴露出化合物半导体层112的开口。在一些实施例中,图案化工艺的详细步骤可与前述化合物半导体层112的图案化工艺相同或相似,于此便不再赘述。

根据一些实施例,接着,可形成栅极电极118于介电层116上,并填入开口中。在一些实施例中,栅极电极118的材料可包含导电材料,例如,金属、金属硅化物、其它合适的导电材料、或前述的组合。举例而言,金属可包含金(Au)、镍(Ni)、铂(Pt)、钯(Pd)、铱(Ir)、钛(Ti)、铬(Cr)、钨(W)、铝(Al)、铜(Cu)、前述的合金、其它合适的材料、或前述的组合。在一些实施例中,可藉由前述化学气相沉积工艺、物理气相沉积工艺、蒸镀(evaporation)工艺、溅射(sputtering)工艺、其它合适的工艺、或前述的组合形成栅极电极118。

根据一些实施例,接着,可对栅极电极118进行图案化工艺。图案化工艺的详细步骤如前所述,于此便不再赘述。如图1A所示,在一些实施例中,于图案化工艺之后,栅极电极118的最大宽度可大于化合物半导体层112的最大宽度。

接着,请参照图1B,根据一些实施例,可形成介电层120于介电层116以及栅极电极118上,介电层116可完整地覆盖栅极电极118。在一些实施例中,介电层120可包含氧化硅、氮化硅、氮氧化硅、氧化铝、氮化铝、其它合适的低介电常数介电材料、或前述的组合。在一些实施例中,可藉由化学气相沉积工艺、旋转涂布工艺、其它合适的工艺、或前述的组合形成介电层120。在一些实施例中,于沉积介电层120之后,可对介电层120进行平坦化工艺,例如,化学机械研磨工艺。

根据一些实施例,接着,可对介电层120进行图案化工艺,移除介电层120的一部分,以于介电层120中形成通孔122以及通孔124。在一些实施例中,通孔122以及通孔124可设置于栅极电极118的两侧,且通孔122以及通孔124可暴露出一部分的通道层106。图案化工艺的详细步骤如前所述,于此便不再赘述。

接着,根据一些实施例,可对介电层120进行图案化工艺,移除介电层120的一部分,以于介电层120中形成第一凹槽126Ra,第一凹槽126Ra可邻近于栅极电极118。在一些实施例中,第一凹槽126Ra可设置于通孔122以及通孔124之间。在一些实施例中,第一凹槽126Ra比通孔122以及通孔124更靠近栅极电极118。如图1C所示,第一凹槽126Ra可从介电层120的顶表面120t延伸至介电层120的第一底表面120b

在一些实施例中,第一凹槽126Ra可具有深度D

接着,请参照图1D,根据一些实施例,可再次对介电层120进行图案化工艺,移除介电层120的另一部分,以于介电层120中形成第二凹槽126Rb。在一些实施例中,第一凹槽126Ra与第二凹槽126Rb位于栅极电极118与漏极电极134之间。在一些实施例中,第二凹槽126Rb亦设置于通孔122以及通孔124之间。在一些实施例中,第二凹槽126Rb比通孔122以及通孔124更靠近栅极电极118。在一些实施例中,第二凹槽126Rb比第一凹槽126Ra更靠近栅极电极118。

如图1D所示,第二凹槽126Rb可从介电层120的顶表面120t延伸至介电层116的一部分的顶表面116t(或介电层120的第二底表面120b

在一些实施例中,第二凹槽126Rb可具有深度D

值得注意的是,如图1D所示,第一凹槽126Ra可与第二凹槽126Rb相连,例如,第一凹槽126Ra以及第二凹槽126Rb可为彼此相通的连续性凹槽。在一些实施例中,由于第一凹槽126Ra的深度D

然而,应理解的是,虽然图式中所绘示的实施例中介电层120具有第一凹槽126Ra以及第二凹槽126Rb这两个凹槽所定义的具有阶梯状轮廓的凹槽,但根据另一些实施例,介电层120可具有由其它合适数量的凹槽所共同定义的凹槽,例如,3个、4个、5个、或其它合适的数量。

再者,在一些实施例中,第一凹槽126Ra以及第二凹槽126Rb可将介电层120分成第一部分119以及第二部分121,且第一凹槽126Ra以及第二凹槽126Rb将第一部分119以及第二部分121隔开。在一些实施例中,第一部分119以及第二部分121分别设置于第一凹槽126Ra以及第二凹槽126Rb的相反两侧。在一些实施例中,第一凹槽126Ra未贯穿介电层120,第一凹槽126Ra贯穿介电层120。

此外,在一些实施例中,可于形成通孔122以及通孔124的图案化工艺之前、期间或之后,进行第一凹槽126Ra以及第二凹槽126Rb的图案化工艺,可于形成通孔122之前、期间或之后形成通孔124,且可于形成第一凹槽126Ra之前、期间或之后形成第二凹槽126Rb。

接着,请参照图1E,根据一些实施例,可顺应性地形成源极场板127于介电层120上,且源极场板127延伸于第一凹槽126Ra以及第二凹槽126Rb内。在一些实施例中,源极场板127可与设置于栅极电极118与化合物半导体层112之间的介电层116直接接触。在一些实施例中,源极场板127亦延伸于通孔122内。详细而言,在一些实施例中,源极场板127从介电层120的第二部分121的顶表面121t延伸至第一部分119的顶表面119t。此外,如图1E所示,在一些实施例中,延伸于第一凹槽126Ra以及第二凹槽126Rb内的源极场板127可包含阶梯状结构127S。

另一方面,根据一些实施例,可顺应性地形成导电层128于介电层120上,且导电层128可延伸于通孔124内。在一些实施例中,导电层128可设置于第一部分119的一部分的顶表面119t上。

在一些实施例中,源极场板127以及导电层128的材料可包含导电材料,例如,金属、金属硅化物、其它合适的导电材料、或前述的组合。举例而言,金属可包含金(Au)、镍(Ni)、铂(Pt)、钯(Pd)、铱(Ir)、钛(Ti)、铬(Cr)、钨(W)、铝(Al)、铜(Cu)、前述的合金、其它合适的材料、或前述的组合。在一些实施例中,可藉由前述化学气相沉积工艺、物理气相沉积工艺、蒸镀工艺、溅射工艺、其它合适的工艺、或前述的组合形成源极场板127以及导电层128。此外,在一些实施例中,可藉由刻蚀工艺移除位于介电层120的第一部分119上的部分导电材料,以暴露出第一部分119的一部分的顶表面119t。

值得注意的是,根据一些实施例,延伸于第一凹槽126Ra以及第二凹槽126Rb内的源极场板127可屏蔽栅极电极118,降低电场对栅极电极118的干扰。此外,根据一些实施例,具有阶梯状结构127S的源极场板127可减少后续所需设置的场板数量,藉此降低场板金属层之间产生寄生电容的风险,并且可简化工艺。

接着,请参照图1F,根据一些实施例,形成介电层130于源极场板127以及导电层128上。在一些实施例中,介电层130亦填充于第一凹槽126Ra以及第二凹槽126Rb内。在一些实施例中,可藉由沉积工艺以及平坦化工艺等形成介电层130,且介电层130的材料以及形成方法可与前述介电层120的材料以及形成方法相同或相似,于此便不再赘述。接着,根据一些实施例,可对介电层130进行图案化工艺以再次形成通孔122以及通孔124,通孔122以及通孔124分别暴露出一部分的源极场板127以及导电层128。图案化工艺的详细步骤如前所述,于此便不再赘述。

接着,请参照图1G,根据一些实施例,形成源极电极132以及漏极电极134于介电层130上。在一些实施例中,介电层120的第一部分119邻近于漏极电极134,介电层120的第二部分121邻近于源极电极132。在一些实施例中,源极电极132以及漏极电极134可分别藉由通孔122以及通孔124与源极场板127以及导电层128电连接。在一些实施例中,漏极电极134与源极电极132位于栅极电极118的相对两侧。

如图1G所示,在一些实施例中,前述第一凹槽126Ra以及第二凹槽126Rb位于该源极电极132以及漏极电极134之间。在一些实施例中,源极场板127的阶梯状结构127S设置于源极电极132以及漏极电极134之间。在一些实施例中,源极电极132与栅极电极118不重叠。在一些实施例中,源极电极132与阶梯状结构127S不重叠。

在一些实施例中,源极电极132以及漏极电极134的材料可包含导电材料,例如,金属、金属硅化物、其它合适的导电材料、或前述的组合。举例而言,金属可包含金(Au)、镍(Ni)、铂(Pt)、钯(Pd)、铱(Ir)、钛(Ti)、铬(Cr)、钨(W)、铝(Al)、铜(Cu)、前述的合金、其它合适的材料、或前述的组合。在一些实施例中,可藉由前述化学气相沉积工艺、物理气相沉积工艺、蒸镀工艺、溅射工艺、其它合适的工艺、或前述的组合形成导电材料。在一些实施例中,可对导电材料进行图案化工艺以形成源极电极132以及漏极电极134,图案化工艺的详细步骤如前所述,于此便不再赘述。

接着,根据一些实施例,可形成介电层136于介电层130上,且介电层136覆盖源极电极132以及漏极电极134。在一些实施例中,可藉由沉积工艺以及平坦化工艺等形成介电层136,且介电层136的材料以及形成方法可与前述介电层120的材料以及形成方法相同或相似,于此便不再赘述。接着,根据一些实施例,可对介电层136进行图案化工艺以再次形成通孔122以及通孔124,通孔122以及通孔124分别暴露出一部分的源极电极132以及漏极电极134。图案化工艺的详细步骤如前所述,于此便不再赘述。

接着,请参照图1H,根据一些实施例,形成源极接触件138以及漏极接触件140于介电层136上。在一些实施例中,源极接触件138以及漏极接触件140可穿过介电层136,分别与源极电极132以及漏极电极134电连接,换言之,源极接触件138以及漏极接触件140可分别藉由通孔122以及通孔124(如图1G所示)与源极电极132以及漏极电极134电连接。

在一些实施例中,源极接触件138以及漏极接触件140的材料可包含导电材料,例如,金属、金属硅化物、其它合适的导电材料、或前述的组合。举例而言,金属可包含金(Au)、镍(Ni)、铂(Pt)、钯(Pd)、铱(Ir)、钛(Ti)、铬(Cr)、钨(W)、铝(Al)、铜(Cu)、前述的合金、其它合适的材料、或前述的组合。在一些实施例中,可藉由前述化学气相沉积工艺、物理气相沉积工艺、蒸镀工艺、溅射工艺、其它合适的工艺、或前述的组合形成导电材料。在一些实施例中,可对导电材料进行图案化工艺以形成,源极接触件138以及漏极接触件140,图案化工艺的详细步骤如前所述,于此便不再赘述。

根据一些实施例,可进一步形成保护层142于源极接触件138以及漏极接触件140上以阻挡水气。在一些实施例中,保护层142可包含任何合适的介电材料,例如,氧化硅、氮化硅、氮氧化硅、低介电常数介电材料、氧化铝、氮化铝、其它合适的材料、或前述的组合。在一些实施例中,可藉由前述化学气相沉积工艺、旋转涂布工艺、其它合适的工艺、或前述的组合形成保护层142。之后,根据一些实施例,可对保护层142进行图案化工艺以形成开口144以及开口146,开口144以及开口146可分别暴露出源极接触件138以及漏极接触件140。

为了简化叙述,可以将源极场板127、源极电极132以及源极接触件138统称为源极结构141,并且可以将导电层128、漏极电极134以及漏极接触件140统称为漏极结构143。

根据一些实施例,如图1H所示,位于第一凹槽126Ra以及第二凹槽126Rb内的源极场板127具有阶梯状结构127S,且源极场板127覆盖介电层120的第二部分121,藉此可降低来自漏极结构143的电场对栅极电极118造成的影响且可吸取因界面漏电流所造成的电荷累积。于较佳实施例中,第二底表面120b

此外,根据一些实施例,由于具有阶梯状结构127S的源极场板127已可有效地屏蔽漏极结构143的电场影响,因此不需于介电层130的顶表面130t上设置额外的场板结构,例如,源极电极132不须进一步延伸于顶表面130t上以与栅极电极118重叠,如此一来,亦可降低栅极电极118与其它场板结构之间产生大量电容的风险,并且可简化工艺。

接着,请参照图2,图2显示根据本发明另一些实施例中,半导体装置200的剖面结构示意图。图2所示的半导体装置200与图1H所示的半导体装置100大致上相似,其差异在于在半导体装置200中,第一凹槽126Ra以及第二凹槽126Rb可分开一段距离,一部分的介电层(第三部分121’)设置于第一凹槽126Ra以及第二凹槽126Rb之间。于此实施例中,第一凹槽126Ra以及第二凹槽126Rb可为非连续性(或称不相连)的凹槽结构。换言之,于此实施例中,第一凹槽126Ra以及第二凹槽126Rb可为不相连的。于此实施例中,第一凹槽126Ra的深度可大于、等于或小于第二凹槽126Rb的深度。

进一步而言,于此实施例中,第一凹槽126Ra以及第二凹槽126Rb可将介电层120分成第一部分119、第二部分121以及第三部分121’,且第一凹槽126Ra以及第二凹槽126Rb可将第一部分119、第二部分121以及第三部分121’隔开。再者,于此实施例中,第一凹槽126Ra以及第二凹槽126Rb两者均可贯穿介电层120。根据本发明一些实施例,提供一种半导体装置。半导体装置可包含基板、栅极电极、介电层、源极场板、第二介电层、源极电极以及漏极电极。栅极电极可设置于基板上。第一介电层可设置于栅极电极上且具有第一凹槽以及第二凹槽。源极场板可设置于第一介电层上,且延伸设置于第一凹槽以及第二凹槽内。第二介电层可设置于源极场板上。源极电极可设置于第二介电层上且与源极场板电连接。漏极电极可设置于第二介电层上,且漏极电极与源极电极可设置于栅极电极的相对两侧,且第一凹槽与第二凹槽位于栅极电极与漏极电极之间。

在一些实施例中,第一凹槽贯穿第一介电层,且第二凹槽未贯穿第一介电层。在一些实施例中,第一凹槽与第二凹槽分别具有第一底表面与第二底表面,栅极电极具有闸底面,且第一底表面及/或第二底表面较闸底面邻近基板。

在一些实施例中,源极场板可包含阶梯状结构,阶梯状结构可设置于第一凹槽以及第二凹槽中。在一些实施例中,源极电极与阶梯状结构不重叠。在一些实施例中,阶梯状结构可设置于源极电极以及漏极电极之间。

在一些实施例中,第一凹槽的深度与第二凹槽的深度不同。在一些实施例中,第一凹槽以及第二凹槽相连。在一些实施例中,源极电极与栅极电极不重叠。

在一些实施例中,前述半导体装置可进一步包含第三介电层,第三介电层可设置于第二介电层上且覆盖源极电极与漏极电极。在一些实施例中,前述半导体装置可进一步包含源极接触件以及漏极接触件,源极接触件以及漏极接触件可设置于第三介电层上,其中源极接触件以及漏极接触件穿过第三介电层,分别与源极电极以及漏极电极电连接。在一些实施例中,前述半导体装置可进一步包含第四介电层,第四介电层可设置于栅极电极与半导体基板之间,其中源极场板与第四介电层直接接触。

在一些实施例中,第一介电层可包含第一部分以及第二部分,第一凹槽以及第二凹槽将第一部分以及第二部分隔开。在一些实施例中,第一部分邻近于漏极电极,第二部分邻近于源极电极,源极场板从第二部分延伸至第一部分。在一些实施例中,源极场板从第二部分的顶表面延伸至第一部分的顶表面。

根据本发明一些实施例,提供一种半导体装置的形成方法,包含以下步骤:提供半导体基板;形成栅极电极于半导体基板上;形成第一介电层于栅极电极上;移除第一介电层的一部分,以于第一介电层中形成第一凹槽;移除第一介电层的另一部分,以于第一介电层中形成第二凹槽;顺应性地形成源极场板于第一介电层上,其中源极场板延伸于第一凹槽以及第二凹槽内;形成第二介电层于源极场板上;形成源极电极于第二介电层上,其中源极电极与源极场板电连接;以及形成漏极电极于第二介电层上,其中漏极电极与源极电极位于栅极电极的相对两侧,且第一凹槽与第二凹槽位于栅极电极与漏极电极之间。

在一些实施例中,第一凹槽以及第二凹槽相连,且第一凹槽的深度与第二凹槽的深度不同。在一些实施例中,延伸于第一凹槽以及第二凹槽内的源极场板包括阶梯状结构。在一些实施例中,第二凹槽贯穿第一介电层。

在一些实施例中,前述半导体装置的形成方法可进一步包含:形成第三介电层于第二介电层上且覆盖源极电极与漏极电极;以及形成源极接触件以及漏极接触件于第三介电层上,其中源极接触件以及漏极接触件穿过第三介电层,分别与源极电极以及漏极电极电连接。

虽然本发明的实施例已揭露如上,但应该了解的是,任何所属技术领域中的相关技术人员,在不脱离本发明的精神和范围内,当可作更动、替代与润饰。此外,本发明的保护范围并未局限于说明书内所述特定实施例中的工艺、机器、制造、物质组成、装置、方法及步骤,任何所属技术领域中的相关技术人员可从本发明揭示内容中理解现行或未来所发展出的工艺、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结果皆可根据本发明使用。因此,本发明的保护范围包括上述工艺、机器、制造、物质组成、装置、方法及步骤。另外,每一权利要求范围构成个别的实施例,且本发明的保护范围也包括各个权利要求范围及实施例的组合。本发明的保护范围当视前述的权利要求范围所界定者为准。

- 芯片封装及其形成方法、半导体器件及其形成方法、半导体装置及其形成方法、三相系统

- 半导体膜的形成方法、半导体器件的形成方法和半导体器件