多相位串行数据采样时钟信号的产生电路

文献发布时间:2024-01-17 01:26:37

技术领域

本发明涉及分频电路,具体涉及一种多相位串行数据采样时钟信号的产生电路。

背景技术

在低电压差分信号的移动产业处理器接口(mipi-LVDS)和低电压差分信号的摄像头/显示接口(LVDS Camera/Display)应用中,需要输出在1位数据周期内相位有16个档位可选的时钟。比如,串行数据率达1Gbps,那么需要 1ns/16=62.5ps步骤调节。

通常在串行数据率为1Gbps的情况下,现有技术通过锁相环(PLL)产生4GHz的4相时钟,然后通过相应的逻辑电路产生4GHz多相时钟,使用4GHz多相时钟对双倍数据速率时钟进行采样,并选通需要的相位时钟。但是,现有技术这种方法的电路结构较为复杂,功率消耗较大,版图实现的面积较大,成本较高。

发明内容

本发明的目的在于:提供一种多相位串行数据采样时钟信号的产生电路,能够实现输出16个档位可选的采样时钟,以此实现在1位数据周期内相位有16个档位可选的功能。

本发明通过下述技术方案实现:

一种多相位串行数据采样时钟信号的产生电路,包括:

四相时钟信号产生电路,其用于产生第一相时钟信号、第二相时钟信号、第三相时钟信号和第四相时钟信号;其中,第一相时钟信号和第三相时钟信号为一对差分时钟信号,第二相时钟信号和第四相时钟信号为另一对差分时钟信号;

第一四选一选择器,其输入端分别输入第一相时钟信号、第二相时钟信号、第三相时钟信号和第四相时钟信号,其控制端分别输入第一位控制信号和第二位控制信号,其输出端输出第一时钟信号;

二选一选择器,其输入端分别输入第二相时钟信号和第四相时钟信号,其控制端输入第二位控制信号,其输出端输出第二时钟信号;

第一采样电路,其用于第四相时钟信号对第三时钟信号进行采样得到第四时钟信号;

第二采样电路,其用于第二时钟信号对第四时钟信号进行采样得到第五时钟信号;

第三采样电路,其用于第一时钟信号对第五时钟信号进行采样得到第六时钟信号;

第四采样电路,其用于第一时钟信号对第六时钟信号进行采样得到第七时钟信号;

第五采样电路,其用于第一时钟信号对第七时钟信号进行采样得到第八时钟信号;

第六采样电路,其用于第一时钟信号对第八时钟信号进行采样得到第九时钟信号;

第二四选一选择器,其输入端分别输入第六时钟信号、第七时钟信号、第八时钟信号和第九时钟信号,其控制端分别输入第三位控制信号和第四位控制信号,其输出端输出开关控制信号;

第一四分频电路,其在开关控制信号的控制下对第一时钟信号进行四分频得到第一分频信号;

第二四分频电路,其在开关控制信号的控制下对第一分频信号进行四分频得到第二分频信号;

其中,电路控制信号包括四位位控制信号,四位位控制信号分别为所述第一位控制信号、第二位控制信号第三位控制信号和第四位控制信号。

所述四相时钟信号产生电路为压控振荡器。

所述第一采样电路、第二采样电路、第三采样电路、第四采样电路、第五采样电路、第六采样电路均为D触发器。

所述第三时钟信号由锁定检测电路产生。

本发明与现有技术相比,具有以下有益技术效果:

本发明结构简单,所使用的信号较少,逻辑电路实现更方便,而且功率消耗较低,版图所需面积较小,能够降低成本。

附图说明

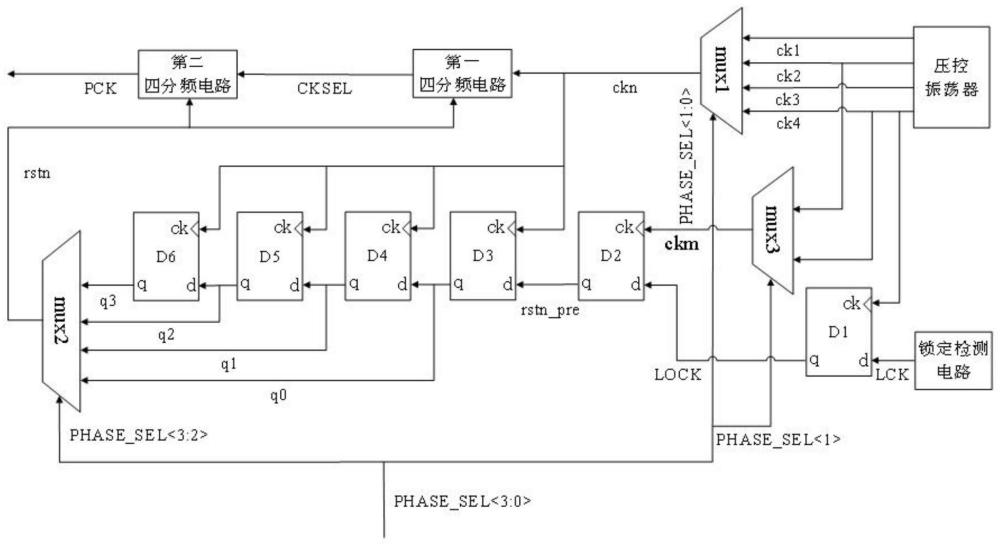

图1为本发明的电路原理图;

图2为PHASE_SEL〈3:0〉=0000时的信号时序图。

具体实施方式

本说明书中公开的所有特征,或公开的所有方法或过程中的步骤,除了相互排斥的特质和/或步骤以外,均可以以任何方式组合,除非特别叙述,均可被其他等效或具有类似目的的替代特征加以替换,即,除非特别叙述,每个特征为一系列等效或类似特征中的一个实施例而已。

参见图1,本发明的一种多相位串行数据采样时钟信号的产生电路,包括四相时钟信号产生电路、第一四选一选择器mux1、二选一选择器mux3、第一采样电路D1、第二采样电路D2、第三采样电路D3、第四采样电路D4、第五采样电路D5、第六采样电路D6、第二四选一选择器mux2、第一四分频电路和第二四分频电路。

四相时钟信号产生电路用于产生第一相时钟信号ck1、第二相时钟信号ck2、第三相时钟信号ck3和第四相时钟信号ck4。第一相时钟信号ck1和第三相时钟信号ck3为一对差分时钟信号,第二相时钟信号ck2和第四相时钟信号ck4为另一对差分时钟信号。图1所呈现的实施例中,四相时钟信号产生电路为压控振荡器。第一相时钟信号ck1、第二相时钟信号ck2、第三相时钟信号ck3和第四相时钟信号ck4的频率根据串行数据率确定,有具体的倍数关系,比如,第一相时钟信号ck1、第二相时钟信号ck2、第三相时钟信号ck3和第四相时钟信号ck4的频率可以是串行数据率的四倍,比如,本实施例中,串行数据率小于等于1Gbps,那么以最高串行数据率1Gbps为标准确定第一相时钟信号ck1、第二相时钟信号ck2、第三相时钟信号ck3和第四相时钟信号ck4的频率,即第一相时钟信号ck1、第二相时钟信号ck2、第三相时钟信号ck3和第四相时钟信号ck4的频率为4GHz。

第一四选一选择器mux1的输入端分别输入第一相时钟信号ck1、第二相时钟信号ck2、第三相时钟信号ck3和第四相时钟信号ck4,第一四选一选择器mux1的控制端分别输入第一位控制信号PHASE_SEL〈0〉和第二位控制信号PHASE_SEL〈1〉,第一四选一选择器mux1的输出端输出第一时钟信号ckn。图1中,PHASE_SEL〈1:0〉即为第一位控制信号PHASE_SEL〈0〉和第二位控制信号PHASE_SEL〈1〉。

二选一选择器mux3的输入端分别输入第二相时钟信号ck2和第四相时钟信号ck4,二选一选择器mux3的控制端输入第二位控制信号PHASE_SEL〈1〉,二选一选择器mux3的输出端输出第二时钟信号ckm。

第一采样电路D1用于第四相时钟信号ck4对第三时钟信号LCK进行采样得到第四时钟信号LOCK。

第二采样电路D2用于第二时钟信号ckm对第四时钟信号LOCK进行采样得到第五时钟信号rstn_pre。

第三采样电路D3用于第一时钟信号ckn对第五时钟信号rstn_pre进行采样得到第六时钟信号q0。

第四采样电路D4用于第一时钟信号ckn对第六时钟信号q0进行采样得到第七时钟信号q1。

第五采样电路D5用于第一时钟信号ckn对第七时钟信号q1进行采样得到第八时钟信号q2。

第六采样电路D6用于第一时钟信号ckn对第八时钟信号q2进行采样得到第九时钟信号q3。

第二四选一选择器mux2的输入端分别输入第六时钟信号q0、第七时钟信号q1、第八时钟信号q2和第九时钟信号q3,第二四选一选择器mux2的控制端分别输入第三位控制信号PHASE_SEL〈2〉和第四位控制信号PHASE_SEL〈3〉,第二四选一选择器mux2的输出端输出开关控制信号rstn。图1中,PHASE_SEL〈3:2〉即为第三位控制信号PHASE_SEL〈2〉和第四位控制信号PHASE_SEL〈3〉。

第一四分频电路在开关控制信号rstn的控制下对第一时钟信号ckn进行四分频得到第一分频信号CKSEL。

第二四分频电路在开关控制信号rstn的控制下对第一分频信号CKSEL进行四分频得到第二分频信号PCK。

图1中,电路控制信号PHASE_SEL〈3:0〉包括四位位控制信号,四位位控制信号分别为第一位控制信号PHASE_SEL〈0〉、第二位控制信号PHASE_SEL〈1〉、第三位控制信号PHASE_SEL〈2〉和第四位控制信号PHASE_SEL〈3〉。比如,当PHASE_SEL〈0〉=0、PHASE_SEL〈1〉=1、PHASE_SEL〈2〉=0、PHASE_SEL〈3〉=1时,PHASE_SEL〈3:0〉=1010;当PHASE_SEL〈0〉=1、PHASE_SEL〈1〉=1、PHASE_SEL〈2〉=0、PHASE_SEL〈3〉=1时,PHASE_SEL〈3:0〉=1011;其他的依此类推。

前述实施例中,第一采样电路D1、第二采样电路D2、第三采样电路D3、第四采样电路D4、第五采样电路D5、第六采样电路D6均为D触发器。

前述实施例中,第三时钟信号LCK由锁定检测电路产生。

本发明的工作原理如下:

参见图1,从压控振荡器产生频率为4GHz的四相时钟,分别为第一相时钟信号ck1、第二相时钟信号ck2、第三相时钟信号ck3和第四相时钟信号ck4,其中,第一相时钟信号ck1和第三相时钟信号ck3是一对差分时钟信号,第二相时钟信号ck2和第二相时钟信号ck4是另一对差分时钟信号。

一并参见图1、图2,将第一相时钟信号ck1、第二相时钟信号ck2、第三相时钟信号ck3和第四相时钟信号ck4分别输入第一四选一选择器mux1,由第二位控制信号PHASE_SEL〈1〉、第一位控制信号PHASE_SEL〈0〉即PHASE_SEL〈1:0〉来控制第一四选一选择器mux1输出,第一四选一选择器mux1的输出端输出第一时钟信号ckn。比如,当PHASE_SEL〈1〉=1、PHASE_SEL〈0〉=1即PHASE_SEL〈1:0〉=11时,第一四选一选择器mux1的输出端输出的第一相时钟信号ck1作为第一时钟信号ckn;当PHASE_SEL〈1:0〉=10时,第一四选一选择器mux1的输出端输出的第二相时钟信号ck2作为第一时钟信号ckn;当PHASE_SEL〈1:0〉=01时,第一四选一选择器mux1的输出端输出的第三相时钟信号ck3作为第一时钟信号ckn;当PHASE_SEL〈1:0〉=00时,第一四选一选择器mux1的输出端输出的第四相时钟信号ck4作为第一时钟信号ckn。

将第二相时钟信号ck2 和第四相时钟信号ck4 输入二选一选择器mux3,由第二位控制信号PHASE_SEL〈1〉来控制二选一选择器mux3输出,二选一选择器mux3的输出端输出第二时钟信号ckm。比如,当PHASE_SEL〈1〉=1时,二选一选择器mux3的输出端输出的第二相时钟信号ck2作为第二时钟信号ckm;当PHASE_SEL〈1〉=0时,二选一选择器mux3的输出端输出第四相时钟信号ck4作为第二时钟信号ckm。将第四相时钟信号ck4输入第一采样电路D1,对第三时钟信号LCK进行采样,得到第四时钟信号LOCK。将第二时钟信号ckm输入第二采样电路D2,对第四时钟信号LOCK信号进行采样,得到第四五时钟信号rstn_pre。这样第二时钟信号ckm和第五时钟信号rstn_pre就具有一定的时序关系。

然后,将第一时钟信号ckn输入第三采样电路D3,对第五时钟信号rstn_pre进行采样,得到第六时钟信号q0;将第一时钟信号ckn输入第四采样电路D4,用第一时钟信号ckn来采样第六时钟信号q0,得到第七时钟信号q1;将第一时钟信号ckn输入第五采样电路D5,用第一时钟信号ckn来采样第七时钟信号q1,得到第八时钟信号q2;将第一时钟信号ckn输入第六采样电路D6,用第一时钟信号ckn来采样第八时钟信号q2,得到第九时钟信号q3。这样产生的第六时钟信号q0、第七时钟信号q1、第八时钟信号q2和第九时钟信号q3,相邻的两个时钟信分别有一个Tckn的相位差,其中,Tckn表示第一时钟信号ckn的周期。将第六时钟信号q0、第七时钟信号q1、第八时钟信号q2和第九时钟信号q3输入第二四选一选择器mux2,由第四位PHASE_SEL〈3〉、第三位控制信号PHASE_SEL〈2〉即PHASE_SEL〈3:2〉来控制第二四选一选择器mux2输出,第二四选一选择器mux2的输出端输出开关控制信号rstn。比如,当PHASE_SEL〈3:2〉=11时,第二四选一选择器mux2的输出端输出第九时钟信号q3;当PHASE_SEL〈3:2〉=10时,第二四选一选择器mux2的输出端输出第八时钟信号q2;当PHASE_SEL〈3:2〉=01时,第二四选一选择器mux2的输出端输出第七时钟信号q1;当PHASE_SEL〈3:2〉=00时,第二四选一选择器mux2的输出端输出第六时钟信号q0。

将第一时钟信号ckn输入第一四分频电路,第一四分频电路在开关控制信号rstn的控制下对第一时钟信号ckn进行四分频得到第一分频信号CKSEL;将第一分频信号CKSEL输入第二四分频电路,第二四分频电路在开关控制信号rstn的控制下对第一分频信号CKSEL进行四分频得到第二分频信号PCK。第二分频信号PCK为本发明最终输出的时钟信号。这样,通过电路控制信号PHASE_SEL〈3:0〉的选择,就能得到在1位数据周期内相位有16个档位可选的第二分频信号PCK,第二分频信号PCK即为所需的双倍数据速率时钟(DDR Clock)。图2中,data是指串行数据,虚线箭头所指部分即一位数据周期。虚线箭头是将第二分频信号PCK的16个相位用虚线表示出来,通过电路控制信号PHASE_SEL〈3:0〉来选择不同相位的第二分频信号PCK输出。

可见,本发明仅使用6个D触发器、2个四选一选择器、1个二选一选择器和2个四分频电路,结构简洁明了,没有涉及复杂的逻辑变换,信号通路清晰易懂。使用的逻辑器件较少,时钟频率也不高,所以产生的功率消耗也较小,整个发明对应的版图占用的面积也较小,能够降低成本。

最后应说明的是:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。