存储器装置

文献发布时间:2023-06-19 09:57:26

技术领域

本发明是有关于一种存储器装置,且特别是有关于一种NAND存储器装置。

背景技术

随着集成电路中元件的关键尺寸逐渐缩小至工艺技术所能感知的极限,设计者已经开始寻找可达到更大存储器密度的技术,藉以达到较低的位成本(costs per bit)。目前正被关注的技术包括与非门存储器(NAND memory)及其操作。

发明内容

本发明是有关于一种存储器装置。

根据本发明的一方面,提出一种存储器装置包括通道元件、栅电极层、及存储元件。通道元件具有U形状。栅电极层电性耦接通道元件。存储元件包围通道元件的侧通道表面。

为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

图1绘示根据一实施例的存储器装置的横剖面图。

图2绘示根据一实施例的存储器装置的纵剖面图。

图3至图13绘示根据一实施例的存储器装置的制造方法。

【符号说明】

C:通道元件

CS1:第一侧通道表面

CS2:第二侧通道表面

CS3:第三侧通道表面

D1:第一方向

D2:第二方向

D3:第三方向

M:存储元件

M1A:第一存储层

M1S1:侧表面

M2、M2A、M2B、M2C:第二存储层

M3、M3A、M3B、M3C:第三存储层

MA:第一存储部分

MB:第二存储部分

MC:第三存储部分

G、GT、GM、GB:栅电极层

GS1:侧表面

GS2:上表面

GS3:下表面

112:介电条

114:导电层

116:电极元件

118:电极元件

250:第一堆叠区

260:第二堆叠区

330:介电层

330S1:侧表面

330S2:上表面

330S3:下表面

473、474:牺牲层

475:孔洞

477:凹口

480:沟道

485:缝隙

487:电极材料

489:导电柱

491:导电条

493:导电块

495:导电柱

497:导电条

具体实施方式

以下是以一些实施例做说明。须注意的是,本揭露并非显示出所有可能的实施例,未于本揭露提出的其他实施方式也可能可以应用。再者,附图上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和图示内容仅作叙述实施例之用,而非作为限缩本揭露保护范围之用。另外,实施例中的叙述,例如局部结构、工艺步骤和材料应用等等,仅为举例说明之用,并非对本揭露欲保护的范围做限缩。实施例的步骤和结构各自细节可在不脱离本揭露的精神和范围内根据实际应用工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件做说明。

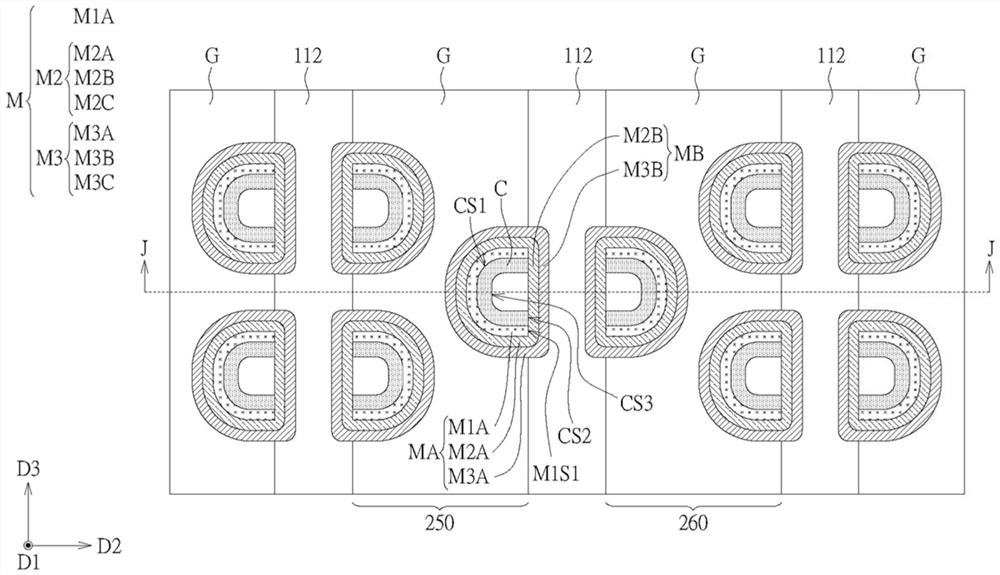

图1绘示根据一实施例的存储器装置的横剖面图。图2绘示根据一实施例的存储器装置的纵剖面图。一实施例中,图1可为沿图2的KK剖面线绘制出的剖面图,且图2可为沿图1的JJ剖面线绘制出的剖面图。

请参照图1,存储器装置包括通道元件C、栅电极层G及存储元件M。

实施例中,通道元件C具有U形状。通道元件C的侧通道表面可包括第一侧通道表面CS1、第二侧通道表面CS2及第三侧通道表面CS3。第二侧通道表面CS2在第一侧通道表面CS1与第三侧通道表面CS3之间。一实施例中,通道元件C可具有呈U形配置的马蹄形图案或开环图案。第一侧通道表面CS1(马蹄图案或开环图案的外侧表面)与第三侧通道表面CS3(马蹄图案或开环图案的内侧表面)具有U形状。第二侧通道表面CS2(马蹄图案或开环图案的末端侧表面)可具有平直形状。介电柱110可在第三侧通道表面CS3上。

存储元件M可包括数层存储层。一实施例中,存储元件M包括第一存储层M1A、第二存储层M2、及第三存储层M3。第二存储层M2在第一存储层M1A的侧表面上。第三存储层M3在第二存储层M2的侧表面上。

存储元件M包括第一存储部分MA与第二存储部分MB。第一存储部分MA在第一侧通道表面CS1上。第一存储部分MA具有U形状。第二存储部分MB在通道元件C的第二侧通道表面CS2上。第二存储部分MB可在第一存储层M1A与通道元件C的共侧平面上。第二存储部分MB具有平直形状。第一存储部分MA与第二存储部分MB形成环形状,包围通道元件C的侧通道表面与介电柱110的侧表面。

第一存储部分MA的存储层数目可不同于第二存储部分MB的存储层数目。于此实施例中,第一存储部分MA的存储层数目大于第二存储部分MB的存储层数目。第一存储部分MA可包括第一存储层M1A、第二存储层M2A与第三存储层M3A。换句话说,第一存储部分MA具有3层存储层。第二存储部分MB可包括第二存储层M2B与第三存储层M3B。换句话说,第二存储部分MB具有2层存储层。第二存储部分MB可不包括第一存储层。第一存储部分MA的第一存储层M1A、第二存储层M2A与第三存储层M3B具有U形状。第一存储层M1A的侧表面M1S1可共平面通道元件C的第二侧通道表面CS2。第二存储部分MB的第二存储层M2B与第三存储层M3B具有平直形状。

第一存储部分MA可包括任意的电荷捕捉结构,例如一氧化物-氮化物-氧化物(ONO)结构或一氧化物-氮化物-氧化物-氮化物-氧化物(BE-SONOS)结构等。举例来说,电荷捕捉层可使用氮化物例如氮化硅,或是其他类似的高介电常数物质包括金属氧化物,例如三氧化二铝(Al2O3)、氧化锆(HfO2)等。第一存储层M1A包括隧穿层。第二存储层M2(包括第二存储层M2A与第二存储层M2B)包括电荷捕捉层。第三存储层M3(包括第三存储层M3A与第三存储层M3B)包括势垒层。一实施例中,隧穿层包括氧化物例如氧化硅。电荷捕捉层包括氮化物例如氮化硅。势垒层包括氧化物例如氧化硅、三氧化二铝等。

第一存储部分MA与通道元件C在第二存储部分MB与栅电极层G之间。第二存储部分MB在介电柱110与介电条112之间。介电柱110可包括氧化物例如氧化硅,但不限于此。

请参照图1与图2,存储器装置可包括数个堆叠区,例如第一堆叠区250、第二堆叠区260等。介电条112在第一堆叠区250的栅电极层G与第二堆叠区260的栅电极层G之间。第一堆叠区250与第二堆叠区260各包括栅电极层G与介电层330。栅电极层G与介电层330在第一方向D1(例如垂直方向)上交错排列。栅电极层G电性耦接通道元件C。栅电极层G可包括位在最顶层的栅电极层GT、位在最底层的栅电极层GB、及在栅电极层GT与栅电极层GB之间的栅电极层GM。存储器装置的堆叠区,例如第一堆叠区250、第二堆叠区260等,可在一横方向(例如第二方向D2)上排列。

一实施例中,存储元件M更包括第三存储部分MC。第一存储部分MA连接在第二存储部分MB与第三存储部分MC之间。第三存储部分MC可从第一存储部分MA,连续延伸至介电层330的侧表面330S1、上表面330S2、与下表面330S3,与栅电极层G的上表面GS2与下表面GS3。

存储元件M在栅电极层G与介电层330之间。存储元件M在栅电极层G的侧表面GS1(侧电极表面)、上表面GS2(上电极表面)、与下表面GS3(下电极表面)上。存储元件M在介电层330的侧表面330S1(侧介电表面)、上表面330S2(上介电表面)、与下表面330S3(下介电表面)上。具有存储元件M于其上的侧表面GS1是相对于具有存储元件M于其上的侧表面330S1。

第一存储部分MA的存储层数目可不同于第三存储部分MC的存储层数目,或具有不同的存储层配置。第一存储部分MA的存储层数目可大于第三存储部分MC的存储层数目。第三存储部分MC的存储层数目可相同于第二存储部分MB的存储层数目,或具有相同的存储层配置。第三存储部分MC的存储层可包括第二存储层M2C与第三存储层M3C。第三存储部分MC可不包括第一存储层。

导电层114可在第一存储层M1A、通道元件C与介电柱110上。电极元件116与电极元件118分别电性连接通过介电条112与第二存储部分MB分开的导电层114。

存储器装置包括NAND存储器串行。NAND存储器串行可包括存储单元定义在通道元件C的栅电极层G之间的存储元件M中。NAND存储器串行可包括U形通道NAND存储器串行,或垂直通道NAND存储器串行。

一实施例中,电极元件116可为位线,且电极元件118可为共同源极线。NAND存储器串行可包括存储单元定义在通道元件C与第一堆叠区250及第二堆叠区260的栅电极层G之间的存储元件M中。NAND存储器串行具有U形的有效通道路径,U形通道与存储单元电性连接在作为位线的电极元件116与作为共同源极线的电极元件118之间。第一堆叠区250的栅电极层GT可用作串行选择线(SSL)。第二堆叠区260的栅电极层GT可用作接地选择线(GSL)。一实施例中,第一堆叠区250的栅电极层GB与第二堆叠区260的栅电极层GB可用作反转栅电极。一实施例中,第一堆叠区250的栅电极层GM与第二堆叠区260的栅电极层GM可用作字线。一实施例中,第一堆叠区250与/或第二堆叠区260中邻近栅电极层GT的部分栅电极层GM可用作虚置字线以避免可能的干扰。举例来说,第一堆叠区250中最顶一个的栅电极层GM与第二堆叠区260中最顶一个的栅电极层GM可用作虚置字线。基底100可为绝缘层,例如形成在半导体基底上的埋氧化物例如埋氧化硅,但不限于此。

另一实施例中,电极元件116可为位线。基底100可电性连接共同源极端,或用作共同源极元件。基底100可包括半导体基底例如含硅材料的基底,例如硅基底等。NAND存储器串行可包括存储单元定义在通道元件C与第一堆叠区250的栅电极层G之间的存储元件M中。NAND存储器串行具有在第一方向D1(例如垂直方向)上延伸的有效垂直通道路径,电性连接在电极元件116与基底100之间。第一堆叠区250的栅电极层GT可用作串行选择线(SSL)。第一堆叠区250的栅电极层GB可用作接地选择线(GSL)。一实施例中,第一堆叠区250的栅电极层GM可用作字线。一实施例中,第一堆叠区250的栅电极层GM的一部分可用作虚置字线。电极元件118也可作为位线,也可依上述类推第二堆叠区260侧的垂直通道NAND存储器串行。

图3至图13绘示根据一实施例的存储器装置的制造方法。

请参照图3,提供基底100。可形成堆叠结构在基底100上。堆叠结构可包括牺牲层与介电层330交错堆叠在基底100上。牺牲层可包括牺牲层474与其下方的牺牲层473。牺牲层473、牺牲层474、与介电层330可包括不同的材料。一实施例中,牺牲层473、牺牲层474包括氮化物,例如氮化硅,但不限于此。介电层330包括氧化物,例如氧化硅,但不限于此。牺牲层473、牺牲层474与介电层330可利用沉积方法例如物理气相沉积、化学气相沉积,或其它合适的方式形成。可利用光刻及刻蚀技术形成孔洞475在堆叠结构中。一实施例中,用以形成孔洞475的刻蚀步骤可停止在基底100上。一实施例中,孔洞475露出基底100的埋氧化层。

请参照图4,第一存储层M1A可形成在孔洞475露出的堆叠结构的侧表面及基底100的上表面上。第一存储层M1A也可形成在堆叠结构的上表面上。通道元件C可形成在孔洞475露出的第一存储层M1A上。通道元件C也可形成在堆叠结构的上表面上的第一存储层M1A上。通道元件C可包括多晶硅或其它合适的半导体材料。一实施例中,可形成介电柱110在通道元件C上,并填充孔洞475。一实施例中,介电柱110的形成方法可包括形成介电材料填充孔洞475并延伸在堆叠结构的上表面上的通道元件C上,并可利用化学机械研磨或其它合适的刻蚀方法移除在堆叠结构的上表面上的介电材料,剩余留在孔洞475中的介电材料形成介电柱110。介电材料可包括氧化物例如氧化硅,但不限于此。在堆叠结构的上表面上方的第一存储层M1A与通道元件C亦可通过化学机械研磨或其它合适的刻蚀方法移除。可利用合适的刻蚀方式对孔洞475中的第一存储层M1A、通道元件C与介电柱110进行回刻蚀以形成凹口477。凹口477的深度并未到达顶层的牺牲层473的上表面。

请参照图5,导电层114可形成填充凹口477。一实施例中,导电层114的形成方法可包括形成导电材料填充凹口477并在堆叠结构的上表面上,并利用化学机械研磨或其它合适的刻蚀方式将导电层114位在堆叠结构的上表面上的部分移除。导电材料可包括掺杂的多晶硅,例如重掺杂的N型多晶硅,或其它合适的导电材料例如金属等。一实施例中,可利用化学机械研磨或其它合适的刻蚀方式(例如回刻蚀)将堆叠结构的最顶层的介电层330上方的牺牲层474与导电层114移除,以平坦化堆叠结构的上表面。

图5A绘示图5的存储器装置沿KK剖面线绘制出的横剖面图。请参照图5A,一实施例中,孔洞475中的介电柱110可具有椭圆形状或操场形状。通道元件C具有环形状,并围绕介电柱110。第一存储层M1A具有环形状,并围绕通道元件C。图5B绘示图5的存储器装置沿QQ剖面线绘制出的横剖面图。请参照图5B,导电层114可具有椭圆形状或操场形状。图5为图5A与图5B所示的存储器装置沿JJ剖面线绘制出的纵剖面图。

请参照图6,可形成沟道480。沟道480可利用光刻及刻蚀技术图案化导电层114与堆叠结构、介电柱110、通道元件C、第一存储层M1A的上部分形成。沟道480可露出介电柱110的侧表面、通道元件C的第二侧通道表面CS2、第一存储层M1A的侧表面M1S1、牺牲层473的侧表面、介电层330的侧表面与导电层114的侧表面。沟道480的底部可露出介电柱110、通道元件C与第一存储层M1A与堆叠结构的牺牲层473。沟道480将堆叠结构定义出不同堆叠区(第一堆叠区250与第二堆叠区260等),使得不同堆叠区的的牺牲层473彼此分开。

图6A绘示图6的存储器装置沿KK剖面线绘制出的横剖面图。请参照图6A,沟道480延伸在第三方向D3上,图案化后的介电柱110具有半圆形状。图案化后的通道元件C可具有U形状、马蹄形状、或开环形状。图案化后的第一存储层M1A可具有U形状、马蹄形状、或开环形状。图6B绘示图6的存储器装置沿QQ剖面线绘制出的横剖面图。请参照图6B,图案化后的导电层114可具有半圆形状。图6为图6A与图6B所示的存储器装置沿JJ剖面线绘制出的纵剖面图。

请参照图7,可移除沟道480露出的牺牲层473(图6)以形成缝隙485。牺牲层473可利用具有刻蚀选择性的刻蚀工艺予以移除。缝隙485连通沟道480。缝隙485可露出第一存储层M1A的侧表面、介电层330的上表面330S2与下表面330S3、与基底100的上表面。

图7A绘示图7的存储器装置沿KK剖面线绘制出的横剖面图。请参照图7A,至此步骤,存储器装置可利用介电柱110、通道元件C与第一存储层M1A作为支撑体支撑其它元件,例如介电层330等。图7为图7A所示的存储器装置沿JJ剖面线绘制出的纵剖面图。

请参照图8,第二存储层M2可形成沟道480与缝隙485露出的介电柱110、通道元件C、第一存储层M1A、介电层330、与基底100上。

请参照图9,第三存储层M3可形成在沟道480与缝隙485露出的第二存储层M2上。

图9A绘示图9的存储器装置沿KK剖面线绘制出的横剖面图。请参照图9A,第二存储层M2可具有环形状,并围绕介电柱110、通道元件C与第一存储层M1A。第三存储层M3可具有环形状,并围绕第二存储层M2。图9为图9A所示的存储器装置沿JJ剖面线绘制出的纵剖面图。

请参照图10,电极材料487可形成在沟道480与缝隙485露出的第三存储层M3上。电极材料487可填满缝隙485。一实施例中,电极材料487可包括势垒金属例如氮化钛(TiN)等,与形成在势垒金属上的填充金属例如钨(W)等。但本揭露不限于此。电极材料487也可包括其它合适的配置/材料例如多晶硅或其它金属等导电材料。

请参照图11,可对电极材料487(图10)进行回刻蚀步骤,移除电极材料487在沟道480中的部分,并留下缝隙485中的部分以形成栅电极层G。不同层的栅电极层G可通过介电层330彼此隔开且电性隔离。

请参照图12,可形成介电条112填充沟道480。介电条112也可填充部分缝隙485。介电条112可包括氧化物例如氧化硅,但不限于此。

请参照图13,可形成导电柱489在导电层114上。可形成导电条491与导电块493在导电柱489上。可形成导电柱495在导电块493上。可形成导电条497在导电柱495上。一实施例中,导电条497可延伸在第二方向D2上。导电条491可延伸在第三方向D3上。一实施例中,导电条491可用作共同源极线。导电条497可用作位线。U形状通道元件C可电性连接在导电条491与导电条497之间。第一方向D1、第二方向D2与第三方向D3可彼此不同,例如实质上互相垂直。第一方向D1可为Z方向。第二方向D2可为X方向。第三方向D3可为Y方向。

综上所述,虽然本发明已以实施例揭露如上,然其并非用以限定本发明。本发明所属技术领域中普通技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当以随附权利要求所界定的为准。

- 存储器装置、存储器装置构造、构造、存储器装置形成方法、电流传导装置及存储器单元编程方法

- 存储器装置、主机装置、存储器系统、存储器装置控制方法、主机装置控制方法以及存储器系统控制方法