存储装置及其制造方法

文献发布时间:2023-06-19 11:52:33

技术领域

本发明有关于一种存储装置,且特别有关于一种动态随机存取存储装置及其制造方法。

背景技术

随着半导体技术的提升,为了符合消费者对于小型化电子装置的需求,动态随机存取存储器中存储单元的尺寸缩小,存储器单元的集成度(integration degree)也随之增加。而埋入式字线动态随机存取存储器(buried word line DRAM)的发展正是为了满足增加的动态随机存取存储器的集成度的需求,以加快元件的操作速度。再者,于埋入式字线动态随机存取存储器中更发展出隔离结构(例如沟槽隔离结构),以避免字线之间的干扰。

传统用来形成存储装置的各部件例如隔离结构、埋入式字线、位线以及电容器接触件(或称接触插塞)的多道工艺中,其所进行的步骤容易产生对位不准的问题。而随着存储装置的集成度不断增加,字线之间的间距和隔离结构之间的间距也不断缩小,对位不准的问题也更益严重。例如,在基底上方的电容器接触件(或称接触插塞)对位不准,可能会使电容器接触件与主动区之间的接触面积减少,使得电容器接触件与主动区之间的阻值增加,进而影响降低存储装置的电性表现。再者,由于对位不准而暴露出的半导体基底的表面可能因为刻蚀工艺而产生损伤,进而降低存储装置的可靠度。因此,如何避免上述情形的发生,实为一重要议题。

发明内容

本发明的一些实施例揭示一种存储装置,包括一半导体基底,其中半导体基底包含一沟槽隔离结构(shallow trench isolation structure)以及一主动区位于沟槽隔离结构的一侧。存储装置还包括两相邻的埋入式字线(buried word lines)以及第一介电层,其中埋入式字线设置于半导体基底内且相互分离,第一介电层位于半导体基底上并对应两相邻的埋入式字线的上方。存储装置还包括一接触插塞(contact plug),位于主动区的半导体基底上。接触插塞包含一导体层以及一外延层(epitaxial layer),其中导体层位于第一介电层的侧壁上,外延层位于导体层的侧壁上并延伸进入半导体基底。存储装置还包括一第二介电层,位于半导体基底上并覆盖接触插塞和沟槽隔离结构。

本发明的一些实施例揭示一种存储装置的制造方法,包括:提供一半导体结构,包含一半导体基底、一沟槽隔离结构位于半导体基底中、一介电层位于半导体基底上、以及一导体材料位于半导体基底上并覆盖介电层。存储装置的制造方法还包括对导体材料进行刻蚀,以暴露出沟槽隔离结构和移除半导体基底的一部分,而在半导体基底形成一凹槽,其中刻蚀后留下的导体材料为一导体层,且导体层位于介电层的侧壁上。存储装置的制造方法还包括进行外延成长,以于导体层的侧壁上形成一外延层,其中外延层填满凹槽。

附图说明

图1是根据本发明的一些实施例的存储装置的上视示意图。

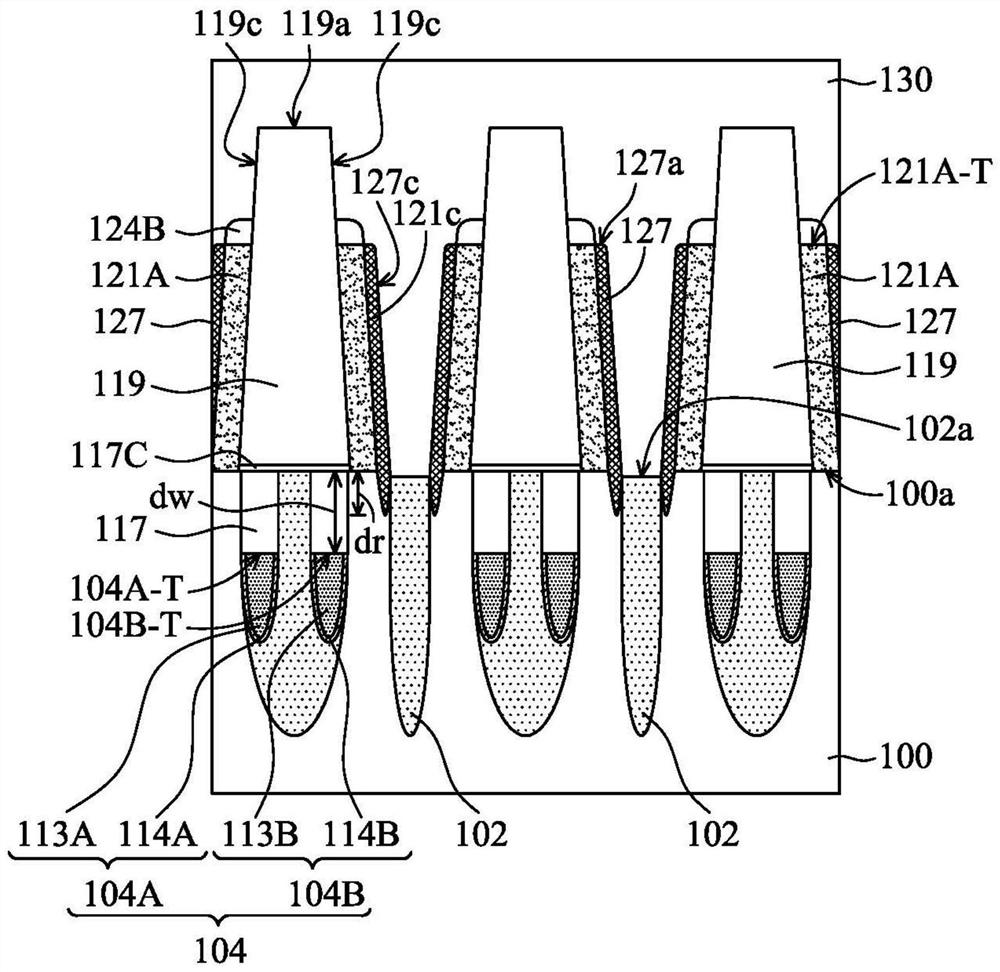

图2A至图2G为根据本发明的一些实施例的制造存储装置的各步骤中所对应的剖面示意图,其中,图2A至图2G对应图1中的剖面线2-2所绘制。

图3是根据本发明的一些其他实施例的具有外延层的存储装置的剖面示意图。

图4A至图4C是根据本发明的一些实施例的形成存储装置的工艺在形成外延层之后的一些中间阶段的剖面示意图。

符号说明

100~半导体基底;100R~凹槽;

100R

A

104~字线组;104A、104B~埋入式字线;

107~电容器接触件;109~位线接触件;

113A、113B~栅极;114A、114B~栅极介电层;

117、117C~氮化硅层;119~第一介电层;

120~开口;121~导体材料;

121A、121A’、135~导体层;124~掩膜层;

124B~掩膜材料;119c、121c、124c、127c~侧壁;

1243~谷部;1245~峰部;

127、127’~外延层;130、130’~第二介电层;

133~凹孔;D1~第一方向;

D2~第二方向;dw~第一深度;

dr~第二深度;W1、W2、W3、W4~宽度;

100a、102a、119a、121a、127a、104A-T、T1~厚度。

104B-T、121A-T~顶面;

具体实施方式

以下参照本发明实施例的图式以更全面地阐述本发明。然而,本发明亦可以各种不同的形式体现,而不应限于本文中所述的实施例。图式中的层与区域的厚度会为了清楚起见而放大。相同或相似的元件标号表示相同或相似的元件,以下段落将不再一一赘述。

本发明实施例提供一种存储装置及其制造方法,以形成包含导体层以及外延层的接触插塞,改善传统工艺中容易因偏移而导致主动区与接触插塞之间的接触面积减少以及对半导体基底造成损伤的问题,进而提升存储装置的电子特性以及操作表现。再者,一些实施例中,例如利用自对准刻蚀步骤形成导体层,并使用选择性外延成长的方式形成外延层,可以简化工艺步骤,减少光掩膜的使用数量,进而降低工艺成本。

另外,文中实施例所提出的存储装置例如是一种动态随机存取存储器(DynamicRandom Access Memory,DRAM),并以埋入式字线动态随机存取存储器为示例说明。而实施例所配合的图式是绘制一存储装置的一个主动区中包含两个埋入式字线。但本发明并不以此为限制。

如图1所示,一些实施例的一种存储装置包括:基底100、多个沟槽隔离结构(STI)102、多个主动区A

在此实施例中,基底100中形成有多个主动区(active areas)A

一些实施例的存储装置还包括多条位线BL位于基底100上,各条位线BL沿着第一方向D1延伸,且相邻的位线BL在第二方向D2上相距排列。多条字线组104位于基底100中,分别沿着第二方向D2延伸。一些实施例中,每一字线组104具有两个埋入式字线104A、104B,且相邻的埋入式字线104A、104B在第一方向D1上相距排列。

如图1所示,每一主动区A

再者,每一主动区A

另外,电容器接触件107和位线接触件109在图1中的形状并不限制为矩形,且其大小可依工艺或应用所需而调整与设计。

为简化图式以利清楚说明,图2A至图2G是绘制关于存储装置中对应于3个字线组104的制造方法与结构。

参照图1和图2A,提供一半导体基底100,且半导体基底100包含沿着第二方向D2延伸且多个沟槽隔离结构102以及分别以沟槽隔离结构隔开的多个主动区A

再者,所提供的半导体基底100内还包含多组字线组104,每一组字线组104包含两个相邻的埋入式字线104A、104B,且以隔离材料例如氧化物而相互分离。此实施例中,隔离材料与沟槽隔离结构102的材料相同,且隔离材料的底面低于各字线组104的底面,以减少字线组之间的干扰。每一条埋入式字线104A、104B包括栅极113A、113B以及围绕栅极113A、113B的栅极介电层114A、114B,其中栅极介电层114A、114B的设置使栅极113A、113B与半导体基底100达到电性隔绝。

栅极113A、113B的材料可例如铜、钨、氮化钨、氮化钛或其他合适的导电材料。栅极113A、113B可为由单层结构或多层结构所构成。例如栅极113A、113B可以包含钨和氮化钛。栅极113A、113B的形成方法可以是化学气相沉积法或物理气相沉积法。另外,栅极介电层114A、114B的材料可例如是氧化硅,其可利用化学气相沉积的方式形成。

再者,于一些实施例中,可以有绝缘层的形成。如图2A所示,分别于埋入式字线104A、104B上方形成一氮化硅层117。于一些实施例的各字线组104中,氮化硅层117C,形成于埋入式字线104A、104B上的两氮化硅层117的上方。氮化硅层117以及117C可利用化学气相沉积法而形成。

再者,于一些实施例中,所提供的半导体基底100的各字线组104上方还形成有第一介电层119。如图2A所示,第一介电层119位于半导体基底100上,且对应各字线组104中两个相邻的埋入式字线104A、104B的上方。对应各字线组104的第一介电层119之间则具有开口120。一些实施例中,第一介电层119包含介电材料,例如是旋涂式介电材料(spin-ondielectric,SOD)。可以利用全面旋涂适当的介电材料于半导体基底100上,并以干式刻蚀方式对介电材料进行图案化,以形成如图2A所示的第一介电层119。在一些实施例中,第一介电层119的材料例如是四乙氧基硅烷(tetraethoxysilane,TEOS),但本发明不以此材料为限,第一介电层119的材料可以是一种或是多种介电材料的组合。

接着,参照图2B,形成一导体材料121于半导体基底100上,且导体材料121覆盖第一介电层119并填满开口120。在一些实施例中,导体材料121覆盖所有第一介电层119的顶面119a与侧壁119c,并且覆盖暴露于第一介电层119之间的半导体基底100的表面。亦即,如图2B所示,导体材料121的顶面121a高于第一介电层119的顶面119a。在一些实施例中,导体材料121例如是掺杂或未掺杂的多晶硅,其可利用化学气相沉积法而形成于半导体基底100上。而此导体材料121在经过后续工艺的图案化,将成为接触插塞的一部份。

之后,参照图2C,移除部分的导体材料121,以暴露出第一介电层119的顶面119a以及部分侧壁119c。移除步骤完成后,第一介电层119的顶面119a低于第一介电层119的顶面119a。在一些实施例中,可进行回刻蚀工艺,以移除部分的导体材料121。

接着,参照图2D,沉积一掩膜层124于导体材料121上,包括顺应性地沉积掩膜层124于第一介电层119的顶面119a和部分的侧壁119c上。此掩膜层124包含多个谷部1243以及多个峰部1245,其中谷部1243大致对应于沟槽隔离结构120,峰部1245大致对应于第一介电层119。在一实施例中,掩膜层124的材料例如是氮化硅,且可利用原子层沉积法(Atomiclayer deposition,ALD)而于导体材料121上形成掩膜层124。

在一些实施例中,若两相邻第一介电层119之间在第一方向D1上具有宽度W1,则掩膜层124的厚度T1可大于宽度W1的1/4,且小于宽度W1的1/2,例如约W1的1/3。而掩膜层124的厚度T1决定了谷部1243的宽度。在一些实施例中,例如掩膜层124的谷部1243在第一方向D1上具有宽度W2,两相邻第一介电层119之间所对应的沟槽隔离结构102在第一方向D1上具有宽度W3,宽度W2可略大于宽度W3。藉由选择与调整掩膜层124的厚度T1,可决定后续自对准刻蚀后所形成的导体层(如图2E所示的导体层121A)在第一方向D1上的宽度以及在半导体基底100形成凹槽(如图2E所示的凹槽100R)大小。

之后,参照图2E,在一些实施例中,根据掩膜层124(图2D)对导体材料121进行刻蚀,例如沿着掩膜层124的侧壁124c向下刻蚀,并且以过刻蚀方式(over-etching)移除部分的导体材料121和移除半导体基底100的一部分,以在半导体基底100形成凹槽(recess)100R,其中留下的导体材料为导体层121A,而凹槽100R的底部100R

在一些实施例中,使用干式刻蚀方式,例如反应离子刻蚀(reactive-ionetching,RIE),进行过刻蚀。由于只需要掩膜层124而不需要额外采用光掩膜,即可对导体材料121进行刻蚀,因此此过刻蚀步骤又称为自对准刻蚀(self-aligned etching),可自对准的形成凹槽100R。

再者,参照图1和图2E,一些实施例中,在同一道过刻蚀步骤中,可以同时移除位于各沟槽隔离结构102的上方的导体材料121,以在沟槽隔离结构102两侧的不同主动区A

另外,上述过刻蚀步骤可例如是一次步骤、两次步骤或多次步骤。例如,在第一刻蚀步骤中,先沿着掩膜层124的侧壁124c向下刻蚀,以移除导体材料121,并暴露出半导体基底100的顶面100a。接着,进行第二刻蚀步骤,例如调整刻蚀工艺的工艺参数,以在半导体基底100形成凹槽100R。

值得注意的是,进行过刻蚀步骤所形成的凹槽100R的底部100R

然而,并不特别限制上述第一深度dw和第二深度dr的数值比例,只要过刻蚀步骤进行后能完全移除相邻主动区中的两个第一介电层119之间的导体材料121,而暴露出沟槽隔离结构102的顶面102a,并且在沟槽隔离结构102的顶面102a两侧的半导体基底100中形成凹槽100R,以确保完全隔绝位于沟槽隔离结构102两侧的半导体基底100,皆属本发明的实施例。

接着,参照图2F,进行选择性外延成长(selective epitaxial growth,SEG),以形成外延层127,其中外延层127位于导体层121A的侧壁121c上并延伸进入半导体基底100,填满凹槽100R。

一些实施例中,导体层121A例如是包含多晶硅,而半导体基底100例如是含有硅,因此进行选择性外延成长时,可在含硅的材料层上形成外延层。在一些实施例中,导体层121A的顶面被掩膜材料124B覆盖,如图2E、2F所示,只有导体层121A的侧壁121c暴露出来。因此进行选择性外延成长时,会在导体层121A的侧壁121c和半导体基底100的凹槽100R处长出外延硅。如图2F所示,外延层127形成于导体层121A的侧壁121c上(例如,覆盖导体层121A暴露出的所有的侧壁121c),并且填满凹槽100R。

再者,一些实施例中,外延层127在凹槽100R内的深度亦为前述的第二深度dr。而半导体基底100的顶面100a至埋入式字线104A/104B的顶面104A-T/104B-T之间的距离(亦即,第一深度dw)与外延层127的第二深度dr之间的比例和关系,请参照前述内容,在此不再赘述。

值得注意的是,一些实施例中,所形成的外延层127与导体层121A构成存储装置的一接触插塞。此接触插塞例如是图1中所示的电容器接触件107。因此,本发明的实施例可以改善因工艺偏移而导致主动区与接触插塞(电容器接触件)之间的接触面积减少的问题,使电流可以通过导体层121A和外延层127,以维持电流流经通道的宽度,进而降低阻值。因此,根据本发明的实施例,可以解决存储装置的操作速度受到接触面积减少的影响而降低的问题。

另外,在其他一些实施例中,可调整和选择选择性外延成长的工艺参数,使成长的外延层127至少填满凹槽100R,还超出凹槽100R的位置延伸至沟槽隔离结构102的顶面102a。图3是根据本发明的一些其他实施例的具有外延层的存储装置的剖面示意图。在此示例中,在进行选择性外延成长后,成长的外延层127填满凹槽100R,并覆盖一部份的沟槽隔离结构102的顶面102a。但不同主动区的外延层127相隔至少一距离,而不相互连接。如图3所示,相邻外延层127之间的距离具有宽度W4。在一些示例中,宽度W4是沟槽隔离结构102的顶面102a的宽度W3的约80%-100%,例如约90%,使相邻接触插塞的信号不相互干扰。

然后,参照图2G,形成一第二介电层130于半导体基底100上,并覆盖第一介电层119以及填满外延层127之间的空间。一些实施例中,此第二介电层130位于导体层121A的上方,并覆盖外延层127的顶面127a与侧壁127c。亦即,第二介电层130直接接触外延层127。一些实施例中,第二介电层130的介电材料可与掩膜层124包含相同的介电质,例如氮化硅。

形成第二介电层130之后,可进行后续工艺,以完成接触插塞的制作。以下提出其中一种后续制法做示例说明。

图4A至图4C是根据本发明的一些实施例的形成存储装置的工艺在形成外延层之后的一些中间阶段的剖面示意图。图4A中的各部件与图2G相同,其各部件及其制作请参照前述实施例的内容,在此不重复赘述。

接着,参照图4B,在一些实施例中,进行平坦化工艺,移除部分的第二介电层130、部分的第一介电层119以及部分的第二介电层130,直至暴露出导体层121A的顶面121A-T以及外延层127的顶面127a。平坦化后,第二介电层130’的顶面、导体层121A的顶面121A-T以及外延层127的顶面127a共平面。在一些实施例中,平坦化工艺可例如是化学机械研磨(chemical mechanical polishing,CMP)工艺。

之后,参照图4C,在一些实施例中,回刻蚀步骤后,使所述导体层121A以及外延层127凹陷化,例如形成凹孔(recessed hole)133。接着,在凹孔133处形成另一导体层135于导体层121A’和外延层127’的上方。如图4C所示,在一些实施例中,导体层135横跨导体层121A’和外延层127’,并与导体层121A’和外延层127’直接接触。

在一些实施例中,导体层135的材料例如是包含铜、钨、氮化钨、氮化钛、或其他合适的含金属的导电材料。一示例中,导体层135包含金属块体(例如钨)和包围金属块体的底面和侧壁的阻障层(例如氮化钛)。一些实施例中,导体层135的形成方法可以是化学气相沉积法。

根据一些实施例,上述的导体层121A’、外延层127’和上方的导体层135构成存储装置的接触插塞,其中导体层121A’和外延层127’共同作为接触插塞的底接触部(bottomcontact portion),导体层135则作为接触插塞的顶接触部(top contact portion)。此接触插塞亦为图1所示的电容器接触件107。在一些实施例中,由于导体层121A’和外延层127’分别为多晶硅和外延硅,导体层135包括含金属的导电材料,其中导体层135的阻值低于导体层121A’的阻值,也低于外延层127’的阻值。因此,导体层135的设置可减少导体层121A’和外延层127’的含量,而降低接触插塞的整体电阻。

之后,可分别形成多个电容元件(未绘示于图4C)于接触插塞(或电容器接触件107)的上方。

根据上述实施例,电容元件下方的接触插塞可以包含导体层135(作为顶接触部)、导体层121A’和外延层127’(作为底接触部),其中导体层135例如是含有钨金属,导体层121A’例如是多晶硅,外延层127’例如是外延硅。因此,在一些实施例中,若以电子显微镜观察存储装置的剖面,特别是接触的电极底接触部的剖面,可以观察到两种不同晶型的导体层121A’和外延层127’及其界面。例如,导体层121A’是由多种不同排列方向的单晶所组成,外延层127’是在某一个平面之上规则排列成长的单结晶膜层。因此,导体层121A’和外延层127’之间具有清楚的界面。

综合上述,根据本发明的一些实施例,可利用过刻蚀方式对导体材料121进行图案化,除了确保位于不同主动区A

虽然本发明已以数个较佳实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中具有通常知识者在不脱离本发明的精神和范围内,当可作任意的更动与润饰,因此本发明的保护范围当视前述权利要求书范围所界定者为准。

- 非易失性存储元件、非易失性存储装置、非易失性存储元件的制造方法及非易失性存储装置的制造方法

- 制造半导体存储装置的方法及用该方法制造的半导体存储装置