薄膜沉积装置及晶舟组件

文献发布时间:2023-06-19 10:08:35

技术领域

本发明涉及半导体制造技术领域,具体地涉及薄膜沉积装置及晶舟组件。

背景技术

存储器件的存储密度的提高与半导体制造工艺的进步密切相关。随着半导体制造工艺的特征尺寸越来越小,存储器件的存储密度越来越高。为了进一步提高存储密度,已经开发出三维结构的存储器件(即,3D存储器件)。3D存储器件包括沿着垂直方向堆叠的多个存储单元,在单位面积的晶片上可以成倍地提高集成度,并且可以降低成本。随着市场对单颗存储器芯片的存储容量的需求越来越高,在堆叠封装结构中堆叠的裸片多达16层,甚至更多。

在3D存储器件的制造工艺中,采用薄膜沉积装置在晶片上形成多层薄膜。薄膜沉积装置包括反应室内的晶舟(wafer boat),在晶舟上沿垂直方向叠置多个晶片,在反应室内通入反应气体,从而可以在多个晶片上同时沉积多层薄膜。该多层薄膜例如是3D存储器件的功能叠层,例如包括氧化物、氮化物和氧化物的ONO叠层结构。由于3D存储器件的功能叠层用于以电荷的形式存储数据,因此功能叠层中的多层薄膜质量对电学性能起着至关重要的作用。

然而,在薄膜沉积装置中,即使多个层面的反应气体流量大致相同,在不同层面的多个晶片之间也会互相竞争反应气体,因而反应速度也存在着差异。在晶舟的垂直方向上不同层面的晶片上的膜厚存在着差异,导致3D存储器件的电学性能波动和产品良率降低。

发明内容

鉴于上述问题,本发明的目的在于提供薄膜沉积装置及晶舟组件,其中,采用进气端附近的隔离结构以消除晶片加载效应的影响。

根据本发明的一方面,提供一种晶舟组件,包括:堆叠的多个横隔板;以及将所述多个横隔板连接在一起的侧壁,所述侧壁与每个所述横隔板的一部分周边区域相连接,使得相邻的所述横隔板与所述侧壁共同形成半包围空间,其中,相邻横隔板之间的所述半包围空间用于容纳至少一个晶片,所述侧壁上形成有多个进气端,分别向所述半包围空间供给气体。

优选地,所述横隔板的表面用于与晶片的背面接触以实现支撑固定。

优选地,还包括:顶板、底板以及在二者之间连接的多根支撑杆,其中,所述多个支撑杆沿着所述顶板的圆周方向分布,并且所述多根支撑杆的侧壁上形成多个凹槽,采用所述多根支撑杆的所述多个凹槽支撑固定多个层面的晶片。

优选地,所述横隔板的表面与所述顶板的表面和所述底板的表面平行。

优选地,所述横隔板的形状为选自圆形、方形和圆环形的任意一种。

优选地,所述横隔板和所述侧壁分别由陶瓷材料制成。

优选地,所述半包围空间的开口部沿着所述横隔板周向的开口角度大于180°。

根据本发明的另一方面,提供一种薄膜沉积装置,包括:外壳和基座,所述外壳和所述基座连接以形成反应室;上述的晶舟组件,位于所述反应室中;以及进气管和多根歧管,彼此连通以形成进气管路,并且所述多根歧管分别连接至所述侧壁上的多个开口以形成所述进气端。

优选地,还包括:竖隔板,所述竖隔板经由开孔与所述反应室的内部空间连通,与所述外壳的内壁之间形成排气通道以排放气体。

优选地,所述薄膜沉积装置采用原子层沉积工艺在垂直方向上叠置的多个晶片上形成薄膜。

根据本发明实施例的晶舟组件中,相邻横隔板与侧壁共同形成半包围空间,将相邻层面的至少一些晶片之间彼此隔开,并且在进气端附近位置的隔离状态最佳,因而可以有效减轻或消除晶片加载效应的影响,使得不同层面的晶片的膜厚大致相同。

根据优选实施例的晶舟组件,横隔板的表面与晶片的背面接触以实现支撑固定。横隔板兼用于支撑固定每个层面的晶片和隔开相邻层面的晶片。该结构不仅可以省去附加的支撑杆从而简化结构,而且每个层面的晶片均单独供给气体,可以进一步有效减轻或消除晶片加载效应的影响,使得不同层面的晶片的膜厚大致相同。

附图说明

通过以下参照附图对本发明实施例的描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:

图1示出一种薄膜沉积装置的结构示意图。

图2示出根据现有技术的薄膜沉积装置中的晶舟组件的立体结构图。

图3示出根据现有技术的薄膜沉积装置中晶片位置与膜厚关系的曲线图。

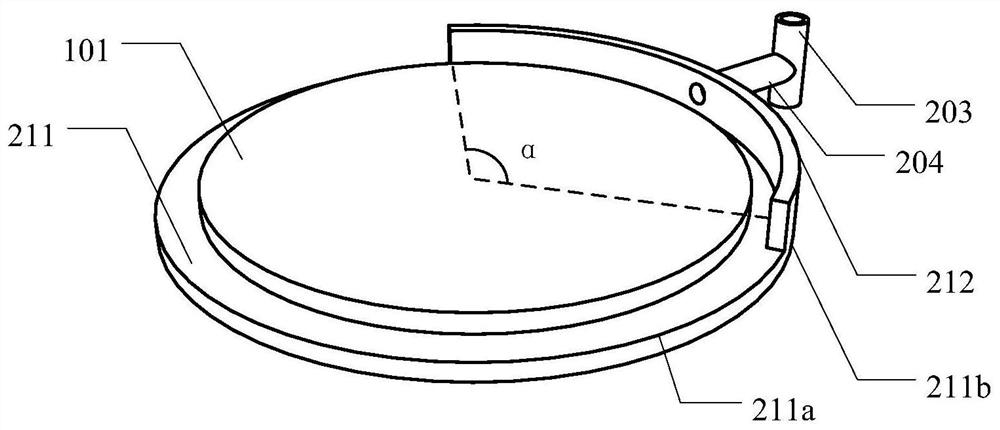

图4示出根据本发明第一实施例的薄膜沉积装置中的晶舟组件的立体结构图。

图5示出图4所示晶舟组件的单层结构的局部结构图。

图6示出图4所示晶舟组件的反应气体分布仿真图。

图7示出根据本发明第二实施例的薄膜沉积装置中的晶舟组件的立体结构图。

具体实施方式

以下将参照附图更详细地描述本发明。在各个附图中,相同的元件采用类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按比例绘制。此外,可能未示出某些公知的部分。为了简明起见,可以在一幅图中描述经过数个步骤后获得的半导体结构。

应当理解,在描述器件的结构时,当将一层、一个区域称为位于另一层、另一个区域“上面”或“上方”时,可以指直接位于另一层、另一个区域上面,或者在其与另一层、另一个区域之间还包含其它的层或区域。并且,如果将器件翻转,该一层、一个区域将位于另一层、另一区域“下面”或“下方”。

如果为了描述直接位于另一层、另一区域上面的情形,本文将采用“直接在……上面”或“在……上面并与之邻接”的表述方式。

下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。

图1示出一种薄膜沉积装置的结构示意图。

如图所示,薄膜沉积装置100包括外壳102和基座103。外壳102和基座103彼此连接以形成反应室。进气管104沿着垂直方向延伸,包括沿着垂直方向分布的多个喷嘴105,从而可以提供反应气体。竖隔板106经由开孔与反应室的内部空间连通,与外壳102的内壁之间形成排气通道,从而可以排放反应气体。

在反应室的内部空间中设置有晶舟组件110。该晶舟组件110例如包括顶板111和底板112,以及在二者之间连接的支撑杆113。多个晶片101沿着垂直方向叠置在晶舟组件110上。在薄膜沉积工艺中,进气管104的多个喷嘴105分别向相应层面的晶片101供给反应气体。

优选地,晶舟组件110与电机相连接,从而可以旋转,以改善反应气体接触晶片表面的均匀性。

图2示出根据现有技术的薄膜沉积装置中的晶舟组件的立体结构图。该晶舟组件例如用于图1所示的薄膜沉积装置中用于叠置晶片。

晶舟组件110包括顶板111和底板112,以及在二者之间连接的多根支撑杆113。晶舟组件110的顶板111、底板112、以及支撑杆113可以分别由在高温过程中耐热形变并且具有高耐腐蚀性的材料制成,例如,由陶瓷材料制成。顶板111和底板112例如分别为圆环状。晶舟组件110的多个支撑杆113沿着顶板111的圆周方向分布,例如可以形成大于180°的开口部。在支撑杆113的侧壁上形成多个凹槽121。晶片101经由开口部放入,边缘接触多根支撑杆113的凹槽121的内壁以实现支撑固定。在晶舟组件110上沿垂直方向叠置多个晶片101。进气管104沿着垂直方向延伸,包括沿着垂直方向分布的多个喷嘴105,从而可以向相应层面的晶片提供反应气体,在多个晶片101的表面上形成薄膜。

在3D存储器件的制造过程中,例如采用上述的原子层沉积工艺,在晶片101上沉积多层薄膜,以形成3D存储器件的功能叠层。该功能叠层例如是氧化物、氮化物和氧化物的ONO叠层结构。

本发明人发现,在上述现有技术的晶舟组件中,进气管104沿着垂直方向延伸并且采用沿着垂直方向分布的多个喷嘴105供给气体,即使多个层面的晶片101上供给的气体流量大致相同,在不同层面的多个晶片101之间也会互相竞争反应气体,因而反应速度也存在着差异。在晶舟的垂直方向上不同层面的晶片上的膜厚存在着差异。

参见图3,晶片位置例如是晶片在晶舟组件中的堆叠层面,膜厚例如是晶片上形成的薄膜厚度。堆叠层面例如从底板112到顶板111依次增加。可以看到,不同层面的晶片膜厚存在着明显的差异,位于中间位置的晶片膜厚远小于位于顶部位置和底部位置的晶片膜厚。由于不同层面的晶片上的膜厚存在着差异,因此,3D存储器件的电学性能波动和产品良率降低。

为减少反应室内多个晶片上薄膜的厚度的差异,本发明实施例提供一种薄膜沉积装置和晶舟组件。图4和5分别示出根据本发明第一实施例的薄膜沉积装置中的晶舟组件的立体结构图和局部结构图。该晶舟组件例如用于图1所示的薄膜沉积装置中,用于叠置晶片。

晶舟组件210包括堆叠的多个横隔板211、以及将多个横隔板211连接在一起的侧壁212。横隔板211和侧壁212可以分别由在高温过程中耐热形变并且具有高耐腐蚀性的材料制成,例如,由陶瓷材料制成。横隔板211的形状例如为圆形、矩形、环形中的任意一种。侧壁212连接横隔板211的一部分周边区域211b,使得相邻层面的横隔板211与侧壁212共同形成半包围空间,该半包围空间具有开口角度α大于180°的开口部211a。晶片101经由开口部211a放入,晶片101的背面接触横隔板211的表面以实现支撑固定。该晶舟组件210的每个横隔板211上均可承载相应的一个晶片101,从而沿垂直方向叠置多个晶片101。进气管203沿着垂直方向延伸,与横向延伸的多根歧管204连通,以形成进气管路。歧管204连接至侧壁212,经由侧壁212上的开口向相应层面的晶片供给反应气体,以在多个晶片101的表面上形成薄膜。

在原子层沉积工艺中,按照多个前驱体脉冲将不同类型的气体(源气体和反应气体)交替地通入反应器,在晶片上化学吸附并反应而形成薄膜。在反应气体到达晶片表面时,在晶片表面化学吸附并发生表面反应。在前驱体脉冲之间用惰性气体对反应室进行清洗。例如,使用含有硅的硅前驱体物质作为源气体,使用等离子活化的氮气作为反应气体,使用氮气作为清洗气体,按照源气体、净化气体、反应气体和净化气体的顺序来有序地提供气体,从而形成氮化硅膜(Si3N4)。

根据该实施例的晶舟组件,其中,相邻层面的横隔板211与侧壁212共同形成半包围空间,不仅用于容纳相应层面的晶片,而且用于将相邻层面的晶片之间彼此隔开。由于晶片加载效应(loading effect),相邻层面的晶片101在进气端附近位置是彼此影响最严重的区域。在该实施例中,侧壁212上的开口作为进气管的进气端,相邻层面的进气端通过上述半包围空间隔开,因此相邻层面的晶片101在进气端附近位置的隔离状态最佳,因而可以有效减少晶片加载效应的影响。这样,可减少沉积薄膜时反应室内多个晶片上薄膜的厚度的差异,改善不同层面的晶片的膜厚一致性。

参见图6,晶片101的表面附近,进气端的气体流速(例如为1.88m/s)远高于远端的气体流速(例如,接近0m/s)。该流速表示气体单位时间内的位移,单位为m/s。本发明实施例提供的晶舟组件210中,晶舟组件的横隔板211和侧壁212共同形成的半包围空间在进气端获得最佳隔离状态,该半包围空间也可在远端也改善了气流分布状况。在进气管203经由歧管204向相应层面的晶片101供给气体的情形下,多个层面的晶片101上供给的气体流量大致相同。这样,在每一个层面中可减少进气端和远端之间的气体流速差异,在晶舟组件的各个层面的晶片上相对于进气端的不同位置的膜厚均匀性改善。横隔板211与侧壁212共同形成的半包围空间也可以抑制不同层面的多个晶片101的彼此影响,使得多个层面的晶片上的反应速度大致相同,在晶舟组件的垂直方向上不同层面的晶片上的膜厚也大致相同。本申请实施例中,平行可包含,近似平行,即不同晶片之间的夹角小于设定阈值。

在3D存储器件的制造过程中,例如采用上述的原子层沉积工艺,在晶片101上沉积多层薄膜,以形成3D存储器件的功能叠层。该功能叠层例如是氧化物、氮化物和氧化物的ONO叠层结构。由于不论晶片位置如何,晶舟组件中不同层面的晶片膜厚均大致相同,因此,3D存储器件的电学性能一致性好,产品良率得以提高。

在该实施例中,以原子层沉积工艺为例说明,即,上述的晶舟组件位于原子层沉积设备的反应室中。然而,本发明不限于此,例如,上述的晶舟组件还可以应用于化学气相沉积设备。

图7示出根据本发明第二实施例的薄膜沉积装置中的晶舟组件的立体结构图。该晶舟组件例如用于图1所示的薄膜沉积装置中用于叠置晶片。

晶舟组件310包括顶板311和底板312、在二者之间连接的多根支撑杆313、堆叠的多个横隔板314、以及将多个横隔板314连接在一起的侧壁315。晶舟组件310的顶板311、底板312、支撑杆313、横隔板314和侧壁315可以分别由在高温过程中耐热形变并且具有高耐腐蚀性的材料制成,例如,由陶瓷材料制成。顶板311和底板312例如分别为圆环状。晶舟组件310的多个支撑杆313沿着顶板311的圆周方向分布,例如可以形成开口角度大于180°的开口部。在支撑杆313的侧壁上形成多个凹槽321。晶片101经由开口部放入,边缘接触多根支撑杆313的凹槽321的内壁以实现支撑固定。

进一步地,横隔板314的表面与顶板311和底板312的表面大致平行横隔板314的形状例如为圆形、矩形、环形中的任意一种。侧壁315连接横隔板314的一部分周边区域,使得相邻层面的横隔板314与侧壁315共同形成半包围空间。优选地,侧壁315与支撑杆313的侧壁相连接。该晶舟组件310利用支撑杆313上的凹槽321支撑固定晶片101,从而沿垂直方向叠置多个晶片101。相邻横隔板314之间的半包围排空间可以容纳多个晶片101。进气管303沿着垂直方向延伸,与横向延伸的多根歧管304连通,以形成进气管路。歧管304连接至侧壁315,经由侧壁315上的开口向多个层面的晶片供给反应气体,在多个晶片101的表面上形成薄膜。

根据该实施例的晶舟组件,其中,采用支撑杆313上的凹槽321支撑固定晶片101,相邻层面的横隔板311与侧壁312共同形成半包围空间,用于将至少一些晶片之间彼此隔开。在该实施例中,侧壁312上的开口作为进气管的进气端,因此相邻层面的晶片101在进气端附近位置的隔离状态最佳,因而可以有效减轻晶片加载效应的影响。

依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要求书及其全部范围和等效物的限制。

- 薄膜沉积装置及晶舟组件

- 一种晶舟和具有该晶舟的炉管装置