一种实现CZT变换的FPGA架构

文献发布时间:2023-06-19 10:24:22

技术领域

本发明属于信号处理技术领域,具体涉及一种FPGA架构设计技术。

背景技术

在信号处理领域,常用DFT变换或FFT变换,分析离散采样信号的频谱,针对的是信号的整个频域。在需要对信号的局部频域细化分析的场合,一般使用CZT变换。

设有限长序列x(n),0≤n≤N-1,其Z变换定义为

z为任意复数。

如果在Z域中,沿单位圆取等间隔抽样点依次对x(n)进行Z变换,即令

如果在Z平面上,取任意一段螺线做等分角抽样,即令z为 z

A、W表示为

为了对信号进行频谱分析,CZT变换在单位圆上取一段圆弧,即A

CZT变换的工程实现并不像DFT那样,通过FFT变换快速计算,而直接计算CZT变换的计算量较大,因此需要研究实现CZT变换的快速计算工程架构。

工程中常用布鲁斯坦等式

令

选取最小的正整数L是2的整数次幂且L≥N+M-1,对g(n)和h(n)序列作长度为L的扩展,g(n)补零加长为L点的序列为

h(n)作周期延拓为L点的序列为

用FFT和IFFT快速计算

令

c(n)产生模块的产生系数c(n)表达式为

系数c(n)和需要做CZT变换的序列x(n)一起输入复数相乘模块相乘,得到

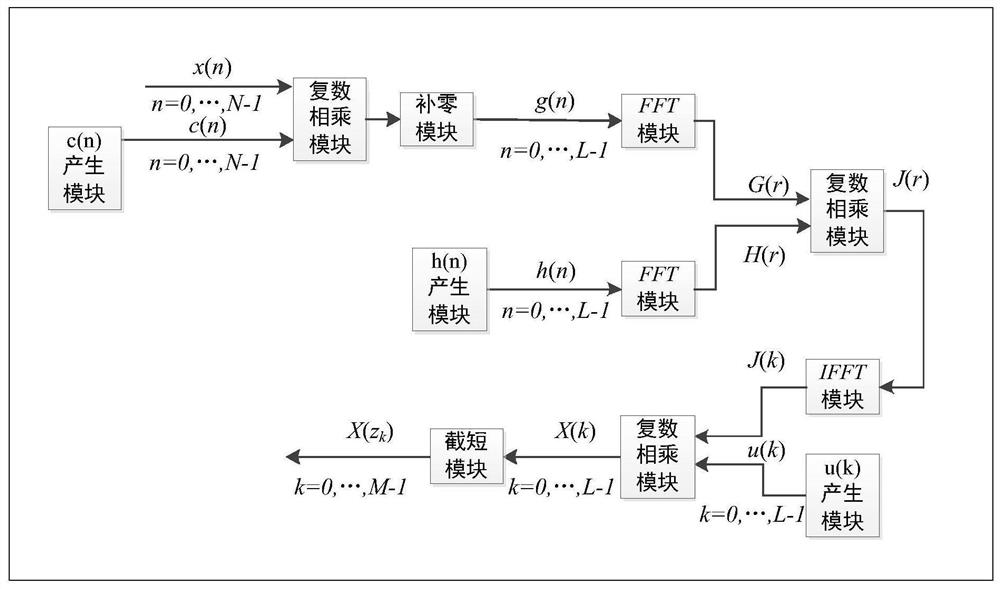

系数h(n)输入FFT模块进行FFT变换,得到H(r)=FFT(h(n))和G(r)一起输入复数相乘模块相乘,得到J(r)=G(r)·H(r)=FFT(g(n))·FFT(h(n))输入IFFT模块进行IFFT变换,得到J(k)=IFFT(J(r))=IFFT(FFT(g(n))·FFT(h(n)))和u(k)一起输入复数相乘模块相乘,得到X(k)表达式为

X(k)输入截短模块,截除M≤k≤L-1部分,得到序列x(n)的CZT变换结果X(z

FFT模块和IFFT模块一般采用FPGA厂商提供的IP核,补零和截短处理容易实现,因此关键在于c(n)、h(n)、u(k)三个系数的产生模块,这是三个线性调频信号,在以往的工程实现中,如果采用线性频率产生器与FPGA厂商提供的DDS产生器相结合的方式,耗费较多的存储资源,如果直接计算相角,再输入FPGA厂商提供的CORDIC运算器产生线性调频信号,计算复杂,耗费较多的计算资源。

发明内容

本发明为了解决现有技术存在的问题,提出了一种实现CZT变换的FPGA架构,为了实现上述目的,本发明采用了以下技术方案。

采用布鲁斯坦等式,将CZT变换转变为三个系数c(n)、h(n)、u(k)的计算,分别设置c(n)、h(n)、u(k)的相角,采用两个加法器形成递推结构,由于相角的初值仅与常数θ

设定c(n)的相角为φ

设定序列

设定序列

设定序列

本发明采用递推结构计算CZT变换系数,计算精简,耗费资源少,既避免了传统FPGA 实现模式使用占大量内存的DDS产生器,又避免了直接计算相角所需要的求平方等复杂计算,整个FPGA处理架构采用并行资源流水处理,实现了CZT变换的高效率快速计算。

附图说明

图1是CZT变换的FPGA实现流程图,图2是c(n)的FPGA实现流程图,图3是h(n) 的FPGA实现流程图,图4是u(k)的FPGA实现流程图。

具体实施方式

以下结合附图对本发明的技术方案做具体的说明。

设定c(n)的相角为φ

设定序列

设定序列

设定序列

上述作为本发明的实施例,并不限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均包含在本发明的保护范围之内。

- 一种实现CZT变换的FPGA架构

- 一种适用于FPGA实现的CPU架构