一种抗单粒子瞬态与噪声干扰的高压电平移位电路

文献发布时间:2023-06-19 11:06:50

技术领域

本发明涉及高压电平移位电路,尤其涉及抗单粒子瞬态与噪声干扰的高压电平移位电路。

背景技术

传统的高压电平移位电路一般采用双窄脉冲触发结构,首先将输入的长周期脉冲波形转化为上升沿与下降沿对应的两个窄脉冲波形,再利用两个窄脉冲波形周期性的开启两个高压LDMOS功率晶体管,进而实现电平从低压到高压的移位,最终通过RS触发器对输入的波形周期进行重建。航天器在轨期间,空间高能重离子入射高压LDMOS器件,通过电离相互作用可以在器件内部沉积大量电子空穴对,在电场的作用下电子空穴对将往两极运动,进而产生单粒子瞬态效应。单粒子瞬态脉冲能够引起传统高压电平移位电路发生误触发,进而导致功率输出级晶体管发生直通,严重威胁航天器的在轨安全。

发明内容

本发明提供的抗单粒子瞬态与噪声干扰的高压电平移位电路,以解决现有技术中存在的单粒子瞬态效应对电压电平移位电路的影响,不仅可以实现对 LDMOS功率晶体管单粒子瞬态脉冲的免疫,而且能够有效的抑制电路的共模噪声,具有极大的应用价值。

为解决上述技术问题,本发明提供的技术方案为:

本发明提供的一种抗单粒子瞬态与噪声干扰的高压电平移位电路,包括第一输入端口、第二输入端口、第一电平移位支路、第二电平移位支路、高压偏置端口、RS触发器、驱动电路和输出端口;所述第一电平移位支路包括第一 LDMOS晶体管、第四LDMOS晶体管、第一电压钳位电路、第四电压钳位电路、第一或门和第一滤波电路;所述第一输入端口连接所述第一LDMOS晶体管的栅极、所述第四LDMOS晶体管的栅极;所述第一LDMOS晶体管的源极、所述第四LDMOS晶体管的源极均接地;所述第一LDMOS晶体管的漏极通过所述第一电压钳位电路连接所述高压偏置端口;所述第四LDMOS晶体管的漏极通过所述第四电压钳位电路连接所述高压偏置端口;所述第一LDMOS晶体管的漏极、所述第四LDMOS晶体管的漏极分别连接所述第一或门的两个输入端;所述第一或门的输出端连接所述第一滤波电路的输入端;所述第二电平移位支路包括第二 LDMOS晶体管、第三LDMOS晶体管、第二电压钳位电路、第三电压钳位电路、第二或门和第二滤波电路;所述第二输入端口连接所述第二LDMOS晶体管的栅极、所述第三LDMOS晶体管的栅极;所述第二LDMOS晶体管的源极、所述第三LDMOS晶体管的源极均接地;所述第二LDMOS晶体管的漏极通过所述第二电压钳位电路连接所述高压偏置端口;所述第三LDMOS晶体管的漏极通过所述第三电压钳位电路连接所述高压偏置端口;所述第二LDMOS晶体管的漏极、所述第三LDMOS晶体管的漏极分别连接所述第二或门的两个输入端;所述第二或门的输出端连接所述第二滤波电路的输入端;所述第一滤波电路的输出端、所述第二滤波电路的输出端分别所述RS触发器的一个输入端连接;所述RS触发器的输出端与所述驱动电路的输入端连接;所述驱动电路的输出端与所述输出端口连接。

本发明提供的抗单粒子瞬态与噪声干扰的高压电平移位电路,优选地,还包括噪声检测锁定电路;所述噪声检测锁定电路包括第一PMOS晶体管、第二 PMOS晶体管;所述第一PMOS晶体管的栅极连接所述第二LDMOS晶体管的漏极;所述第一PMOS晶体管的源极连接所述高压偏置端口;所述第一PMOS晶体管的漏极连接所述第一LDMOS晶体管的漏极;所述第二PMOS晶体管的栅极连接所述第四LDMOS晶体管的漏极;所述第二PMOS晶体管的源极连接所述高压偏置端口;所述第二PMOS晶体管的漏极连接所述第三LDMOS晶体管的漏极。

本发明提供的抗单粒子瞬态与噪声干扰的高压电平移位电路,优选地,所述第一电压钳位电路、所述第二电压钳位电路、所述第三电压钳位电路和所述第四电压钳位电路均由电压钳位电路构成;所述电压钳位电路包括电阻和若干齐纳二极管;若干所述齐纳二极管同向串联,并与所述电阻并联;所述电阻与所述齐纳二极管的阳极连接点为所述电压钳位电路的输入端;所述电阻与所述齐纳二极管的阴极连接点为所述电压钳位电路的输出端;所述第一电压钳位电路的输入端与所述第一LDMOS晶体管的漏极连接、所述第一电压钳位电路的输出端与所述高压偏置端口连接;所述第二电压钳位电路的输入端与所述第二LDMOS晶体管的漏极连接、所述第二电压钳位电路的输出端与所述高压偏置端口连接;所述第三电压钳位电路的输入端与所述第三LDMOS晶体管的漏极连接、所述第三电压钳位电路的输出端与所述高压偏置端口连接;所述第四电压钳位电路的输入端与所述第四LDMOS晶体管的漏极连接、所述第四电压钳位电路的输出端与所述高压偏置端口连接。

本发明提供的抗单粒子瞬态与噪声干扰的高压电平移位电路,优选地,还包括高压浮动地端口;所述第一或门的电源端、所述第二或门的电源端、所述第一滤波电路的电源端、所述第二滤波电路的电源端、所述RS触发器的电源端、所述驱动电路的电源端均连接所述高压偏置端口;所述第一或门的地端、所述第二或门的地端、所述第一滤波电路的地端、所述第二滤波电路的地端、所述 RS触发器的地端、所述驱动电路的地端均与所述高压浮动地端口连接。

本发明具有如下优点:

本发明提供的一种抗单粒子瞬态与噪声干扰的高压电平移位电路,结合共模噪声抑制与冗余加固的原理,提供了双节点触发耦合的高压电平移位电路结构,不仅可以实现对LDMOS功率晶体管单粒子瞬态脉冲的免疫,而且能够有效的抑制电路中的共模噪声,展现了良好的太空应用前景。

附图说明

通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明及其特征、外形和优点将会变得更加明显。在全部附图中相同的标记指示相同的部分。并未刻意按照比例绘制附图,重点在于示出本发明的主旨。

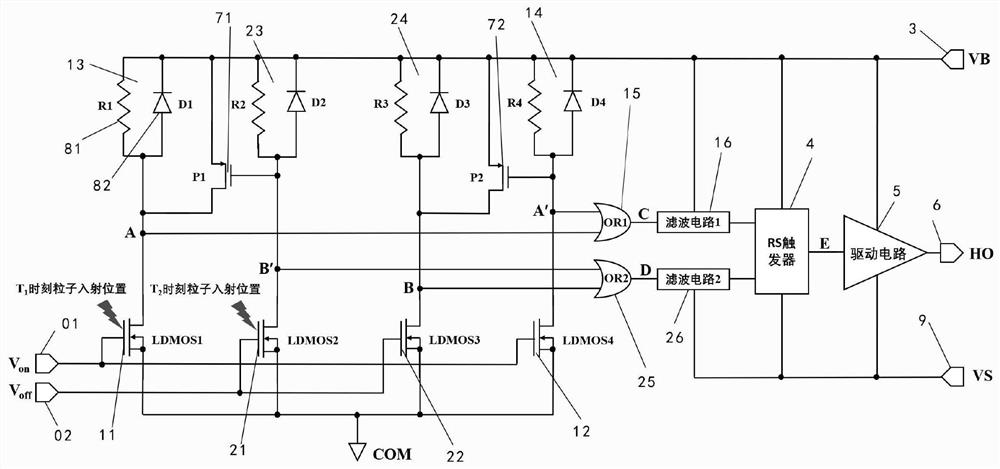

图1是本发明抗单粒子瞬态与噪声干扰的高压电平移位电路原理图;

图2是本发明电路正常工作状态波形图;

图3是高能粒子入射本发明电路示意图;

图4是本发明电路抗单粒子瞬态脉冲波形图;

图5是本发明电路抗噪声干扰波形图。

具体实施方式

需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。需要注意的是,本发明所使用的术语仅是为了描述具体实施方式,而非意图限制根据本申请的示例性实施方式。

实施例1:

如图1所示,本发明实施例1提供的一种抗单粒子瞬态与噪声干扰的高压电平移位电路,包括第一输入端口01、第二输入端口02、第一电平移位支路1、第二电平移位支路2、高压偏置端口3、RS触发器4、驱动电路5和输出端口6;第一电平移位支路1包括第一LDMOS晶体管11、第四LDMOS晶体管12、第一电压钳位电路13、第四电压钳位电路14、第一或门15和第一滤波电路16;第一输入端口01连接第一LDMOS晶体管11的栅极、第四LDMOS晶体管12的栅极;第一LDMOS晶体管11的源极、第四LDMOS晶体管12的源极均接地;第一LDMOS晶体管11的漏极通过第一电压钳位电路13连接高压偏置端口3;第四LDMOS晶体管12的漏极通过第四电压钳位电路14连接高压偏置端口3;第一LDMOS晶体管11的漏极、第四LDMOS晶体管12的漏极分别连接第一或门15 的两个输入端;第一或门15的输出端连述第一滤波电路16的输入端;第二电平移位支路2包括第二LDMOS晶体管21、第三LDMOS晶体管22、第二电压钳位电路23、第三电压钳位电路24、第二或门25和第二滤波电路26;第二输入端口02连接第二LDMOS晶体管21的栅极、第三LDMOS晶体管22的栅极;第二LDMOS晶体管21的源极、第三LDMOS晶体管22的源极均接地;第二LDMOS 晶体管21的漏极通过第二电压钳位电路23连接高压偏置端口3;第三LDMOS 晶体管22的漏极通过第三电压钳位电路24连接高压偏置端口;第二LDMOS晶体管21的漏极、第三LDMOS晶体管22的漏极分别连接第二或门25的两个输入端;第二或门25的输出端连接第二滤波电路26的输入端;第一滤波电路16的输出端、第二滤波电路26的输出端分别RS触发器4的一个输入端连接;RS触发器4的输出端与驱动电路5的输入端连接;驱动电路5的输出端与输出端口 6连接。

优选地,第一电压钳位电路13、第二电压钳位电路23、第三电压钳位电路 24和第四电压钳位电路14均由电压钳位电路构成;电压钳位电路包括电阻81 和齐纳二极管82;齐纳二极管82与电阻81并联;电阻81与齐纳二极管82的阳极连接点为电压钳位电路的输入端;电阻81与齐纳二极管82的阴极连接点为电压钳位电路的输出端;第一电压钳位电路13的输入端与第一LDMOS晶体管11的漏极连接、第一电压钳位电路13的输出端与高压偏置端口3连接;第二电压钳位电路23的输入端与第二LDMOS晶体管21的漏极连接、第二电压钳位电路23的输出端与高压偏置端口3连接;第三电压钳位电路24的输入端与第三LDMOS晶体管22的漏极连接、第三电压钳位电路24的输出端与高压偏置端口3连接;第四电压钳位电路14的输入端与第四LDMOS晶体管12的漏极连接、第四电压钳位电路14的输出端与高压偏置端口3连接。

优选地,还包括高压浮动地端口9;第一或门15的电源端、第二或门25 的电源端、第一滤波电路16的电源端、第二滤波电路26的电源端、RS触发器 4的电源端、驱动电路5的电源端均连接高压偏置端口3;第一或门15的地端、第二或门25的地端、第一滤波电路16的地端、第二滤波电路26的地端、RS 触发器4的地端、驱动电路5的地端均与高压浮动地端口9连接。

第一输入端口01同时开关第一LDMOS晶体管11与第四LDMOS晶体管12;第二输入端口02同时开关第二LDMOS晶体管21与第三LDMOS晶体管22。如图2所示,PWM波形经前端窄脉冲产生电路转化为两路窄脉冲信号分别输入第一输入端口01和第二输入端口02;第一输入端口01输入上升沿窄脉冲输入信号V

当电路工作在宇宙空间时,假设先后有两个高能粒子入射高压功率晶体管,分别为T

同理,高能粒子也可以在不同的时刻入射第三LDMOS晶体管22与第四 LDMOS晶体管12,进而在节点B与A′产生单粒子瞬态脉冲波形,由于各自对应的冗余节点分别保持了高电平,所以瞬态脉冲都无法通过或门进入后续电路,因此本发明实施例1提供的高压电平移位电路具备较高的抗单粒子瞬态扰动的能力。

为了使本发明实施例1中电路结构具备较强的抗噪声干扰能力,优选地,还包括噪声检测锁定电路7;噪声检测锁定电路7包括第一PMOS晶体管71、第二PMOS晶体管72;第一PMOS晶体管71的栅极连接第二LDMOS晶体管21 的漏极;第一PMOS晶体管71的源极连接高压偏置端口3;第一PMOS晶体管 71的漏极连接第一LDMOS晶体管11的漏极;第二PMOS晶体管72的栅极连接第四LDMOS晶体管12的漏极;第二PMOS晶体管72的源极连接高压偏置端口 3;第二PMOS晶体管72的漏极连接第三LDMOS晶体管22的漏极。如图5所示。当VS从0开始往高压浮动时,电路将会在动态对LDMOS功率晶体管的漏极充电并产生位移电流,进而在钳位电阻上产生电压降,可以在第一LDMOS晶体管 11、第二LDMOS晶体管21、第三LDMOS晶体管22与第四LDMOS晶体管12 的漏极形成共模噪声干扰信号。由于噪声捡测锁定电路的存在,当节点A′检测到电压降的时候,将会同步打开第二PMOS晶体管72,将B节点快速拉至高电平VB;同理,当节点B′检测到电压降的时候,将会同步打开第一PMOS晶体管 71,将A节点快速拉至高电平VB。通过以上噪声检测互锁机制,最终节点A与 B的噪声得到了快速的抑制,由于只有同相的低电平可以通过后续或门,所以单独的节点A′或B′噪声信号均无法进入后续电路。如图5所示,节点C与D基本不会受到噪声信号显著的干扰,整体电路电平移位功能正常,具备较强的抗噪声干扰能力。

综上所述,本发明提供的一种抗单粒子瞬态与噪声干扰的高压电平移位电路,结合共模噪声抑制与冗余加固的原理,提供了双节点触发耦合的高压电平移位电路结构,不仅可以实现对LDMOS功率晶体管单粒子瞬态脉冲的免疫,而且能够有效的抑制电路中的共模噪声,展现了良好的太空应用前景。

以上所述仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

- 一种抗单粒子瞬态与噪声干扰的高压电平移位电路

- 一种抗单粒子瞬态与噪声干扰的高压电平移位电路