一种内嵌式显示屏的GIP驱动电路及其控制方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及GIP驱动电路技术领域,特别涉及一种内嵌式显示屏的GIP驱 动电路及其控制方法。

背景技术

显示屏的GIP(即Gate In Panel)驱动电路的输出波形由于受TFT漏电的影 响,从而导致GIP输出波形会失真,GIP波形的失真会使得显示屏内显示区域 的TFT开启和关闭出现问题,从而导致显示屏的显示异常。

发明内容

本发明所要解决的技术问题是:提供一种内嵌式显示屏的GIP驱动电路及 其控制方法,使得GIP的输出波形不失真,从而使得显示屏显示效果不失真。

为了解决上述技术问题,本发明采用的第一种技术方案为:

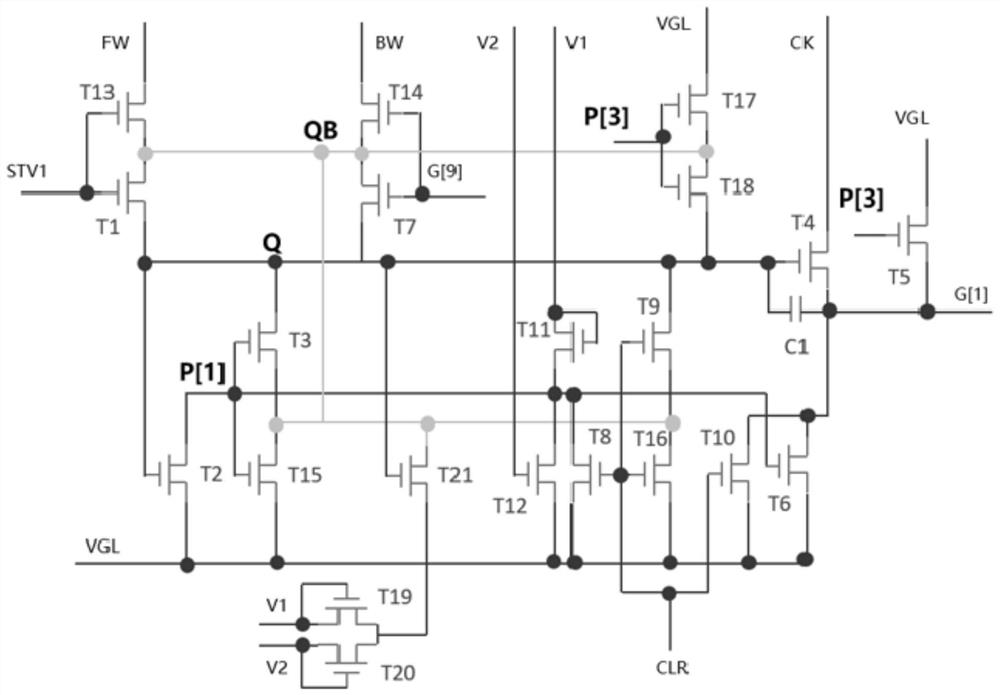

一种内嵌式显示屏的GIP驱动电路,包括晶体管T1、晶体管T2、晶体管 T3、晶体管T4、晶体管T5、晶体管T6、晶体管T7、晶体管T8、晶体管T9、 晶体管T10、晶体管T11、晶体管T12、晶体管T13、晶体管T14、晶体管T15、 晶体管T16、晶体管T17、晶体管T18、晶体管T19、晶体管T20、晶体管T21 和电容C1,所述晶体管T1的栅极与晶体管T13的栅极电连接且晶体管T1的栅 极和晶体管T13的栅极均接第一栅极走线,所述晶体管T1的漏极分别与晶体管 T13的源极、晶体管T14的源极、晶体管T7的漏极、晶体管T17的源极、晶体 管T18的漏极、晶体管T3的源极、晶体管T15的漏极、晶体管T21的漏极、 晶体管T16的源极和晶体管T9的源极电连接,所述晶体管T1的源极分别与晶 体管T2的栅极、晶体管T3的漏极、晶体管T7的漏极、晶体管T21的栅极、 晶体管T9的漏极、晶体管T18的漏极、晶体管T4的栅极和电容C1的一端电 连接,所述晶体管T3的栅极分别与晶体管T2的漏极、晶体管T15的栅极、晶 体管T12的栅极、晶体管T8的漏极和晶体管T6的栅极电连接,所述晶体管T2 的源极分别与晶体管T15的源极、晶体管T12的源极、晶体管T8的源极、晶体 管T16的源极、晶体管T10的源极和晶体管T6的源极电连接,所述晶体管T21 的源极分别与晶体管T19的源极和晶体管T20的漏极电连接,所述晶体管T8 的栅极分别与晶体管T9的栅极、晶体管T16的栅极和晶体管T10的栅极电连接,所述晶体管T10的漏极分别与晶体管T6的漏极、电容C1的另一端、晶体管T4 的源极和晶体管T5的源极电连接且晶体管T10的漏极、晶体管T6的漏极、电 容C1的另一端、晶体管T4的源极和晶体管T5的源极均接第二栅极走线,所述 晶体管T14的栅极与晶体管T7的栅极电连接且晶体管T14的栅极和晶体管T7 的栅极均接第三栅极走线。

本发明采用的第二种技术方案为:

一种内嵌式显示屏的GIP驱动电路的控制方法,包括以下步骤:

S1、在第一时刻,控制晶体管T1的栅极和晶体管T13的栅极输入高电平;

S2、在第二时刻,控制晶体管T4的漏极输入高电平;

S3、在第三时刻,控制晶体管T7的栅极和晶体管T14的栅极输入高电平。

本发明的有益效果在于:

通过将晶体管T1的栅极与晶体管T13的栅极电连接且晶体管T1的栅极和 晶体管T13的栅极均接第一栅极走线,晶体管T1的源极分别与晶体管T2的栅 极、晶体管T3的漏极、晶体管T7的漏极、晶体管T21的栅极、晶体管T9的 漏极、晶体管T18的漏极、晶体管T4的栅极和电容C1的一端电连接,晶体管 T10的漏极分别与晶体管T6的漏极、电容C1的另一端、晶体管T4的源极和晶 体管T5的源极电连接且晶体管T10的漏极、晶体管T6的漏极、电容C1的另一端、晶体管T4的源极和晶体管T5的源极均接第二栅极走线,晶体管T14的 栅极与晶体管T7的栅极电连接且晶体管T14的栅极和晶体管T7的栅极均接第 三栅极走线,让GIP驱动电路的Q点(即晶体管T1的源极、晶体管T3的漏极、 晶体管T7的源极、晶体管T21的栅极、晶体管T9的漏极、晶体管T18的源极、 晶体管T4的栅极和电容C1的一端的公共端点处)电压变得稳定,使得下拉的 TFT没有漏电产生,改善GIP的输出波形,节约了改善GIP材料的成本,提高 显示屏的显示品质。

附图说明

图1为根据本发明的一种内嵌式显示屏的GIP驱动电路的结构示意图;

图2为根据本发明的一种内嵌式显示屏的GIP驱动电路的结构示意图;

图3为根据本发明的一种内嵌式显示屏的GIP驱动电路的结构示意图;

图4为根据本发明的一种内嵌式显示屏的GIP驱动电路的结构示意图;

图5为根据本发明的一种内嵌式显示屏的GIP驱动电路的结构示意图;

图6为根据本发明的一种内嵌式显示屏的GIP驱动电路的结构示意图;

图7为根据本发明的一种内嵌式显示屏的GIP驱动电路的结构示意图;

图8为根据本发明的一种内嵌式显示屏的GIP驱动电路的时序波形图;

图9为根据本发明的一种内嵌式显示屏的GIP驱动电路的时序波形图;

图10为根据本发明的一种内嵌式显示屏的GIP驱动电路的时序波形图;

图11为根据本发明的一种内嵌式显示屏的GIP驱动电路的时序波形图;

图12为根据本发明的一种内嵌式显示屏的GIP驱动电路的控制方法的步骤 流程图。

具体实施方式

为详细说明本发明的技术内容、所实现目的及效果,以下结合实施方式并 配合附图予以说明。

请参照图1,本发明提供的一种技术方案:

一种内嵌式显示屏的GIP驱动电路,包括晶体管T1、晶体管T2、晶体管 T3、晶体管T4、晶体管T5、晶体管T6、晶体管T7、晶体管T8、晶体管T9、 晶体管T10、晶体管T11、晶体管T12、晶体管T13、晶体管T14、晶体管T15、 晶体管T16、晶体管T17、晶体管T18、晶体管T19、晶体管T20、晶体管T21 和电容C1,所述晶体管T1的栅极与晶体管T13的栅极电连接且晶体管T1的栅 极和晶体管T13的栅极均接第一栅极走线,所述晶体管T1的漏极分别与晶体管 T13的源极、晶体管T14的源极、晶体管T7的漏极、晶体管T17的源极、晶体 管T18的漏极、晶体管T3的源极、晶体管T15的漏极、晶体管T21的漏极、 晶体管T16的源极和晶体管T9的源极电连接,所述晶体管T1的源极分别与晶 体管T2的栅极、晶体管T3的漏极、晶体管T7的漏极、晶体管T21的栅极、 晶体管T9的漏极、晶体管T18的漏极、晶体管T4的栅极和电容C1的一端电 连接,所述晶体管T3的栅极分别与晶体管T2的漏极、晶体管T15的栅极、晶 体管T12的栅极、晶体管T8的漏极和晶体管T6的栅极电连接,所述晶体管T2 的源极分别与晶体管T15的源极、晶体管T12的源极、晶体管T8的源极、晶体 管T16的源极、晶体管T10的源极和晶体管T6的源极电连接,所述晶体管T21 的源极分别与晶体管T19的源极和晶体管T20的漏极电连接,所述晶体管T8 的栅极分别与晶体管T9的栅极、晶体管T16的栅极和晶体管T10的栅极电连接,所述晶体管T10的漏极分别与晶体管T6的漏极、电容C1的另一端、晶体管T4 的源极和晶体管T5的源极电连接且晶体管T10的漏极、晶体管T6的漏极、电 容C1的另一端、晶体管T4的源极和晶体管T5的源极均接第二栅极走线,所述 晶体管T14的栅极与晶体管T7的栅极电连接且晶体管T14的栅极和晶体管T7 的栅极均接第三栅极走线。

从上述描述可知,本发明的有益效果在于:

通过将晶体管T1的栅极与晶体管T13的栅极电连接且晶体管T1的栅极和 晶体管T13的栅极均接第一栅极走线,晶体管T1的源极分别与晶体管T2的栅 极、晶体管T3的漏极、晶体管T7的漏极、晶体管T21的栅极、晶体管T9的 漏极、晶体管T18的漏极、晶体管T4的栅极和电容C1的一端电连接,晶体管 T10的漏极分别与晶体管T6的漏极、电容C1的另一端、晶体管T4的源极和晶 体管T5的源极电连接且晶体管T10的漏极、晶体管T6的漏极、电容C1的另一端、晶体管T4的源极和晶体管T5的源极均接第二栅极走线,晶体管T14的 栅极与晶体管T7的栅极电连接且晶体管T14的栅极和晶体管T7的栅极均接第 三栅极走线,让GIP驱动电路的Q点(即晶体管T1的源极、晶体管T3的漏极、 晶体管T7的源极、晶体管T21的栅极、晶体管T9的漏极、晶体管T18的源极、 晶体管T4的栅极和电容C1的一端的公共端点处)电压变得稳定,使得下拉的 TFT没有漏电产生,改善GIP的输出波形,节约了改善GIP材料的成本,提高 显示屏的显示品质。

进一步的,所述晶体管T4的漏极接时钟信号。

进一步的,所述晶体管T11的栅极与晶体管T11的漏极电连接且晶体管T11 的栅极和晶体管T11的漏极均接第一电压,所述晶体管T12的栅极接第二电压, 所述晶体管T19的栅极与晶体管T19的漏极电连接且晶体管T19的栅极和晶体 管T19的漏极均接第一电压,所述晶体管T20的栅极与晶体管T20的漏极电连 接且晶体管T20的栅极和晶体管T20的漏极均接第二电压。

进一步的,所述晶体管T17的漏极接电源的负极,所述晶体管T2的源极、 晶体管T15的源极、晶体管T12的源极、晶体管T8的源极、晶体管T16的源 极、晶体管T10的源极和晶体管T6的源极均接电源的正极。

进一步的,所述晶体管T1、晶体管T2、晶体管T3、晶体管T4、晶体管T5、 晶体管T6、晶体管T7、晶体管T8、晶体管T9、晶体管T10、晶体管T11、晶 体管T12、晶体管T13、晶体管T14、晶体管T15、晶体管T16、晶体管T17、 晶体管T18、晶体管T19、晶体管T20和晶体管T21均为N沟道MOS管。

由上述描述可知,通过N沟道的MOS管能够进一步稳定GIP驱动电路的 输出波形,节约了改善GIP制程的成本,优化显示屏的显示效果。

请参照图12,本发明提供的另一种技术方案:

一种内嵌式显示屏的GIP驱动电路的控制方法,包括以下步骤:

S1、在第一时刻,控制晶体管T1的栅极和晶体管T13的栅极输入高电平;

S2、在第二时刻,控制晶体管T4的漏极输入高电平;

S3、在第三时刻,控制晶体管T7的栅极和晶体管T14的栅极输入高电平。

从上述描述可知,本发明的有益效果在于:

通过将晶体管T1的栅极与晶体管T13的栅极电连接且晶体管T1的栅极和 晶体管T13的栅极均接第一栅极走线,晶体管T1的源极分别与晶体管T2的栅 极、晶体管T3的漏极、晶体管T7的漏极、晶体管T21的栅极、晶体管T9的 漏极、晶体管T18的漏极、晶体管T4的栅极和电容C1的一端电连接,晶体管 T10的漏极分别与晶体管T6的漏极、电容C1的另一端、晶体管T4的源极和晶 体管T5的源极电连接且晶体管T10的漏极、晶体管T6的漏极、电容C1的另一端、晶体管T4的源极和晶体管T5的源极均接第二栅极走线,晶体管T14的 栅极与晶体管T7的栅极电连接且晶体管T14的栅极和晶体管T7的栅极均接第 三栅极走线,让GIP驱动电路的Q点(即晶体管T1的源极、晶体管T3的漏极、 晶体管T7的源极、晶体管T21的栅极、晶体管T9的漏极、晶体管T18的源极、 晶体管T4的栅极和电容C1的一端的公共端点处)电压变得稳定,使得下拉的 TFT没有漏电产生,改善GIP的输出波形,节约了改善GIP材料的成本,提高 显示屏的显示品质。

进一步的,步骤S1还包括以下步骤:

控制晶体管T4的漏极输入低电平。

进一步的,步骤S3还包括以下步骤:

控制晶体管T11的栅极输入高电平。

请参照图1至图11,本发明的实施例一为:

请参照图1,一种内嵌式显示屏的GIP驱动电路,包括晶体管T1、晶体管 T2、晶体管T3、晶体管T4、晶体管T5、晶体管T6、晶体管T7、晶体管T8、 晶体管T9、晶体管T10、晶体管T11、晶体管T12、晶体管T13、晶体管T14、 晶体管T15、晶体管T16、晶体管T17、晶体管T18、晶体管T19、晶体管T20、 晶体管T21和电容C1,所述晶体管T1的栅极与晶体管T13的栅极电连接且晶 体管T1的栅极和晶体管T13的栅极均接第一栅极走线,所述晶体管T1的漏极 分别与晶体管T13的源极、晶体管T14的源极、晶体管T7的漏极、晶体管T17 的源极、晶体管T18的漏极、晶体管T3的源极、晶体管T15的漏极、晶体管 T21的漏极、晶体管T16的源极和晶体管T9的源极电连接,所述晶体管T1的 源极分别与晶体管T2的栅极、晶体管T3的漏极、晶体管T7的漏极、晶体管 T21的栅极、晶体管T9的漏极、晶体管T18的漏极、晶体管T4的栅极和电容C1的一端电连接,所述晶体管T3的栅极分别与晶体管T2的漏极、晶体管T15 的栅极、晶体管T12的栅极、晶体管T8的漏极和晶体管T6的栅极电连接,所 述晶体管T2的源极分别与晶体管T15的源极、晶体管T12的源极、晶体管T8 的源极、晶体管T16的源极、晶体管T10的源极和晶体管T6的源极电连接,所 述晶体管T21的源极分别与晶体管T19的源极和晶体管T20的漏极电连接,所 述晶体管T8的栅极分别与晶体管T9的栅极、晶体管T16的栅极和晶体管T10的栅极电连接,所述晶体管T10的漏极分别与晶体管T6的漏极、电容C1的另 一端、晶体管T4的源极和晶体管T5的源极电连接且晶体管T10的漏极、晶体 管T6的漏极、电容C1的另一端、晶体管T4的源极和晶体管T5的源极均接第 二栅极走线,所述晶体管T14的栅极与晶体管T7的栅极电连接且晶体管T14 的栅极和晶体管T7的栅极均接第三栅极走线。

所述晶体管T4的漏极接时钟信号。

所述晶体管T11的栅极与晶体管T11的漏极电连接且晶体管T11的栅极和 晶体管T11的漏极均接第一电压,所述晶体管T12的栅极接第二电压,所述晶 体管T19的栅极与晶体管T19的漏极电连接且晶体管T19的栅极和晶体管T19 的漏极均接第一电压,所述晶体管T20的栅极与晶体管T20的漏极电连接且晶 体管T20的栅极和晶体管T20的漏极均接第二电压。

所述晶体管T17的漏极接电源的负极,所述晶体管T2的源极、晶体管T15 的源极、晶体管T12的源极、晶体管T8的源极、晶体管T16的源极、晶体管 T10的源极和晶体管T6的源极均接电源的正极。

所述晶体管T1、晶体管T2、晶体管T3、晶体管T4、晶体管T5、晶体管 T6、晶体管T7、晶体管T8、晶体管T9、晶体管T10、晶体管T11、晶体管T12、 晶体管T13、晶体管T14、晶体管T15、晶体管T16、晶体管T17、晶体管T18、 晶体管T19、晶体管T20和晶体管T21均为N沟道MOS管。

本方案的每一级GIP电路共有21颗TFT,1个电容C1,FW是直流高电压, 设为15V,BW和VGL均是直流低电压,设为-10V,在本方案中,CK(n)的 高电位是FW电位,CK(n)的低电位是-10V,CK(n)的高电位和低电位在数 值上和FW、VGL相等。对Q点来说,将电压上拉的TFT有晶体管T1、晶体管 T4和晶体管T13,将电压下拉的TFT有晶体管T3、晶体管T9、晶体管T15和晶体管T16。本方案通过控制QB节点的电压,使得晶体管T3和晶体管T9没 有漏电产生,从而Q点没有了漏电路径,Q点没有漏电产生,G(n)的波形才 不会失真。

对21T1C电路进行举例说明本方案的电路连接关系,本方案中以4个STV (GIP动作的开启电压波形)单侧的GIP为例,STV1作为G[1]和G[3]的开启电 压,STV3作为G[5]和G[7]的开启电压。

请参照图2,当n=1时,GIP输出波形是第一条Gate Line波形,记为G[1]。 P[3]是当n=3时的GIP电路的P点电压,即G[1]的GIP电路中的晶体管T5、晶 体管T17、晶体管T18的栅极与G[3]的P[3]连接。另外,晶体管T12的栅极连 接的信号是V2,晶体管T11的栅极连接的是V1信号。

请参照图3,当n=3时,GIP输出波形是第三条Gate Line波形,记为G[3]。 P[1]是当n=1时的GIP电路的P点电压,即G[3]的GIP电路中的晶体管T5、晶 体管T17、晶体管T18的栅极与G[1]的P[1]连接。另外,晶体管T12的栅极连 接的信号是V1,T11的栅极连接的是V2信号。

请参照图4,当n=5时,GIP输出波形是第五条Gate Line波形,记为G[5]。 P[3]是当n=3时的GIP电路的P点电压,即G[5]的GIP电路中的晶体管T5、晶 体管T17、晶体管T18的栅极与G[3]的P[3]连接。另外,晶体管T12的栅极连 接的信号是V2,晶体管T11的栅极连接的是V1信号。

请参照图5,当n=7时,GIP输出波形是第七条Gate Line波形,记为G[7]。 P[5]是当n=5时的GIP电路的P点电压,即G[7]的GIP电路中的晶体管T5、晶 体管T17、晶体管T18的栅极与G[5]的P[5]连接。另外,晶体管T12的栅极连 接的信号是V1,晶体管T11的栅极连接的是V2信号。

综上所述,单侧奇数GIP的晶体管T12与晶体管T11的栅极信号上下级GIP 给的信号是不同的,在这里可以简单理解为奇数侧GIP电路又划分为奇数和偶 数级GIP,相当于G[1]为奇数级,那晶体管T12的栅极连接的信号是V2,晶体 管T11的栅极连接的是V1信号。G[3]是偶数级,晶体管T12的栅极连接的信号 是V1,晶体管T11的栅极连接的是V2信号。G[5]为奇数级,那晶体管T12的 栅极连接的信号是V2,晶体管T11的栅极连接的是V1信号。G[7]是偶数级, 晶体管T12的栅极连接的信号是V1,晶体管T11的栅极连接的是V2信号。依 次反复给晶体管T12和晶体管T11的栅极传输对应的V1,V2信号。

请参照图6,当n=4i+5(i≥1)时,GIP的晶体管T5、晶体管T17、晶体管 T18的栅极连接关系是从第9级开始。G[7]的P点,P[7]与G[9]的晶体管T5、 晶体管T17、晶体管T18的栅极连接,G[11]的P点,P[11]与G[13]的晶体管T5、 晶体管T17、晶体管T18的栅极连接,依次按照G[n-2]的P点,P[n-2]与G[n] 的GIP电路中的晶体管T5、晶体管T17、晶体管T18的栅极连接的原则往下循 环。这里需要注意的是当n=4i+5(i≥1)时,所有GIP电路中的晶体管T12的 栅极连接的信号是V2,晶体管T11的栅极连接的是V1信号。

请参照图7,当n=4i+7(i≥1)时,GIP的晶体管T5、晶体管T17、晶体 管T18的栅极连接关系是从第11级开始。此电路的连接关系与图1中一样,但 须注意的是晶体管T12的栅极连接的信号是V1,晶体管T11的栅极连接的是 V2信号。

以下介绍第一帧GIP的驱动过程(请结合图8和图9分析):

在图8中,第一帧时,V1为高电压,记为V1=H,V2为低电压,记为V2=L。 当n=4i+1,i≥0时,可参考图7的GIP电路图,此时所有GIP电路中的晶体管 T12的栅极连接的信号是V2,晶体管T11的栅极连接的是V1信号。

在图6的GIP电路图中,参考图8(n=4i+1,i≥0)的时序图。在t1时刻, Vg[n-8](即G(n-8))为高电位,晶体管T1、晶体管T13、晶体管T2、晶体管 T4、晶体管T21打开,Q点充电到FW高电位,此时CK(n)为低电位状态, G[n]输出低电位。QB节点电位充到一个高电位(小于FW),P[n]节点由于晶体 管T2的打开,此节点被VGL拉到电位VGL状态。V1在一帧内一直为高电位, T11打开,但由于晶体管T2比晶体管T11的拉电压能力更强,因此P[n]依然是 被晶体管T2拉到低电位VGL。V2在一帧内一直是低电位,此时晶体管T12一 直处于关闭状态。

在t2时刻,CK(n)为高电位,Q[n]为高电位,晶体管T4保持打开状态, CK(n)通过晶体管T4将电压传给G[n],G[n]电压由低电位转变为高电位的同 时,由于电容C1的电容耦合作用,此时Q点电位由FW转变为FW+FW,这样 晶体管T4又会打开得更好。也由于Q[n]节点电位此时达到最高,晶体管T21 打开得最好,此时QB[n]节点充电充到FW准位。

在t2时刻,晶体管T3和晶体管T9是关闭的,晶体管T3和晶体管T9的 Gate电压为低电位VGL,此时由于QB[n]节点的电位为FW,则晶体管T3和晶 体管T9的Vgs=VGL-FW=-25V,根据TFT的特性曲线Vgs-Ids可知,在Vgs=-25V 电压情况下,Ids特别小,可忽略不计,则Q点没有了漏电路径。

在t3时刻,Vg[n+8](即G(n+8))为高电位,晶体管T14、晶体管T7打 开,Q[n]和QB[n]节点电压被拉到BW低电压准位,晶体管T2、晶体管T4、晶 体管T21处于关闭状态。在此时,由于晶体管T2的关闭,V1一直处于高电位 状态,晶体管T11也一直处于打开状态,P[n]此时充电到高电位。P[n]充电到高 电位,晶体管T6打开,晶体管T6将G[n]拉到低电位状态。

当n=4i+3时,i≥0时,可参考图7的GIP电路,此时所有GIP电路中的晶 体管T12的栅极连接的信号是V1,晶体管T11的栅极连接的是V2信号。由于 此时V1与T12连接,晶体管T12一直处于打开状态,晶体管T11一直处于关 闭状态,P[n]电压一直被晶体管T2和晶体管T12拉到VGL电位。此时Q[n]可 靠P[n-2]将电压拉到VGL电位,将Q[n]节点电荷放掉。

以下介绍第二帧GIP的驱动过程(请结合图10和图11分析):

第二帧与第一帧有区别的是,此时V1为低电压准位,V2为高电压准位。 在第二帧中,当n=4i+1时(i≥0),依旧参考图6的电路,与第一帧相比,由于此 时V1与晶体管T11的栅极相接,则晶体管T11处于关闭状态,V2与晶体管T12 相接,晶体管T12处于打开状态,使得P[n]一直被拉到VGL低电位。此时的 P[n-2]可将Q[n]点拉到VGL低电位。在第二帧中,当n=4i+3时(i≥0),参考图7 的电路,与第一帧相比,由于V2为高电位,晶体管T11在第二帧一直处于打开 状态,当晶体管T2关闭时,P[n]充电到高电位,可将晶体管T6打开,晶体管 T6再下拉G[n]到VGL低电位,G[n]关闭得更好。由于V1为低电位,晶体管 T12在第二帧一直处于关闭状态。其他的时序驱动过程与第一帧一样,在此不 做累述。

请参照图2至12,本发明的实施例二为:

请参照图12,一种内嵌式显示屏的GIP驱动电路的控制方法,包括以下步 骤:

S1、在第一时刻,控制晶体管T1的栅极和晶体管T13的栅极输入高电平;

S2、在第二时刻,控制晶体管T4的漏极输入高电平;

S3、在第三时刻,控制晶体管T7的栅极和晶体管T14的栅极输入高电平。

步骤S1还包括以下步骤:

控制晶体管T4的漏极输入低电平。

步骤S3还包括以下步骤:

控制晶体管T11的栅极输入高电平。

本方案的每一级GIP电路共有21颗TFT,1个电容C1,FW是直流高电压, 设为15V,BW和VGL均是直流低电压,设为-10V,在本方案中,CK(n)的 高电位是FW电位,CK(n)的低电位是-10V,CK(n)的高电位和低电位在数 值上和FW、VGL相等。对Q点来说,将电压上拉的TFT有晶体管T1、晶体管 T4和晶体管T13,将电压下拉的TFT有晶体管T3、晶体管T9、晶体管T15和晶体管T16。本方案通过控制QB节点的电压,使得晶体管T3和晶体管T9没 有漏电产生,从而Q点没有了漏电路径,Q点没有漏电产生,G(n)的波形才 不会失真。

对21T1C电路进行举例说明本方案的电路连接关系,本方案中以4个STV (GIP动作的开启电压波形)单侧的GIP为例,STV1作为G[1]和G[3]的开启电 压,STV3作为G[5]和G[7]的开启电压。

请参照图2,当n=1时,GIP输出波形是第一条Gate Line波形,记为G[1]。 P[3]是当n=3时的GIP电路的P点电压,即G[1]的GIP电路中的晶体管T5、晶 体管T17、晶体管T18的栅极与G[3]的P[3]连接。另外,晶体管T12的栅极连 接的信号是V2,晶体管T11的栅极连接的是V1信号。

请参照图3,当n=3时,GIP输出波形是第三条Gate Line波形,记为G[3]。 P[1]是当n=1时的GIP电路的P点电压,即G[3]的GIP电路中的晶体管T5、晶 体管T17、晶体管T18的栅极与G[1]的P[1]连接。另外,晶体管T12的栅极连 接的信号是V1,T11的栅极连接的是V2信号。

请参照图4,当n=5时,GIP输出波形是第五条Gate Line波形,记为G[5]。 P[3]是当n=3时的GIP电路的P点电压,即G[5]的GIP电路中的晶体管T5、晶 体管T17、晶体管T18的栅极与G[3]的P[3]连接。另外,晶体管T12的栅极连 接的信号是V2,晶体管T11的栅极连接的是V1信号。

请参照图5,当n=7时,GIP输出波形是第七条Gate Line波形,记为G[7]。P[5]是当n=5时的GIP电路的P点电压,即G[7]的GIP电路中的晶体管T5、晶 体管T17、晶体管T18的栅极与G[5]的P[5]连接。另外,晶体管T12的栅极连 接的信号是V1,晶体管T11的栅极连接的是V2信号。

综上所述,单侧奇数GIP的晶体管T12与晶体管T11的栅极信号上下级GIP 给的信号是不同的,在这里可以简单理解为奇数侧GIP电路又划分为奇数和偶 数级GIP,相当于G[1]为奇数级,那晶体管T12的栅极连接的信号是V2,晶体 管T11的栅极连接的是V1信号。G[3]是偶数级,晶体管T12的栅极连接的信号 是V1,晶体管T11的栅极连接的是V2信号。G[5]为奇数级,那晶体管T12的 栅极连接的信号是V2,晶体管T11的栅极连接的是V1信号。G[7]是偶数级, 晶体管T12的栅极连接的信号是V1,晶体管T11的栅极连接的是V2信号。依 次反复给晶体管T12和晶体管T11的栅极传输对应的V1,V2信号。

请参照图6,当n=4i+5(i≥1)时,GIP的晶体管T5、晶体管T17、晶体管 T18的栅极连接关系是从第9级开始。G[7]的P点,P[7]与G[9]的晶体管T5、 晶体管T17、晶体管T18的栅极连接,G[11]的P点,P[11]与G[13]的晶体管T5、 晶体管T17、晶体管T18的栅极连接,依次按照G[n-2]的P点,P[n-2]与G[n] 的GIP电路中的晶体管T5、晶体管T17、晶体管T18的栅极连接的原则往下循 环。这里需要注意的是当n=4i+5(i≥1)时,所有GIP电路中的晶体管T12的 栅极连接的信号是V2,晶体管T11的栅极连接的是V1信号。

请参照图7,当n=4i+7(i≥1)时,GIP的晶体管T5、晶体管T17、晶体 管T18的栅极连接关系是从第11级开始。此电路的连接关系与图1中一样,但 须注意的是晶体管T12的栅极连接的信号是V1,晶体管T11的栅极连接的是 V2信号。

以下介绍第一帧GIP的驱动过程(请结合图8和图9分析):

在图8中,第一帧时,V1为高电压,记为V1=H,V2为低电压,记为V2=L。 当n=4i+1,i≥0时,可参考图7的GIP电路图,此时所有GIP电路中的晶体管 T12的栅极连接的信号是V2,晶体管T11的栅极连接的是V1信号。

在图6的GIP电路图中,参考图8(n=4i+1,i≥0)的时序图。在t1时刻, Vg[n-8](即G(n-8))为高电位,晶体管T1、晶体管T13、晶体管T2、晶体管T4、晶体管T21打开,Q点充电到FW高电位,此时CK(n)为低电位状态, G[n]输出低电位。QB节点电位充到一个高电位(小于FW),P[n]节点由于晶体 管T2的打开,此节点被VGL拉到电位VGL状态。V1在一帧内一直为高电位, T11打开,但由于晶体管T2比晶体管T11的拉电压能力更强,因此P[n]依然是 被晶体管T2拉到低电位VGL。V2在一帧内一直是低电位,此时晶体管T12一 直处于关闭状态。

在t2时刻,CK(n)为高电位,Q[n]为高电位,晶体管T4保持打开状态, CK(n)通过晶体管T4将电压传给G[n],G[n]电压由低电位转变为高电位的同 时,由于电容C1的电容耦合作用,此时Q点电位由FW转变为FW+FW,这样 晶体管T4又会打开得更好。也由于Q[n]节点电位此时达到最高,晶体管T21 打开得最好,此时QB[n]节点充电充到FW准位。

在t2时刻,晶体管T3和晶体管T9是关闭的,晶体管T3和晶体管T9的 Gate电压为低电位VGL,此时由于QB[n]节点的电位为FW,则晶体管T3和晶 体管T9的Vgs=VGL-FW=-25V,根据TFT的特性曲线Vgs-Ids可知,在Vgs=-25V 电压情况下,Ids特别小,可忽略不计,则Q点没有了漏电路径。

在t3时刻,Vg[n+8](即G(n+8))为高电位,晶体管T14、晶体管T7打 开,Q[n]和QB[n]节点电压被拉到BW低电压准位,晶体管T2、晶体管T4、晶 体管T21处于关闭状态。在此时,由于晶体管T2的关闭,V1一直处于高电位 状态,晶体管T11也一直处于打开状态,P[n]此时充电到高电位。P[n]充电到高 电位,晶体管T6打开,晶体管T6将G[n]拉到低电位状态。

当n=4i+3时,i≥0时,可参考图7的GIP电路,此时所有GIP电路中的晶 体管T12的栅极连接的信号是V1,晶体管T11的栅极连接的是V2信号。由于 此时V1与T12连接,晶体管T12一直处于打开状态,晶体管T11一直处于关 闭状态,P[n]电压一直被晶体管T2和晶体管T12拉到VGL电位。此时Q[n]可 靠P[n-2]将电压拉到VGL电位,将Q[n]节点电荷放掉。

以下介绍第二帧GIP的驱动过程(请结合图10和图11分析):

第二帧与第一帧有区别的是,此时V1为低电压准位,V2为高电压准位。 在第二帧中,当n=4i+1时(i≥0),依旧参考图6的电路,与第一帧相比,由于此 时V1与晶体管T11的栅极相接,则晶体管T11处于关闭状态,V2与晶体管T12 相接,晶体管T12处于打开状态,使得P[n]一直被拉到VGL低电位。此时的 P[n-2]可将Q[n]点拉到VGL低电位。在第二帧中,当n=4i+3时(i≥0),参考图7 的电路,与第一帧相比,由于V2为高电位,晶体管T11在第二帧一直处于打开 状态,当晶体管T2关闭时,P[n]充电到高电位,可将晶体管T6打开,晶体管 T6再下拉G[n]到VGL低电位,G[n]关闭得更好。由于V1为低电位,晶体管 T12在第二帧一直处于关闭状态。其他的时序驱动过程与第一帧一样,在此不 做累述。

综上所述,本发明提供的一种内嵌式显示屏的GIP驱动电路及其控制方法, 通过将晶体管T1的栅极与晶体管T13的栅极电连接且晶体管T1的栅极和晶体 管T13的栅极均接第一栅极走线,晶体管T1的源极分别与晶体管T2的栅极、 晶体管T3的漏极、晶体管T7的漏极、晶体管T21的栅极、晶体管T9的漏极、 晶体管T18的漏极、晶体管T4的栅极和电容C1的一端电连接,晶体管T10的 漏极分别与晶体管T6的漏极、电容C1的另一端、晶体管T4的源极和晶体管 T5的源极电连接且晶体管T10的漏极、晶体管T6的漏极、电容C1的另一端、 晶体管T4的源极和晶体管T5的源极均接第二栅极走线,晶体管T14的栅极与 晶体管T7的栅极电连接且晶体管T14的栅极和晶体管T7的栅极均接第三栅极 走线,让GIP驱动电路的Q点(即晶体管T1的源极、晶体管T3的漏极、晶体 管T7的源极、晶体管T21的栅极、晶体管T9的漏极、晶体管T18的源极、晶 体管T4的栅极和电容C1的一端的公共端点处)电压变得稳定,使得下拉的TFT 没有漏电产生,改善GIP的输出波形,节约了改善GIP材料的成本,提高显示 屏的显示品质。

以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利 用本发明说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术 领域,均同理包括在本发明的专利保护范围内。

- 一种内嵌式显示屏的GIP驱动电路及其控制方法

- 一种低功耗显示屏的GIP驱动电路及其控制方法