使用级联差分晶体管对实现逻辑的光子发射器驱动器

文献发布时间:2023-06-19 12:16:29

技术领域

本申请涉及光子发射器驱动器,更详而言之,涉及使用级联差分晶体管对(cascaded differential transistor pair)的光子发射器驱动器。

背景技术

在光学数据传输系统中,发射器(emitter或transmitter)经常使用各种类型的驱动器,其中之一是脉冲幅度调制(pulse amplitude modulation;PAM)驱动器。电性接口(interface)中使用的一个或多个调制格式包括诸如不归零(non-return to zero;NRZ),4进制,8进制,N进制等格式的脉冲幅度调制(PAM-4,PAM-8,PAM-N等)。PAM-4是为了便于说明和讨论而在本申请中使用的多级幅度调制的一个示例,然而,本领域普通技术人员应当理解,使用本文中的PAM-4示例的所有讨论同样适用于其他调制格式,因此,本申请所附的权利要求书意在适用于所有此类格式,无论是当前已知的还是将来开发的。在此PAM-4驱动器的示例中,将同时处理信息的两个二进制位(双二进制)。在此中使用

围绕四电平(4-level)脉冲幅度调制驱动器电路的一个问题涉及无法进行超过20GHz的高频或更大带宽的操作。这种局限性可以追溯到PAM-4实现(implementation)中涉及的许多子电路。具体而言,PAM-4的实现涉及用于格雷编码(Gray coding)、PAM-4逻辑生成、缓冲、模拟求和等的子电路。当级联连接时,这些构建块中的每一个都增加了电容性负载,从而降低了整体带宽。亚纳米(sub-nanometric)技术节点中的低电源电压限制了每个子块中的输出摆幅,在缓冲操作期间需要更多的级联级,进而导致运作速度受到级联系统的增益带宽乘积的限制。

此问题的一种解决方案是堆叠晶体管以实现驱动常用的光子调制器,马赫曾德尔调制器(Mach-Zehnder modulator;MZM)所需的更高的电压电平(例如3V或更高)。晶体管的堆叠与硅面积和功耗成正比。互补金属氧化物半导体(complementary metal oxidesemiconductor;CMOS)和电流模式逻辑(current-mode logic;CML)装置两者都需要晶体管堆叠来实现各种逻辑功能,例如异或(XOR)、多路复用(MUX)、与(AND)等。然而,对于任何类型的PAM-4或双二进制运算,在高数据速率下,这些电路都难以在低于1V的电源电压下运作。

发明内容

本文的各种驱动电路包括连接到外部多路复用器(multiplexor)和缓冲器的数字(digital)输入。该数字输入可以是第一数字输入和第二数字输入。该数字输入接收数字高电压或数字低电压下的电压。这些驱动器电路还具有连接到外部激光提供的传输调制器的时钟输入和步进模拟(analog)输出。

第一差分对晶体管和两个或多个第二差分对晶体管连接到数字输入,并组合以产生模拟输出。另外,电压限制器(voltage limiter)连接到时钟输入和该第二差分对晶体管。电压限制器向第二差分对晶体管提供不同的电压,这导致第一差分对晶体管和第二差分对晶体管在数字高电压处、数字低电压处、以及数字高电压和数字低电压之间以不同的电压步进(step)提供模拟输出。具体来说,构成电压限制器的晶体管的阈值电压决定了输出的不同电压步进。

需注意的是,本文的时钟输入仅连接到电压限制器,而不连接到第一差分对晶体管。此外,第一差分对晶体管和第二差分对晶体管中的晶体管连接到公共节点并被提供相同的电流。另外,第一差分对晶体管和第二差分对晶体管中的晶体管为相同尺寸和相同类型的晶体管。但是,这些晶体管与电压限制器的晶体管的尺寸不同。

此外,通过设置前述组件并且将第一晶体管差分对和第二晶体管差分对与模拟输出连接的电性连接的模式,以形成逻辑AND电路、逻辑OR电路、逻辑XOR电路等,以执行格雷编码(Gray encoding)、温度编码(temperature encoding)、加法运算(adding)等。

附图说明

通过以下参考附图的详细描述,将更好地本文中的实施例,这些附图不一定是按照比例绘制的,其中:

图1为根据本文中的各实施例的光发射器的示意图;

图2A至图2D分别为图1所示的通用驱动器的不同示例的示意图,即逻辑OR、XOR、AND,以及任何其他逻辑使用函数;以及

图3A至图3C分别为图2A至图2C所示具体示例的逻辑OR、XOR、AND电路的示意图。

主要附图标记说明

100 发射装置

102 多路复用器/缓冲器

104 时钟发生器

106 大摆幅调制驱动器(LSMD)

108 PAM-4驱动器、驱动电路

108A至108D 驱动器

110 调制器、传输调制器

112 激光器

114 分流电路

122A 第一差分对晶体管

122B至122C 第二差分对晶体管

124,126 电压限制器

128A 逻辑OR电路

128B 逻辑XOR电路

128C 逻辑AND电路

128D 任何逻辑

CLK 时钟输入

D1,

D2,

L1 电感、调谐电感

M1至M6 晶体管

M7至M8 晶体管(电压限制器)

Out,

R1 电阻、负载电阻

TX 光传输输出

VDD 电源电压。

具体实施方式

如上所述,PAM驱动电路可能无法进行高频或更大带宽的操作,甚至堆叠晶体管也存在硅面积和功耗影响。鉴于这些问题,本申请提出了使用相同的但基于电源电压差步进的级联差分晶体管对实现逻辑的光子发射器驱动器。再次,虽然在本讨论中使用PAM-4作为示例,但是本文中揭示的所有结构都可以以其他调制格式(PAM-4,PAM-8,PAM-N等)予以实现。

更详细地,这些示例性结构被呈现为在一个块(即温度计(一元)编码)中预执行PAM-4合成,且并行进行PAM-4逻辑生成和求和的单体单元(single cell)PAM-4发射器。本文中的驱动器不需要额外的阶段来进行缓冲和放大。因此,本申请提出了一种新的CML逻辑系列,其使用模拟输出(类似于数模转换(digital-to-analog;DAC)电路)代替了经典数字逻辑门(gate)的二进制输出。此处的驱动器提供基于存储器(memory)的逻辑门,在非限制性实施例中,基于与门(AND)、或门(OR)、异或门(XOR)的存储器。本文中的驱动器利用CML时钟(clocked)缓冲器和无时钟(unclocked)缓冲器的组合在漏极共享相同的输出。因此,这些结构使用与输入晶体管相同电平的电路时钟。

如附图所示且如以下详细讨论的,在本申请中作为示例呈现的PAM-4驱动电路使用时钟缓冲层和无时钟缓冲层,其中,输入信号和时钟信号两者都处于相同的电压电平。这些PAM-4驱动电路使用单个无时钟缓冲以及另一对时钟缓冲,该另一对时钟缓冲使用该时钟信号替换输入中的一个,以便以不同电压步进提供模拟类型的输出。在给出的示例中,电路配置创建基于AND、XOR和OR电路的存储器;然而,本领域的普通技术人员将理解,其他逻辑电路也可由此衍生,因此,所述逻辑电路也意图在本文中使用AND、XOR和OR电路作为所有此类逻辑电路的示例进行公开。

图1示出了一个示例性发射装置100,其包括各种多路复用器以及将各种数字信号输出到各种数字输入D1,

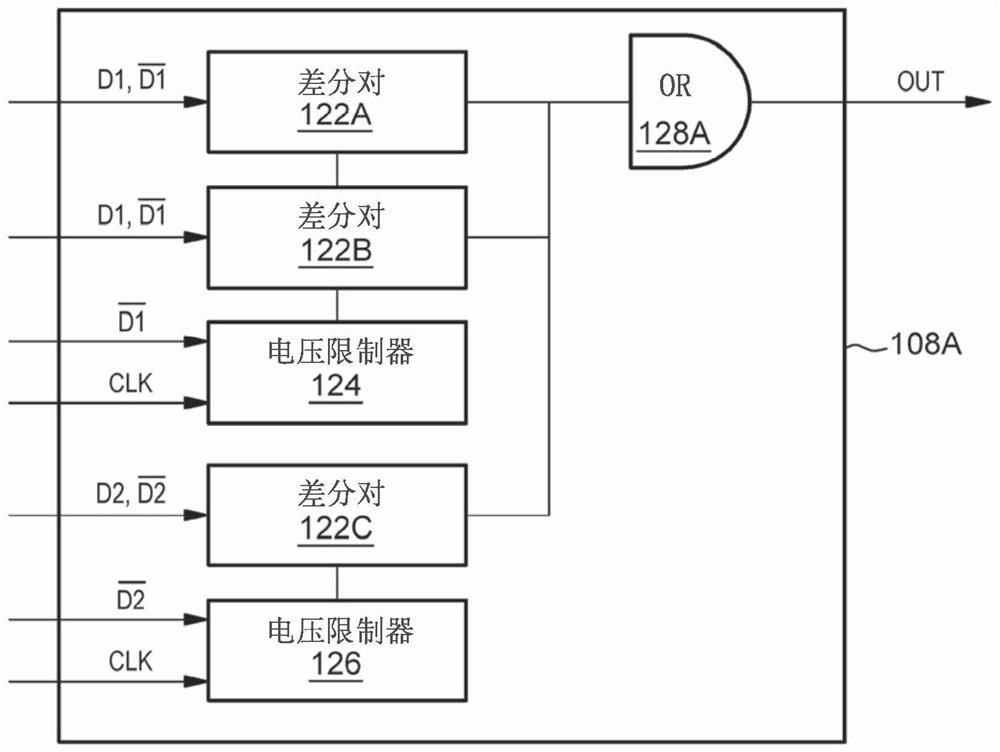

如图2A所示的示例,本文的驱动电路108包括连接至外部多路复用器和缓冲器102的数字输入D1,

图2A示出了连接到第一数字输入D1,

另外,图2A示出了电压限制器124,126,其包括连接至第一数字输入D1,

需注意的,此处的时钟输入(CLK)仅连接到电压限制器124,126而不连接到第一差分对晶体管122A。而且,第一差分对晶体管122A中的晶体管和第二差分对晶体管122B,122C中的晶体管被供应相同的电流。另外,第一差分对晶体管122A中的晶体管和第二差分对晶体管122B,122C中的晶体管具有相同尺寸和相同类型。然而,第一差分对晶体管122A中的晶体管和第二差分对晶体管122B,122C中的晶体管与电压限制器124,126的晶体管的尺寸不同。

如图2A至图2C所示,前述组件的布置以及将第一差分对晶体管122A和第二差分对晶体管122B,122C连接至模拟输出(Out)的电性连接以形成以下任意一种模式:逻辑OR电路128A(图2A),逻辑XOR电路128B(图2B),逻辑AND电路128C(图2C),或任何其他逻辑功能电路128D(图2D),以执行包括格雷编码(Gray encoding)、温度编码(temperature encoding)、加法运算(adding)等的不同操作功能。

为了提供PAM-4驱动器108的具体实现示例,图2A至图2C所示的逻辑OR、XOR和AND驱动器呈现于图3A至图3C的电路视图中;然而,本领域的技术人员将理解,图2A至图2C的概念图可以在除了图3A至图3C所示的示例之外的许多不同电路中实现。

此处的PAM-4AND驱动器108A至108C包括连接到外部多路复用器和缓冲器102(图1)的数字输入D1,

如图3A至图3C所示,第一差分对晶体管122A(M1,M2)连接到第一数字输入D1,

图3A至图3B中所示的OR和XOR实现108A,108B都是用分流电路114来控制性地将第一差分对晶体管122(M1,M2)连接到VDD。然而,在图3C所示的AND实现108C中,没有使用分流电路114,从而导致第一差分对晶体管122A(M1,M2)在AND实现108C中持续地连接到VDD。此外,在图3A至图3C所示的OR或XOR实现108A,108B中,晶体管M1的栅极连接至D1,且晶体管M2的栅极连接至

在图3A至图3C所示的OR或XOR实现108A,108B中,一个第二差分对晶体管122B(M3,M4)连接到第一数字输入D1,

更具体而言,图3A至图3B示出了在OR或XOR实现中108A,108B,晶体管M3和M4的栅极分别连接至D1,

图3A至图3C还示出了电压限制器124,126由晶体管M7,M8构成,其连接到数字输入D1,

更详细地说,在图3A所示的OR实现108A中,

因此,图3A至图3C所示,提供给电压限制器M7,M8的栅极的时钟CLK控制了电压(VDD)何时被提供给第二差分对晶体管122B(M3,M4),122C(M5,M6),且不同尺寸的电压限制器M7,M8导致了向第二差分对晶体管122B(M3,M4),122C(M5,M6)提供不同的电压。因此,此为第二差分对晶体管122B(M3,M4),122C(M5,M6)提供时钟,并向第二差分对晶体管122B(M3,M4),122C(M5,M6)提供不同的电压,以便提供类似模拟的步进输出。

输入M7和M8的尺寸不同于输入晶体管对M1,M2和M3,M4。钳位晶体管M7的尺寸可以与M8的尺寸相同或不同。输出端的PAM-4模拟阈值电平由M7和M8的强度设置。通过调节M7,M8的M/L比,可以彼此独立的选择阈值和电压电平。另外,M7和M8的VDD与M1和M2或M3,M4和M5,M6不级联。此外,在差分对M1,M2,M3,M4和M5,M6的漏极之间共享负载电阻R1和调谐电感L1。输入D1和D2具有相同的(平衡的)扇出(fan out)或寄生负载;从而使得输出端的上升时间和下降时间的变化最小化。

图3A至图3C进一步示出了所有晶体管的所有源极/漏极提供相同的电阻和电感(L1,R1),以确保平衡的电容负载。同样,图3A至图3C还示出了第一差分对晶体管122A(M1,M2)可以恒定的或可控制的(使用分流电路114)提供VDD,而第二差分对晶体管122B(M3,M4),122C(M5,M6)通过电压限制器M7,M8被提供不同于VDD的电压,这使得驱动器可以输出三组不同的高电压和低电压(总共六个电压步进),其被提供在所有六个差分对晶体管的源极/漏极共享的公共输出节点OUT,

另外,此导致了第二差分对晶体管122B,122C向模拟输出(Out)提供模拟信号,该模拟信号在数字高电压处、数字低电压处、以及数字高电压和数字低电压之间处于不同的电压步进。具体地,构成电压限制器124,126的晶体管的阈值电压确定第二差分对将输出的不同电压步进。

需注意的是,此处的时钟输入(CLK)仅连接到电压限制器124,126(其对第二差分对晶体管122B,122C进行时钟),而不连接到第一差分对晶体管122A(其保持无时钟)。另外,第一差分对晶体管122A和第二差分对晶体管122B,122C中的晶体管连接到公共节点并被提供相同的电流。此外,第一差分对晶体管122A和第二差分对晶体管122B,122C中的晶体管是尺寸相同和类型相同的晶体管。然而,第一差分对晶体管122A和第二差分对晶体管122B,122C中的晶体管的尺寸与电压限制器124,126的晶体管的尺寸不同,以帮助输出不同的电压步进。

此外,这些非限制性实施例表明可通过设置上述组件,并以电性节点连接将第一差分对晶体管122A和第二差分对晶体管122B,122C的源极/漏极连接至模拟输出(OUT,

此外,时钟控制的晶体管(M7和M8)引入存储效应。具体而言,此处介绍的PAM-4驱动电路包括输入级的差分对M1和M2,以及另外两个差分对M3,M4和M5,M6,其在差分对M3,M4和M5,M6的源极连接了额外的晶体管(电压限制器)M7和M8。在此,M3和M4充当第一存储器对,且M5和M6充当第二存储器对。通过调节钳位晶体管M7和M8的尺寸来设置存储器模拟电平。同样,M7和M8的尺寸可以相同,但与输入晶体管的尺寸不同。

因此,此示例性PAM-4驱动电路使用两个输入D1和D2。D1是无时钟无内存差分对M1,M2的输入,而D1和D2的组合是第二差分对M3,M4和第三差分对M5,M6的输入。M3,M4和M5,M6的源极被额外的晶体管M7和M8钳位。M3,M4和M5,M6的栅极处的差分数据相同以确保均衡的电容负载。同样,输入M7和M8共享相同的负载,因此,输入数据相同。

每个相应的附图除了在各个阶段说明书本实施例的方法和功能之外,还说明由一个或多个装置和结构全部实现或部分实现的方法的逻辑。这种装置和结构被配置成(即包括一个和多个组件,例如连接以使能执行步骤的电阻、电容器、晶体管等)实现上述的方法。换言之,可以创建一个或多个计算机硬件设备,其被配置成参考附图及其相应的描述来实现本文所述的方法和步骤。

本文中的实施例可用于各种电子应用中。由此产生的装置和结构,例如集成电路(IC)芯片,可以由制造者以原始晶圆形式(即,作为具有多个未封装芯片的单个晶圆)、裸芯片或封装形式进行分配。在后一种情况下,芯片安装在单个芯片封装中(例如塑料载体,其引线固定在主板或其他更高级别的载体上)或者安装在多芯片封装中(例如陶瓷载体,具有表面互连或埋置互连中的一种或两种)。在任何情况下,芯片然后与其他芯片、分立电路元件和/或其他信号处理设备集成,作为(a)中间产品(例如主板)或(b)最终产品的一部分。最终产品可以是包括集成电路芯片的任何产品,从玩具和其他低端应用到具有显示器、键盘或其他输入设备和中央处理器的高级计算机产品。

虽然仅结合有限数量的实施例详细描述了上述内容,但应容易理解,本文中的实施例不限于此类公开。相反,本文中的元件可以被修改为包括迄今为止未描述但与本文的精神和范围相称的任何数量的变化、改变、替换或等效安排。另外,虽然已经描述了各种实施例,但是应当理解,本文的各个方面可以仅由所描述的一些实施例包括。因此,所附权利要求不应被视为受到上述描述的限制。除非特别说明,否则对单数形式的元件的引用并不意味着“一个且仅一个”,而是“一个或多个”。本申请中所描述的各种实施例的所有结构和功能等价物,对于本领域的普通技术人员而言,都是已知的或以后知道的,通过引用明确地包含在本文中,并打算包含在本公开中。因此,应当理解,可以在所公开的特定实施例中进行改变,所公开的实施例在所附权利要求书概述的范围内。

- 使用级联差分晶体管对实现逻辑的光子发射器驱动器

- 容性平衡和自差分平衡级联的高速单光子探测系统