用于检测时变图像数据的单元阵列

文献发布时间:2023-06-19 09:57:26

技术领域

本发明涉及用于检测时变图像数据的光电阵列。

背景技术

这种光电阵列通常由像素阵列组成,每个像素阵列包含一个光电传感器(例如光电二极管)和一个像素编码电路。光电传感器产生与入射光强度相对应的模拟传感器信号。随后,该模拟信号被像素编码电路转换为数字信号,以下称为数字信号信息。

US 7,728,269 B2提出了这样的光电阵列,该光电阵列对由其光电传感器捕获的场景的时间视觉对比(temporal visual contrast)进行编码。通过这样做,几乎消除了光电阵列输出数据的时间冗余,从而以ON/OFF事件的格式生成活动驱动的稀疏数据。这意味着每个事件都由符号ON/OFF和像素坐标组成。然而,US 7,728,269 B2中描述的来自光电阵列的基于事件的输出仍然包含由噪声和空间冗余引起的,超出预期数量的数据,从而产生噪声事件和空间冗余事件。噪声事件和空间冗余事件都会削弱有意义的信息,尤其是当场景空间对比至关重要时。

可以通过单独的信号处理过滤掉噪声事件,该信号处理可以在单独的电路中实现,也可以通过在主机设备上运行的软件来实现。但是,有效的过滤仅在主机设备上以相当大的计算成本才能得以实现。此外,所有噪声事件仍然需要通过多路复用通信总线从光电阵列发送到主机设备,这就导致通信总线负担沉重。

为了减少主机计算机上过滤掉噪声事件的计算成本和传输噪声事件的通信负担,可以将基于关联的噪声事件过滤算法实现到可编程逻辑设备中,该可编程逻辑设备与光电阵列和主机设备都分开。在US 2016/0274643 A1中,提出了一种基于时空关联(spatio-temporal correlation)原理的噪声事件过滤器。在减轻主机设备及其通信总线的负担的同时,基于时空关联的噪声事件过滤器的这种硬件实现仍然需要在噪声事件被过滤掉之前,将所有事件从光电阵列传输到次级设备。因此,从光电阵列到次级设备的多路复用通信总线仍然承受噪声事件的负担。在极端情况下,即当通信总线不能在期望的时间帧内发送所有事件时,这会损害光电阵列本身的有效运行。而且,这种基于时空关联的噪声事件过滤算法也无法过滤掉空间冗余事件。

发明内容

本发明的目的是提出一种设备,所述设备能够滤除噪声事件并且滤除可能还发生在光电阵列上的空间冗余事件,同时减轻了主机读取光电阵列的负担,以及减轻了连接光电阵列与主机的通信总线的负担。

根据本发明,通过提供一种具有权利要求1的特征的光电阵列来实现该目的。本发明的其它有利的实施例是从属权利要求的主题。

根据本发明,光电阵列包括多个设备单元的阵列。每个设备单元包括一组像素和一个处理单元。每个像素包括光电传感器和像素编码电路。每个光电传感器(例如是光电二极管或光电晶体管)连续产生模拟传感器信号,该信号取决于照射在所述光电传感器上的光的光强度。为了获得用于进一步数字处理的数字信号,像素编码电路将由所述光电传感器生成的模拟传感器信号转换成数字像素信息。在下文中,该数字像素信息被识别为源自所述光电传感器的数字像素信息或像素信息。

光电传感器单元和随后的像素编码电路可以指定为生成像素信息的像素。因此,本发明的光电阵列实际上包括像素阵列,每个像素包括光电传感器和用于该光电传感器的像素编码电路,光电传感器和像素编码电路分组在一起,使得光电阵列同时包括设备单元阵列。作为示例,用于高清晰度应用的光电阵列可以包括1280x720像素(或光电传感器)。如果组的大小为4,则每个设备单元包含2x2像素(或光电传感器)的子阵列,则这将对应于所述光电阵列中640x360个设备单元(或处理单元)的阵列。

如上所述,由像素编码电路生成的像素信息可以被噪声事件和/或空间冗余事件叠加。当像素中的晶体管热噪声和结漏导致转换的内部电信号(对应于光电传感器处入射光的时间强度变化)超过像素编码电路的ON/OFF事件检测阈值时,可能会发生噪声事件。当通过光电阵列或整个场景检测到的场景中的某些区域均匀地变亮或变暗时,例如,当场景或整个场景的一部分被增加或减少的光照亮时,可能会发生空间冗余事件。

噪声事件和空间冗余事件均会削弱有意义的信息,尤其是当场景空间对比至关重要时。此外,过多的噪声事件和空间冗余事件给像素阵列和主机之间的通信总线增加了不必要的负担,这在极端情况下可能会损害像素阵列的有效运行,例如,当通信总线无法在期望的时间帧内传输所有事件时。

本发明基于这样的想法:通过关联源于一组光电传感器的像素信息,来滤除像素信息中的噪声事件以及可能的空间冗余事件。可以对来自该组的两个或更多个光电传感器的信息,甚至可能包含来自该组的所有光电传感器的信息执行关联处理或功能。一组继而可以包括至少两个光电传感器,有利地是包括两个以上的光电传感器,例如设置在2x2光电传感器的子阵列中的4个光电传感器,或设置在4x4光电传感器的子阵列中的16个光电传感器。

为了执行此关联,每个设备单元都包含一个处理单元,该处理单元又包括关联逻辑,该关联逻辑配置为关联使来自所述光电传感器组的光电传感器的所述像素信息,并作为结果产生指示所述单元包含要读取的像素信息的请求信号。可替代地或累积地,由于该关联可以产生直通信号,所述直通信号指示包含在所述单元中的像素信息被允许发送到,例如主机、次级处理单元或其它处理设备。通过正确地配置关联逻辑,即使有可能来自相应的一个或多个光电传感器的像素信息,也可以通过保留这样的请求和/或直通信号来忽略与噪声和/或空间冗余关联的像素信息。换句话说,仅当通过该关联确定像素信息不是噪声或空间冗余信息时,关联逻辑才会产生请求信号和/或直通信号,从而指示该设备单元包含要读取的像素信息,即,指示可以和/或应该读取该设备单元中的组的一些或全部像素。在这种情况下,将相应的像素信息从光电阵列传输到主机设备以进行进一步处理。

在发送任何像素信息之前,所述信息过滤或事件过滤在像素阵列中以像素并行方式(例如,通过多路复用通信总线)执行,从而使总线和光电阵列上的通信负载最小化。有利的是,有意义的事件(即,非噪声和/或非空间冗余像素信息)被成组发送,而不是单独发送,因此增加了通信总线的吞吐量。

为了滤除噪声事件,关联逻辑利用噪声和非噪声事件之间的时空关联差异。噪声事件在空间和时间上都是随机发生的,因此在时空上是不关联的。非噪声事件是指由真实场景视觉刺激引起的事件,这通常与时空关联(即,非噪声事件通常在相对相同的时间彼此相邻出现)。因此,关联逻辑滤除时空不关联的事件,并且仅传递时空关联的事件以进行后续处理。

此外,空间冗余事件通常是时空关联性极高的。例如,如果整个场景的照明突然增加,则事件将同时在整个光电阵列的每个像素中发生。这些事件在空间上是多余的,并且不传达任何空间对比信息。因此,关联逻辑过滤掉时空关联性极高的事件,并且仅将时空关联性适中的事件传递以用于后续处理。

在有利的实施例中,所述光电传感器组中的两个或多个光电传感器彼此相邻设置。换句话说,两个或多个光电传感器实际上是在光电阵列内部在空间上分组到一起。所述组中的所有光电传感器也可能在空间上分组到一起。在两种情况下,通过使一组光电传感器在空间上散置在第二组光电传感器中,两个组可以在空间上,特别是在组的边缘处重叠。在简化的一维(1D)示例中,如果有两个光电传感器组A和B,每个组都有4个光电传感器,则可以将光电传感器设置为AABABABB,其中每个字母表示光电传感器所属的组。

在一些实施例中,如果重复利用光电传感器可能是有利的。光电传感器因此可以将其输出发送到多个组。换句话说,同一光电传感器则属于多个不同的组。因此,在前面简化的一维示例中,可以用少于8个光电传感器来组成2组,所述光电传感器排列为AA(A&B)(A&B)BB,其中(A&B)表示光电传感器将其输出发送到A组和B组。光电传感器的散置或共享越多,输出将在空间上越连续,但是,光电阵列内的布线/连接会变得更为复杂。

根据一个优选实施例,多个设备单元被分成多组单元,特别是设置成具有单元行和单元列的单元矩阵。每组单元进一步包括放置在所述单元组的末端,特别是在单元列的末端的次级处理单元。每个次级处理单元包括次级关联逻辑,所述次级关联逻辑配置为关联来自所述单元的所选单元的所述光电传感器组的光电传感器的所述像素信息,并作为结果产生指示所述所选单元包含要读取的像素信息的请求信号。换句话说,多个处理单元共享单个次级处理单元。在这种情况下,处理单元可以称为主要处理单元,因为像素信息在被中继到次级处理单元之前首先进入它们。

次级处理单元的次级关联逻辑有利地一次关联一个单元。因为整个矩阵的读取可以通过扫描逐行进行,每次选中要读取的行时,在列的末端的次级处理单元都会实行单个单元的二次过滤。因此,来自次级处理单元的请求信号指示该列的特定单元,并且当前所选的行包含经过两级过滤的信息,即主要处理单元中由关联逻辑进行的第一次过滤和次级处理单元中由次级关联逻辑进行的第二次过滤。

可替代地或者除了请求信号之外,可以生成至少一个直通信号,其在次级处理单元中用以允许发送包含在所述所选单元中的像素信息。有利的是,次级关联逻辑可以产生两个直通信号,这样不仅指示可以发送像素信息,而且指示可以发送哪种像素信息。例如,来自单个像素的像素信息可以具有ON值、OFF值或中性值。ON值表示像素已检测到其入射光提高了预定阈值,OFF值表示像素已检测到其入射光降低了预定阈值,以及中性值表示像素检测到的入射光没有变化(超过预定阈值)。在这种情况下,可以有一个直通(ON)信号,它表示来自像素的组的ON值是有意义的(无噪声和/或非空间冗余),和一个直通(OFF)信号,它表示像素的组的OFF值有意义。

在该实施例中,可以通过更简单的方式来实现主要处理单元的关联逻辑,例如,仅将其配置为以极性盲(polarity-blind)的方式关联所有事件,而处理单元可以通过更复杂的方式实现,例如,将其配置为分别关联ON事件和OFF事件,即根据极性将事件分离。ON事件表示像素处的入射光强度增加超过开启阈值,而OFF事件则相反,表示像素处的入射光强度减小超过关闭阈值。像素信息有利地包含两个位,即ON信号和OFF信号。ON=1,OFF=0表示ON事件,而ON=0,OFF=1表示OFF事件,ON=0,OFF=0表示无事件。特别地,ON和OFF不应均等于1。因此,通过像素信息对ON/OFF事件进行编码,该ON/OFF事件指示入射光的时间变化。

可以以矩阵方式排列多组单元。在该矩阵中,一组单元可以包括设置在一列中的X个单元,使得在该列的末端,放置用于该单元列的对应的次级处理单元。因此,整个光电阵列被分成子阵列或子单元,每个子阵列或子单元具有一个主处理单元,而列单元又具有一个次级处理单元。当相应的单元包含一个或多个要读取的事件时,每个单独的主要处理单元都可以生成行请求信号,以及允许读取相应的单元中的事件的内部直通信号,并且从主机接收行选择信号作为读取的指示。每个次级处理单元都可以产生列请求信号,以及两个内部直通信号(直通(ON)信号和直通(OFF)信号),并且接收列选择信号。

优选地,所述关联逻辑和/或所述次级关联逻辑由组合逻辑实现。这尤其意味着,该实现是通过布尔(Boolean)电路完成的,并且相应逻辑的输出是在任何给定时间的当前输入的纯函数。换句话说,关联逻辑和/或次级关联逻辑不包含用于存储像素信息的存储或记忆元件。

优选地,所述关联逻辑和/或所述次级关联逻辑实现为时空关联逻辑。在简化的实施例中,关联逻辑和/或所述次级关联逻辑实现为空间关联逻辑。具体地,当所述像素信息的关联结果等于或大于最小阈值数(N)和/或小于或等于最大阈值数(M)时,这样的关联逻辑和/或次级关联逻辑可以配置为产生请求信号和/或直通信号。具体地,这可以意味着像素的组中的事件数量(即,在报告事件的组中的像素数量)等于或大于N和/或等于或小于M。

在光电阵列的有利实施例中,每个像素的像素信息在被关联逻辑读取之前被存储。为此,所述处理单元包括用于所述光电传感器组中的每个光电传感器的事件存储存储器,其配置为存储来自所述光电传感器的所述像素信息。这样,整个光电阵列的每个光电传感器都有一个对应的事件存储存储器。优选地,所述次级处理单元包括用于所述光电传感器组中的每个光电传感器的次级事件存储存储器,其配置为存储来自所述光电传感器的所述像素信息。换句话说,次级事件存储存储器的大小等于第一事件存储存储器的大小。因为每组设备单元有利地具有一个单独的次级处理单元,所以整个光电阵列可以具有与组中的像素数乘以设备单元组数一样多的次级事件存储存储器。

来自像素的组的所有事件以同步的方式(即,同时)被读入相应设备单元的相应事件存储存储器中。对于将像素信息读取到次级处理单元的次级存储存储器中也是如此。换句话说,在同步的采样信号的相同采样间隔期间,占满了处理单元或次级处理单元的整个事件存储存储器。因此,存储在每个处理单元,即每个组中的事件已经被临时关联。因此,为了用作时空关联逻辑,随后的关联逻辑仅执行空间关联就足够了。因此,同样适用于次级处理单元和次级关联逻辑。

有利的是,所述处理单元具有用于该组中的每个光电传感器的存储存储器,并且所述次级处理单元具有用于所述组中的每个光电传感器的次级存储存储器。在该实施例中,次级存储存储器可以配置为从所述存储存储器接收所述像素信息。换句话说,像素信息首先被读入初级处理单元中的存储存储器中,然后被读入次级处理单元中的次级存储存储器中。

优选地,如果所述处理单元的内部直通信号为真,则所述处理单元配置为接收选择信号,并且响应于所述选择信号以并行方式发送所述单元包含的要被读取的所有像素信息。具体地,当处理单元包含事件存储存储器时,在事件存储存储器存储了像素信息,并且如果所述处理单元的内部直通信号为真,如果可以的话,则选择信号可以启动事件存储存储器到通信总线或次级处理单元(如果可用)的读出。附加地或可替代地,如果所述次级处理单元的内部直通信号为真,则所述次级处理单元可以配置为接收选择信号,并且响应于所述选择信号以并行方式发送所述单元包含的要被读取的所有像素信息。与处理单元类似,次级处理单元可以包含次级事件存储存储器,例如从所述处理单元的事件存储存储器中读取像素信息之后,在次级事件存储存储器中存储像素信息。在这种情况下,如果所述次级处理单元的内部直通信号为真,则选择信号可以启动次级事件存储存储器到通信总线的读出。

如前所述,像素编码电路将由光电传感器生成的模拟传感器信号转换为数字像素信息或事件信息。根据优选实施例,像素编码电路是变化检测电路。在这种情况下,由像素编码电路生成的数字像素信息指示由光电传感器生成的传感器信号的变化。这可以通过阈值的比较来实现。例如,每次模拟传感器信号上升或下降量等于或大于给定阈值时,像素信息可以相应地包括ON信号或OFF信号。为此,每个像素的像素信息可以包括用于区分变化的极性的两位(two-bit)信息,并且在不发生变化的情况下还允许中性信号。

具体地,变化检测电路可以是使用差分脉冲编码调制(DPCM)编码方案的模数转换器,这是一种将模拟信号编码为脉冲流的方案,其中每个脉冲代表模拟信号固定量的变化。这种变化检测电路,例如在上文背景技术中所描述的US 7,728,269 B2中进行了描述。

附图说明

在下面的描述中,将参考所附示意图更详细地解释本发明的实施例的一些示例,其中:

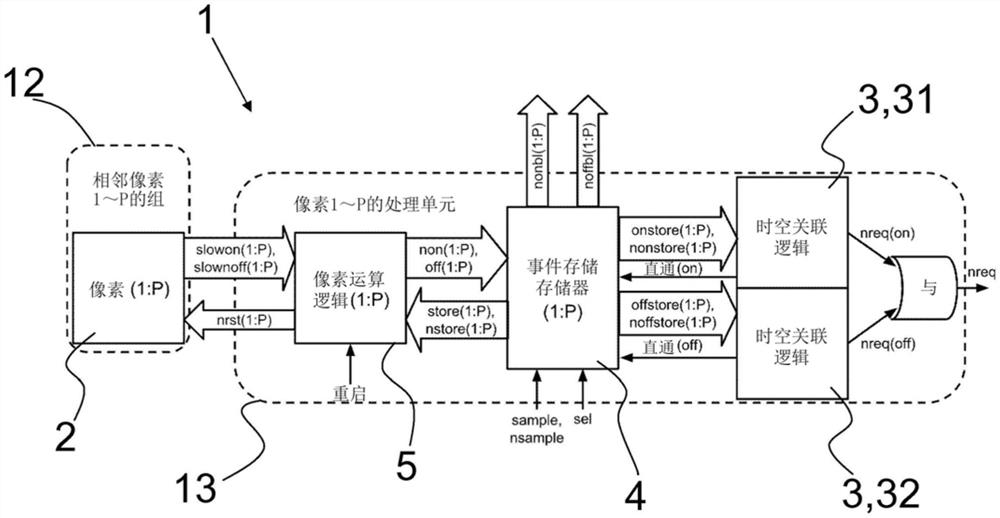

图1示出了根据一个有利实施例的具有像素组和处理单元的设备单元的架构示意图;

图2示出了根据另一有利实施例的具有像素组、处理单元和次级处理单元的设备单元的架构示意图;

图3示出了根据又一有利实施例的以矩阵方式设置的多组设备单元的示意图,在设备单元的每一列的末端具有次级处理单元;

图4示出了根据现有技术的像素的示意图;

图5示出了根据一个优选实施例的在处理单元中使用的像素运算逻辑的示意图;

图6示出了根据一个优选实施例的在处理单元中使用的事件存储存储器的示意图;

图7示出了根据一个优选实施例的处理单元中的关联逻辑的一般形式的示意图;以及

图8示出了图7的关联逻辑的特定形式的示意图。

具体实施方式

图1示出了根据光电阵列的一个有利实施例的设备单元1的示意图,设备单元1包括P个相邻像素2的组和用于该组像素2的处理单元13。每个像素2包括光电传感器和像素编码电路(两者均未在图1中单独示出)。设备单元1的所有组的处理单元13形成2D阵列,该2D阵列被并入光电传感器和光电阵列的像素2的2D阵列中。

每个处理单元由三部分组成:像素运算逻辑5、事件存储存储器4和时空关联逻辑3。每个像素2在处理单元13中具有对应的像素运算逻辑5和事件存储存储器4。相邻像素2的组共享相同的时空关联逻辑3。

应当注意,在输出或输入标识符之前的n通常表示对相应的输入、输出或信号取反。因此,尽管rst可以是复位信号,但是nrst可以是逻辑反相的复位信号。

像素2的组将其输出slowon(1:P)和slownoff(1:P)发送到其相应的像素运算逻辑5,并从其相应的像素运算逻辑5接收nrst(1:P)。像素运算逻辑5由全局信号重启(restart)控制,并将其输出non(1:P)和off(1:P)发送到其相应的事件存储存储器4,同时从事件存储存储器4将信号store(1:P)和nstore(1:P)接收回来。事件存储存储器4由全局信号sample/nsample和行/列信号sel控制。事件存储存储器4将其输出onstore(1:P)和offstore(1:P)发送到两个相应的时空关联逻辑31、32,所述时空关联逻辑31、32将信号直通(on)和直通(off)发送回事件存储存储器4以允许读出。当第一时空关联逻辑31关联从事件存储存储器4接收的所有on事件以产生信号nreq(on)时,第二时空关联逻辑32关联所有off事件以产生信号nreq(off)。信号nreq(on)和nreq(off)一起确定最终输出信号nreq,从而请求读出通信总线对其相应行的访问。如果直通(on)和直通(off)为真,则一旦行选择信号sel选择了相应的行,就可以通过位线信号nonbl(1:P)和noffbl(1:P)来读取事件存储存储器。

相同的时空关联逻辑31、32电路可同时服务于图1所示的on事件和off事件信号onstore(1:P)和offstore(1:P)。然而,每个处理单元13具有两个占据相当大的硅面积的时空关联逻辑电路31、32。因此,图2示出了根据另一有利实施例的具有替代处理单元和次级处理单元的设备单元的替代架构。

在该替代架构中,每个主要处理单元只有一个时空关联逻辑3。一列这样的处理单元13(以下称为主要处理单元)在列的末端共享次级处理单元8。次级处理单元8包括一组次级事件存储存储器6和另外两个时空关联逻辑电路81、82。为了容纳来自P个像素2的组12的所有像素信息,次级事件存储存储器6具有与事件存储存储器4相同的大小。

主要处理单元中的时空关联逻辑3以信号store(1:P)和nstore(1:P)作为输入,并产生信号传递使得信号从事件存储存储器中读出,并且信号nreq(行)请求读出通信总线对其相应行的访问。因此,它不能区分ON和OFF事件。可以说是极性盲的。当通过行信号sel(行)选择该行主要处理单元13时,如果直通为真,则事件存储存储器4通过位线信号nonbl1(1:P)和noffbl1(1:P)读入列的末端的次级事件存储存储器6,该次级时间存储存储器6进一步馈入次级时空关联逻辑81、82。换句话说,次要事件存储器6接收从sel(行)信号导出的采样信号。因此,每次选择主要处理单元的行时,次级事件存储存储器6从所选行中的主要处理单元13的事件存储储存器4中采样像素信息。包括两个电路并由该列共享的次级时空关联逻辑81、82对符号事件(signed events)进行进一步过滤,并且产生信号直通(on)和直通(off)返回到次级事件存储存储器6使得信号读出,并且产生信号nreq(列)以请求读出通信总线对其相应列的访问。

当通过列信号sel(列)选择其相应的列时,如果直通(on)和直通(off)为真,则通过位线信号nonbl2(1:P)和noffbl2(1:P)读出存储在次级事件存储器6中的事件。图2所示的替代架构降低了主要处理单元13的阵列的复杂度,但是代价是可能存在不完全的和/或不正确的事件过滤。因为事件在主要处理单元13的阵列中被处理为无符号,所以不同符号的噪声事件可能会被错误地视为时空关联事件并被允许继续传递;并且,具有不同符号的有意义事件可能会被错误地视为空间冗余事件并被过滤掉。但是,就减少多路复用总线nonbl1(1:P)和noffbl1(1:P)的通信量负担而言,对噪声事件进行不完全过滤仍然是对完全不过滤的一种改进。此外,主要处理单元13中的时空关联逻辑3可以配置为不过滤掉空间冗余事件,如后面所述的,从而防止错误地过滤掉有意义的事件。

应当注意,关联逻辑3和次级关联逻辑81、82产生请求信号和直通信号。直通信号是每个关联逻辑3、81、82的即时输出,并且意在控制其相应的事件存储存储器4、6。所述请求信号是一个或多个处理单元13、8的输出(取自其直通信号),并且用于请求总线访问时间。

作为第一示例,处理单元的行可以共享单个行请求信号。只要该行中的至少一个处理单元13在内部具有直通=1,即行请求=或(该行中的所有单独直通信号),则共享行请求信号将为1。并且,选择该行的情况下,它是单独的内部直通信号,所述内部直通信号确定哪个处理单元13可以将其信息发送出去。仅当其request=1时才能选择行。

作为第二示例,次级处理单元8可以包含两个极性敏感的关联逻辑电路81和82,因此在内部包含直通(ON)信号和直通(OFF)信号。次级处理单元8的输出是列请求信号。当直通(ON)=1或直通(OFF)=1时,列请求将为1。并且,选择该二次处理单元8时,其内部的直通(ON)和直通(OFF)信号确定是否读取ON或OFF的信息。仅当次级处理单元8的列请求=1时,才可以选择次级处理单元8。

图3用来更好地说明根据上文所述的以及图2所示的实施例的光电阵列的架构。图3示出了以矩阵方式设置设备单元的多个组71、72、73的示意图,在设备单元的每一列的末端具有次级处理单元81、82、83。光电阵列包括以行和列设置的主要处理单元13的矩阵或阵列。在图3中,示出了3×3的主要处理单元13的阵列。为了清楚起见,在图3中省略了每个设备单元的像素组12,或者可以将其视为图3所示的每个主要处理单元13的一部分。

设备单元的每个组7设置为设备单元的列,在其末端设置了次级处理单元8。例如,在设备单元的第一组71的末端或主要处理单元13的末端,设置了第一次级处理单元81等。每个主要处理单元13的关联逻辑3生成行请求信号nreq(r1)、nreq(r2)、nreq(r3)以表示设备单元的相应行具有要发送的信息,即行1、行2和/或行3。另一方面,如果设备单元的某一列的所选单元,即所述所选设备单元中的任何像素具有要发送的信息,则相应的次级处理单元8将生成列请求信号nreq(c1)、nreq(c2)、nreq(c3)。例如,当通过信号sel(r2)选择第二行时,则具有行2和列2的单元是第二次级处理单元82的所选单元。如果该所选单元包含具有要发送的信息的像素,则第二次级处理单元82将生成相应的列请求信号nreq(c2)。

因此,次级处理单元在逐行扫描读出期间执行第二级过滤。如果行1和行3具有信息,当行1被选择时,则整个行1的信息进入次级处理单元81、82、83。即,将来自行1,列1的信息读入第一次级处理单元81,将来自行1,列2的信息读入第二次级处理单元82,以及将来自行1,列3的信息读入第三次级处理单元83。然后,次级处理单元81、82、83进一步确定哪一列实际上具有信息。例如,在基于极性的二次过滤之后,只有第1行第2列可能包含信息,或者第1行中的所有单元都不会有信息。在读取行1之后,可以选择行3,然后次级处理单元81、82、83处理来自行3的信息。

图4示出了属于现有技术的像素电路的示意图,其在US 7,728,269 B2中进行了描述。它包含一个作为光电传感器的光电二极管D,以及一个像素编码电路,该电路产生输出slowon和slownoff。

图5示出了根据一个优选实施例的像素运算逻辑的示意图.像素运算逻辑5控制感测像素的时间/时空视觉对比的运行。当像素检测到其内部转换的电信号的变化(其对应于入射光感应的光电流的对数值)超过预定的ON/OFF事件阈值时,像素运行逻辑5保持检测到的事件处于复位状态并将像素置为复位状态。

像素运算逻辑5可以进一步分为3个子电路,每个子电路在图5中以虚线框表示:事件保持器、复位逻辑和重启逻辑。当像素产生ON或OFF信号,slowon=1或slownoff=0时,事件保持器将锁存为on=1或off=1的状态,仅保留一个符号事件(假设fb=1和nfb=0)。同时,复位逻辑将设置复位信号rst=1和nrst=0(假设fb=1),从而将像素置于复位状态。像素将保持复位状态,直到接收到全局脉冲信号重启为止。当重启=1时,重启逻辑设置fb=0和nfb=1(假设store=1和nstore=0),这进一步无效了事件保持器中的正反馈机制,并设置rst=0和nrst=1。当重启返回0时,重启逻辑设置fb=1和nfb=0(假设store=1和nstore=0),这将再次使能事件保持器和复位逻辑。因此,处于复位状态的像素可以恢复到对比检测状态的时刻由全局脉冲信号重启确定。信号store和nstore来自事件存储存储器4。

图6示出了根据优选实施例的事件存储存储器4和/或次级事件存储存储器6的示意图。像素运算逻辑5可以将检测到的事件写入事件存储存储器4、6的时刻由全局信号sample和nsample(nsample是来自sample的反相信号)确定。

在sample脉冲之后,如果事件存储存储器存储了一个ON/OFF事件,即store=1和nstore=0,则像素运算逻辑中的重启逻辑将在重启脉冲之后将像素从复位状态恢复为对比检测状态。如果像素未检测到任何事件,则事件存储存储器没有存储事件。在sample脉冲,即store=0和nstore=1之后,像素运算逻辑中的重启逻辑将忽略重启信号,并且使像素保持在对比检测状态。如果像素仅在sample脉冲之后但在重启脉冲之前检测到ON/OFF事件,即使像素运算逻辑5已将像素置于复位状态,它仍将忽略重启信号,并且所述像素将保持在复位状态,因为像素运算逻辑5仍保留检测到的事件并且无法写入事件存储存储器(store=0和nstore=1)。

当sel=1和直通=1时,通过两条位线nonbl和noffbl读取事件存储存储器。信号sel是行/列选择信号。信号直通来自时空关联逻辑3、8、81、82。

时空关联逻辑3、8、81、82读取其组中所有像素的事件存储存储器4、6,并且在每个sample脉冲之后确定应将存储在该组中的事件传递到读出通信总线还是将其过滤掉。

全局同步sample信号意味着在每个sample脉冲之后存储在每个组中的事件已经在时间上关联,因为它们出现在同一采样间隔内。因此,通过近似于设备单元的事件存储存储器4、6中所存储的事件的数量,时空关联逻辑3、8、81、82还仅基于它们的空间关联性来确定所存储的事件是否能够通过。可以将决策标准设置为两个可选条件的组合:

1.如果存储在设备单元中的事件少于最小阈值数N,则将这些事件视为噪声事件并过滤掉。在此,N大于1且小于设备单元中的像素P总数。(第一可选条件)

2.如果在设备单元中存储的事件超过最大阈值数M,则将这些事件视为空间冗余事件并过滤掉。在此,M大于N并且小于设备单元中的像素P总数。(第二可选条件)

如果时空关联逻辑3、8、81、82配置为执行两个可选条件,则仅当组中存储的事件数在N和M之间(包括N和M)时,才会通过存储的事件。如果时空关联逻辑3、8、81、82配置为不执行两个可选条件中的任何一个,则只要组中至少有一个存储的事件,它将通过任何存储的事件。如果只执行了第一可选条件,只要设备单元中至少有N个存储的事件,则时空关联逻辑3、8、81、82将通过任何存储的事件。如果只执行了第二可选条件,只要设备单元中存储的事件不超过M个,则时空关联逻辑3、8、81、82将通过任何存储的事件。如图1和图2所示,相同的时空关联逻辑3、8、81、82可用于处理ON事件(onstore(1:P)和nonstore(1:P)),OFF事件(offstore(1:P)和noffstore(1:P))或无符号的事件(store(1:P)和nstore(1:P))。

时空关联逻辑3、8、81、82由组合逻辑实现。图7示出了根据优选实施例的时空关联逻辑电路3、8、81、82的一般形式。s[i]和ns[i]表示在设备单元中是否存在来自每个像素i(i∈[1,P])存储事件(符号的或无符号的)。s[i]=1和ns[i]=0都表示在像素i中存在存储的事件。alN(至少N)是使能/无效第一可选条件的信号。amM(至多为M)是使能/无效第二可选条件的信号。直通是时空关联逻辑3、8、81、82的输出信号,该时空关联逻辑确定是否应发出存储在组中的事件。nreq是用于访问读出的通信总线的请求信号。

如果alN=1,则使能第一可选条件。第一可选条件是通过上拉电路和下拉电路实现的。上拉电路由C(P,N)(P的N种组合)个支路组成,其中每个支路由ns[i]控制的N个串联的p型晶体管组成。每个上拉支路代表具有ns[i]=0的N个像素的唯一组合。因此,当至少N个像素具有ns[i]=0(即,已经存储了事件)时,上拉电路能够设置直通=1。下拉电路由C(P,P-N+1)(P的P-N+1种组合)个支路组成,其中每个支路由ns[i]控制的P-N+1个n型晶体管组成。每个下拉支路代表具有ns[i]=1的P-N+1个像素的唯一组合。因此,当至少P-N+1个像素具有ns[i]=1,即没有存储事件时,换句话说,当少于N个像素有存储事件时,下拉电路会设置直通=0。

如果amM=1,则使能第二可选条件。第二可选条件也是通过上拉电路和下拉电路实现的。上拉电路由C(P,P-M)(P的P-M种组合)个支路组成,其中每个支路由s[i]控制的P-M个串联的p型晶体管组成。每个上拉支路代表具有s[i]=0的P-M个像素的唯一组合。因此,当至少P-M个像素具有s[i]=0,即,没有存储事件时,换句话说,当至多M个像素有存储事件时,上拉电路能够设置直通=1。下拉电路由C(P,M+1)(P的M+1种组合)个支路组成,其中每个支路由s[i]控制的M+1个n型晶体管组成。每个下拉支路代表具有s[i]=1的M+1个像素的唯一组合。因此,当至少M+1个像素具有s[i]=1,即存储了事件时,换句话说,当至多M个像素有存储事件时,下拉电路会设置直通=0。

如果alN=1和amM=1,则使能第一和第二可选条件。两个条件的两个上拉电路是串联的,而两个条件的两个下拉电路是并联的。

如果alN=0和amM=0,则两个可选条件均被无效。整个时空关联逻辑都简化为P输入或门。

图8示出了根据图7中总体示出的实施例的时空关联逻辑的具体示例的示意图,其中N=2,M=3,P=4。这两个配置位分别为al2(至少2)和am3(至多3)。

附图标记

1 设备单元

12 像素的组

13 (主要)处理单元

2 像素

3 关联逻辑

4 存储储存器

5 像素运算逻辑

6 次级存储储存器

7 单元的组

8 次级关联逻辑

- 用于检测时变图像数据的单元阵列

- 特别用于将时变图像数据的取样亮度感测和异步检测相结合的光电阵列