接口转换电路、芯片、芯片测试系统及方法

文献发布时间:2023-06-19 11:32:36

技术领域

本发明实施例涉及芯片测试技术领域,尤其涉及一种接口转换电路、芯片、芯片测试系统及方法。

背景技术

为了确保芯片能正常工作,在芯片制造过程中和制造完成后,必须对芯片进行严格的测试。通常,芯片测试要通过联合测试工作组(Joint Test Action Group,JTAG)测试引脚进行,标准JTAG协议的测试方法,是在测试数据输入端口向芯片灌入测试向量,然后在测试数据输出端口获取芯片的响应信号,以此来检测芯片的功能是否正常。芯片内部的测试电路负责接收并执行外部测试系统发送来的测试向量,然后将结果向量反馈给外部的芯片测试系统。随着计算需求的高度发展,软件对运算算力的要求越来越高,导致芯片规模越来越大,测试向量越来越复杂,使得芯片测试所需的时间越来越长。因此,现有的芯片测试方法存在灵活性差、效率低的问题。

发明内容

本发明实施例提供了一种接口转换电路、芯片、芯片测试系统及方法,以提高芯片测试的灵活性和效率。

第一方面,本发明实施例提供了一种接口转换电路,置于芯片内部,用于芯片测试,所述接口转换电路包括:

解码模块,所述解码模块的输入端用于与外部的主控设备连接;所述解码模块用于根据所述主控设备发出的测试向量得到测试指令和原始测试数据;其中,所述测试向量与所述接口转换电路匹配;

控制模块,所述控制模块的输入端与所述解码模块的第一输出端连接;所述控制模块包括压缩判断单元,所述压缩判断单元用于根据所述测试指令判断所述原始测试数据是否经过压缩,并将判断结果输出;

数据模块,所述数据模块的第一输入端与所述解码模块的第二输出端连接,所述数据模块的第二输入端与所述控制模块的输出端连接;所述数据模块用于根据所述判断结果输出测试数据;其中,所述测试数据包括写入数据和期待响应数据;

写入模块,所述写入模块的输入端与所述数据模块的第一输出端连接,所述写入模块的输出端与所述芯片的测试访问端口的输入端连接,以将所述写入数据输出至所述芯片;

读取模块,所述读取模块的输入端与所述芯片的测试访问端口的输出端连接;所述读取模块用于采集所述芯片反馈的读取数据;

比较输出模块,所述比较输出模块的第一输入端与所述数据模块的第二输出端连接,所述比较输出模块的第二输入端与所述读取模块的输出端连接;所述比较输出模块用于根据所述读取数据和所述期待响应数据,得到错误信号并通过输出端输出。

可选地,所述测试数据还包括掩码数据;

所述比较输出模块包括:与单元、异或单元和错误寄存器;

所述与单元的第一输入端与所述数据模块的第三输出端连接;所述与单元的第二输入端与所述读取模块的输出端连接;所述与单元用于根据所述掩码数据和所述读取数据得到实际关心数据,并过滤不关心数据;

所述异或单元的第一输入端与所述数据模块的第二输出端连接;所述异或单元的第二输入端与所述与单元的输出端连接;所述异或单元用于根据所述实际关心数据和所述期待响应数据得到比较结果;

所述错误寄存器的第一输入端与所述异或单元的输出端连接,所述错误寄存器的第一输出端为所述比较输出模块的输出端;所述错误寄存器用于根据所述比较结果得到所述错误信号,以及存储并输出所述错误信号。

可选地,所述解码模块内配置有指令集,所述解码模块依据所述指令集的规则解码所述测试向量,得到所述测试指令和所述原始测试数据。

可选地,所述指令集中的指令包括赋值指令;所述赋值指令包括全0指令或全1指令。

可选地,所述测试指令包括循环指令,所述控制模块还包括顺序控制单元;所述顺序控制单元分别与所述解码模块、所述写入模块和所述读取模块连接;所述顺序控制单元用于根据所述循环指令控制测试顺序。

可选地,所述控制模块还包括使能控制单元;所述使能控制单元与所述写入模块和所述读取模块连接,用于控制测试开始或结束。

可选地,所述控制模块还包括模式控制单元;所述接口转换电路还包括:数据选择模块;

所述数据选择模块分别与所述比较输出模块和所述读取模块连接;所述数据选择模块输出测试结果;所述测试结果包括所述错误信号或所述读取数据;

所述模式控制单元与所述数据选择模块连接,用于选择所述数据选择模块输出的所述测试结果为所述错误信号或所述读取数据。

第二方面,本发明实施例还提供了一种芯片,包括:如本发明任意实施例所提供的接口转换电路。

第三方面,本发明实施例还提供了一种芯片测试系统,包括:主控设备、软件模块和如本发明任意实施例所提供的芯片;

所述软件模块用于处理原始标准测试向量,以得到与所述芯片中的接口转换电路相匹配的测试向量并输出;

所述主控设备包括输入端和输出端;所述主控设备的输入端与所述软件模块连接,所述主控设备的输出端与所述芯片连接;所述主控设备用于将所述软件模块发送的测试向量传送给所述芯片。

第四方面,本发明实施例还提供了一种如本发明任意实施例所提供的芯片的芯片测试方法,包括:

主控设备将与所述芯片中的接口转换电路相匹配的测试向量传送给所述芯片中的接口转换电路;

解码模块接收所述测试向量,并根据所述测试向量得到测试指令和原始测试数据;

控制模块接收所述测试指令,根据所述测试指令判断所述原始测试数据是否经过压缩,并将判断结果输出;

数据模块接收所述判断结果,根据所述判断结果输出测试数据;其中,所述测试数据包括写入数据和期待响应数据;

写入模块将所述写入数据通过测试访问端口传输给所述芯片;

读取模块通过所述测试访问端口采集所述芯片反馈的读取数据;

比较输出模块根据所述读取数据和所述期待响应数据得到错误信号并输出。

本发明实施例提供的接口转换电路,设置有解码模块、控制模块和数据模块。通过解码模块解码测试向量得到测试指令和原始测试数据;其中,测试指令指示了该测试向量中解码出的原始测试数据是否经过了压缩,还可以指示压缩方式。控制模块根据测试指令动态控制数据模块的解压缩功能打开或关闭;当控制模块中的压缩判断单元根据测试指令判断出原始测试数据已压缩时,数据模块解压原始测试数据,得到测试数据。这样,在转换接口内部实现了硬件的解压缩结构,可以有效减少数据传输过程,提高测试效率。并且,写入模块和读取模块的设置,使得写入数据可以直接灌入测试访问端口,并且读取数据可以直接从测试访问端口提取。也就是说,该接口转换电路使芯片测试可以脱离JTAG测试引脚进行,提高了芯片测试的灵活性。以及,接口转换电路中设置有比较输出模块,可以在芯片内部进行读取数据和期待响应数据的比较,测试系统直接获取比较输出模块输出的错误信号便可得知芯片是否正常,并不需要输出所有读取数据在芯片外部进行处理,从而减少数据传输,提高了测试效率。因此,与现有技术相比,本发明实施例可以提高芯片测试的灵活性和效率。

附图说明

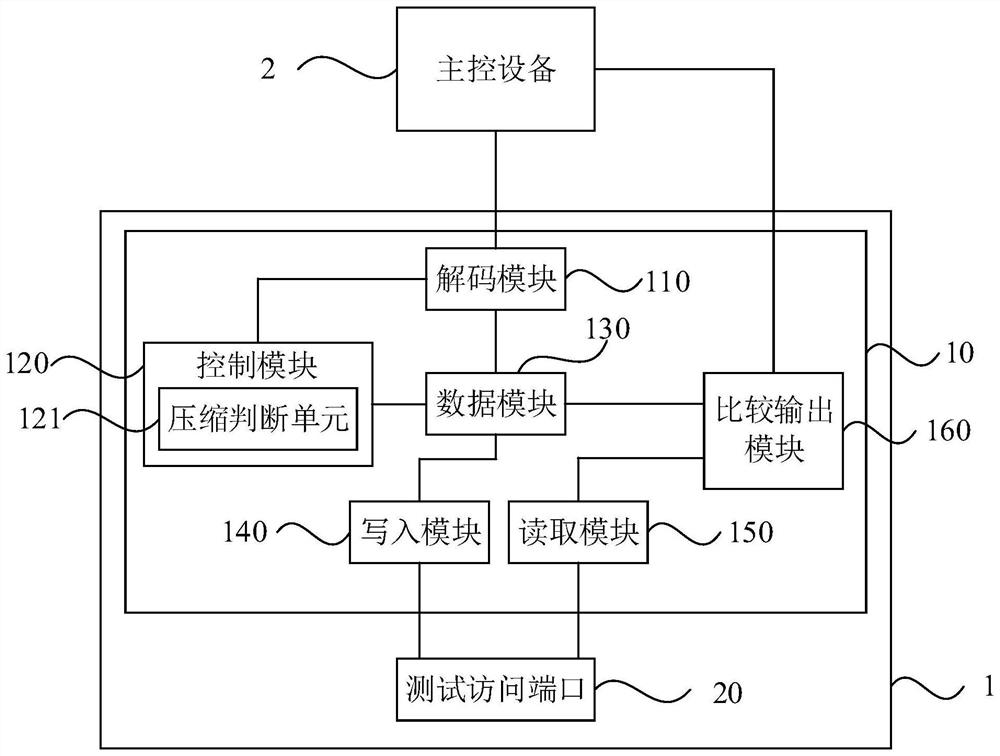

图1是本发明实施例提供的一种接口转换电路的结构示意图;

图2是本发明实施例提供的另一种接口转换电路的结构示意图;

图3是本发明实施例提供的一种比较输出模块的结构示意图;

图4是本发明实施例提供的一种芯片测试系统的结构示意图;

图5是本发明实施例提供的一种软件模块的数据压缩编码方式示意图;

图6是本发明实施例提供的一种芯片测试方法的流程示意图。

具体实施方式

下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

本发明实施例提供了一种接口转换电路,置于芯片内部,用于芯片测试。图1是本发明实施例提供的一种接口转换电路的结构示意图。参见图1,该接口转换电路10包括:解码模块110、控制模块120、数据模块130、写入模块140、读取模块150和比较输出模块160。

其中,解码模块110的输入端用于与外部的主控设备2连接;解码模块110用于根据主控设备2发出的测试向量得到测试指令和原始测试数据;其中,测试向量与接口转换电路10匹配。控制模块120的输入端与解码模块110的第一输出端连接;控制模块120包括压缩判断单元121,压缩判断单元121用于根据测试指令判断原始测试数据是否经过压缩,并将判断结果输出。数据模块130的第一输入端与解码模块110的第二输出端连接,数据模块130的第二输入端与控制模块120的输出端连接;数据模块130用于根据判断结果输出测试数据;其中,测试数据包括写入数据和期待响应数据。写入模块140的输入端与数据模块130的第一输出端连接,写入模块140的输出端与芯片1的测试访问端口(Testing Access Port,TAP)20的输入端连接,以将写入数据输出至芯片。读取模块150的输入端与芯片1的测试访问端口20的输出端连接;读取模块150用于采集芯片1反馈的读取数据。比较输出模块160的第一输入端与数据模块130的第二输出端连接,比较输出模块160的第二输入端与读取模块150的输出端连接;比较输出模块160用于根据读取数据和期待响应数据,得到错误信号并通过输出端输出。

示例性地,该接口转换电路10的工作过程为:解码模块110对接收到的测试向量进行解码,得到测试指令和原始测试数据;其中,测试指令包含指示原始测试数据是否经过压缩处理的指令(比如包含压缩标识)。控制模块120中的压缩判断单元121解码测试指令中的压缩标识,以判断原始测试数据是否经过压缩处理;并将判断结果传输给数据模块130。数据模块130根据判断结果输出测试数据;其中,当判断结果为已压缩时,数据模块130对原始测试数据进行解压后得到测试数据;当判断结果为未压缩时,数据模块130将原始测试数据作为测试数据直接输出;其中,测试数据中包括写入数据和期待响应数据,数据模块130将写入数据传输给写入模块140,将期待响应数据传输给比较输出模块160。写入模块140通过测试访问端口20将接收到的写入数据输出至芯片1;等待芯片1对写入数据进行处理后,读取模块150通过测试访问端口20采集芯片1反馈的读取数据,并传输给比较输出模块160。比较输出模块160将该读取数据与之前接收到的期待响应数据进行比较,产生错误信号并输出给主控设备2。

可选地,以对一条测试向量的解码过程为例,解码模块110将测试向量解码后,得到至少一条测试指令和对应的一组原始测试数据。测试指令和原始测试数据构成一整条解码后的向量。其中,测试指令相当于根据一定规则对该组原始测试数据进行抽象描述的数据,占据解码后的向量中的指令标识位;示例性地,测试指令可以包括指示原始测试数据是否经过压缩的压缩指令或指示原始测试数据长度的长度指令等等。原始测试数据占据解码后的向量中的数据位。解码模块110在完成解码后,将整条解码后的向量向其他模块传输。示例性地,一条测试向量中,多条测试指令可以对应一条原始测试数据,或者整组原始测试数据,或者其中几条原始测试数据,测试指令和原始测试数据的对应关系可以根据需求进行描述,此处不做限定。或者,解码模块110将测试向量解码后,可以得到仅包含测试指令的指令向量和仅包含原始测试数据的数据向量;并将指令向量传输给控制模块120,将数据向量传输给数据模块130。

可选地,数据模块130输出的测试数据中至少包括写入数据和期待响应数据;其中,写入数据用于对芯片1进行测试,期待响应数据与写入数据一一对应,用于检测芯片1反馈的读取数据是否正确。

可选地,该接口转换电路10适用于串行外设接口(Serial PeripheralInterface,SPI)、I2C(Inter-Integrated Circuit)、通用异步收发传输器(UniversalAsynchronous Receiver/Transmitter,UART)、控制器局域网总线(Controller AreaNetwork,CAN)、通用串行总线(Universal Serial Bus,USB)、高速串行计算机扩展总线(Peripheral Component Interconnect Express,PCIE)等多种常用的总线、接口和协议类型,可以将对芯片1在不同阶段的不同测试环境统一化,用一致的设置环境来测试所有向量。

可选地,比较输出模块160输出错误信号的方式有多种,在实际应用时可以根据需求进行设置。比如,当芯片1需要对多个测试向量进行处理时,比较输出模块160可以每次都将代表结果正确或错误的标识信号传输给主控设备2;或者,在结果正确时不输出信号,直到出现错误结果或测试完成时才输出信号;或者,将每个测试向量对应的结果储存,在测试结束后将正确结果和错误结果的个数和它们对应的指令位置一起输出。总之,读取数据与期待响应数据的比较在芯片1的内部完成,接口转换电路10仅输出标识测试结果的错误信号。

本发明实施例提供的接口转换电路10,设置有解码模块110、控制模块120和数据模块130。通过解码模块110解码测试向量得到测试指令和原始测试数据;其中,测试指令指示了该测试向量中解码出的原始测试数据是否经过了压缩,还可以指示压缩方式。控制模块120根据测试指令动态控制数据模块130的解压缩功能打开或关闭;当控制模块120中的压缩判断单元121根据测试指令判断出原始测试数据已压缩时,数据模块130解压原始测试数据,得到测试数据并输出。这样,在转换接口内部实现了硬件的解压缩结构,可以有效减少数据传输过程,提高测试效率。

并且,写入模块140和读取模块150的设置,使得写入数据可以直接灌入测试访问端口20,并且读取数据可以直接从测试访问端口20提取。也就是说,该接口转换电路10使芯片测试可以脱离JTAG测试引脚进行,通过接口转换逻辑可以灵活的应用各种功能接口加载测试向量,有利于在系统测试板级进行芯片测试,为产品出厂/返厂测试带来了很大的灵活性。以及,接口转换电路10中设置有比较输出模块160,可以在芯片内部进行读取数据和期待响应数据的比较,测试系统直接获取比较输出模块160输出的错误信号便可得知芯片1是否正常,并不需要输出所有读取数据在芯片1外部进行处理,从而减少数据传输,提高了测试效率。因此,本发明实施例可以提高芯片测试的灵活性和效率。

在上述各实施方式的基础上,可选地,解码模块110内配置有指令集,解码模块110依据指令集的规则解码测试向量,得到测试指令和原始测试数据。可选地,原始测试数据中包括原始写入数据、原始期待响应数据和原始掩码数据。其中原始掩码数据可以经数据模块130的处理得到掩码数据,掩码数据应用于比较输出模块160的比较过程,该应用在下面实施例中进行具体说明,此处不再展开。

示例性地,解码模块110将测试向量解码后得到的测试指令和原始测试数据构成解码后的向量,该解码后的向量的结构如表1所示。

表1

参见表1,解码后的向量的长度根据测试指令和原始测试数据的长度可以变化。示例性地,测试指令包括抽象描述编码方式、编码结构等的数据,比如指令类型、压缩标识、循环长度和数据长度等可以对测试向量进行标识的内容,均可以采用二进制编码等形式进行标识。原始测试数据包含与芯片实际检测相关的数据,比如原始写入数据、原始期待响应数据和原始掩码数据等。其中,每条测试指令中可包含多条原始写入数据、原始期待响应数据和原始掩码数据,在表1中以省略号体现。

在上述各实施方式的基础上,可选地,指令集中的指令包括赋值指令。示例性地,赋值指令可以位于表1中指令类型的标识位。其中,赋值指令的设置是由于在原始测试数据中包含一些特殊数据,其各数据位中的数据是根据一定的规则有序排列,那么此种原本需要传输的数据,由于其有序排列的特殊性而无需实际传输,只需在赋值指令中指示该数据的排列方式,在指令解析出来后直接在对应的数据位赋予数值即可。这样,可以有效减少数据传输的过程。

可选地,赋值指令包括全0指令(即数据全为0)或全1指令(即数据全为1),上述赋值指令的类型并不作为对本发明的限定,实际可根据测试数据的最终分布来决定赋值数据的定制。赋值指令可以针对原始写入数据、原始期待响应数据和原始掩码数据中的一项或多项。

图2是本发明实施例提供的另一种接口转换电路的结构示意图。参见图2,在上述各实施方式的基础上,可选地,数据模块130包括解压判断单元131、解压单元132和数据单元133。解压判断单元131的第一输入端与解码模块110的第二输出端连接,第二输入端与控制模块120连接,第一输出端与解压单元132连接,第二输出端与数据单元133连接;解压判断单元131接收控制模块120中压缩判断单元121的判断结果,根据判断结果判断由解码模块110传输的原始测试数据是否需要解压;若是(即压缩判断单元121的判断结果为已压缩时),则将原始测试数据传输至解压单元132;否则将原始测试数据传输至数据单元133。解压单元132分别与解压判断单元131和数据单元133连接,用于在解压判断单元131判断出原始测试数据需要解压时,根据原始测试数据的压缩编码规则,相应的对原始测试数据进行解压。综上,数据模块130通过解压判断单元131的判断来决定输出测试数据前是否需要对原始测试数据进行解压操作。

继续参见图2,在上述各实施方式的基础上,可选地,接口转换电路10还包括缓存模块170。缓存模块170与主控设备2、解码模块110、比较输出模块160和控制模块120连接,用于主控设备2与芯片1之间的数据传输。具体地,缓存模块170读取主控设备2中的测试向量,并传输给解码模块110;比较输出模块160输出错误信号给缓存模块170,由缓存模块170传输给主控设备2。缓存模块170传输测试向量和错误信号的方式可以由控制模块120来控制。示例性地,在测试开始时,缓存模块170可以对所有测试向量进行缓存并逐个传输给解码模块110;并且,在测试过程中,缓存模块170可以对多个测试向量的测试结果进行存储,最终一起传输给主控设备2。

继续参见图2,在上述各实施方式的基础上,可选地,接口转换电路10还包括并串转换模块141和串并转换模块151。其中,并串转换模块141连接在写入模块140和测试访问端口20之间;串并转换模块151连接在读取模块150和测试访问端口20之间。这样设置,通过并串转换将写入数据由测试访问端口20中的输入端(记为TDI)输入;并且芯片1的反馈数据(即读取数据)由测试访问端口20中的输出端(记为TDO)输出后,用串并转换成并行数据被读取模块150读取,可以减少测试时间,提高测试效率。

继续参见图2,在上述各实施方式的基础上,可选地,由于在某些测试过程中,只关心芯片1反馈的数据中的部分位是否正确,因此并不需要对读取数据中的每一位都进行判断。为了简化比较过程,数据模块130还包括第三输出端(数据单元133的第三输出端),数据模块130还用于根据解码模块110发出的原始测试数据得到掩码数据;比较输出模块160还包含第三输入端,比较输出模块160的第三输入端与数据模块130的第三输出端连接。在此基础上,示例性地,比较输出模块160的工作过程为:先根据读取数据和掩码数据得到实际关心数据,并过滤不关心数据;再将实际关心数据与期待响应数据进行比较,以判断芯片1反馈的读取数据是否正确。其中,数据模块130根据原始测试数据解析出的期待响应数据的格式与实际关心数据的格式相对应。

继续参见图2,在上述各实施方式的基础上,可选地,在控制模块120中,除去压缩判断单元121之外,还包括多种其他功能单元,用于执行不同的测试指令对应的操作。其中,不同的测试指令对应接口转换电路10中不同的模块,下面就几种可能的实施方式进行说明,但不作为对本发明的限定。

在一种实施方式中,可选地,测试指令包括循环指令,即重复执行同一个测试数据包含的测试过程,在测试指令中包含循环次数。控制模块120包括顺序控制单元122;顺序控制单元122分别与解码模块110、写入模块140和读取模块150连接,用于根据循环指令控制测试顺序。例如顺序控制单元122中包含指令计数器,在控制测试循环进行的同时,记录循环次数,在循环次数到达指定值时,停止对该写入数据的测试。这样,在循环测试时,无需解码模块110每次测试都进行测试向量的读取解析、以及测试指令和原始测试数据的传输,简化测试逻辑,节约测试时间,提高测试效率。

在另一种实施方式中,可选地,测试指令为使能指令;控制模块120包括使能控制单元123;使能控制单元123与写入模块140和读取模块150连接,用于控制测试开始或结束。这样,使得芯片测试的过程可控,比如在比较输出模块160中的比较结果第一次出现错误时即认定芯片不合格,停止测试,以缩短测试时间,提高测试效率。

继续参见图2,在另一种实施方式中,可选地,测试指令为调试指令,接口转换电路10中还包括:数据选择模块180。其中,数据选择模块180分别与比较输出模块160、读取模块150和缓存模块170连接;数据选择模块180输出测试结果;测试结果包括错误信号或读取数据。控制模块120还包括模式控制单元124;模式控制单元124与数据选择模块180连接,用于选择数据选择模块180输出的测试结果为错误信号或读取数据。示例性地,模式控制单元124在调试指令的控制下,控制芯片测试为调试模式或正常模式。其中,在调试模式下可以兼容传统的测试方案,即在读取模块150每次读取芯片1反馈的数据之后都由数据选择模块180返回给缓存模块170,或在特定测试向量处停下返回读取数据给缓存模块170。这种模式在早期芯片测试阶段非常有用,可以快速确定芯片1中的问题位置。在测试向量和测试环境稳定之后,芯片测试则可以采用正常模式,在正常模式下,模式控制单元124控制数据选择模块180读取比较输出模块160中的错误信号并输出,有利于提高测试效率。

上述各实施例示例性地对接口转换电路10的工作原理进行了说明,以下,就比较输出模块160的一种可能结构进行说明,但不作为对本发明的限定。

图3是本发明实施例提供的一种比较输出模块的结构示意图。参见图3,在一种实施方式中,可选地,比较输出模块160包括:与单元161、异或单元162和错误寄存器163。

其中,与单元161的第一输入端与数据模块130的第三输出端连接,用于接收掩码数据Dmask;与单元161的第二输入端与读取模块150的输出端连接,用于接收读取数据Dread;与单元161用于根据掩码数据Dmask和读取数据Dread(将掩码数据Dmask和读取数据Dread进行与运算)得到实际关心数据,并过滤不关心数据。异或单元162的第一输入端与数据模块130的第二输出端连接,用于接收期待响应数据Dexp;异或单元162的第二输入端与与单元161的输出端连接,用于接收实际关心数据;异或单元162用于根据实际关心数据和期待响应数据Dexp(将实际关心数据和期待响应数据Dexp进行异或运算)得到比较结果。错误寄存器163的第一输入端与异或单元162的输出端连接,错误寄存器163的第一输出端为比较输出模块160的输出端;错误寄存器163用于根据比较结果得到错误信号Serror,以及存储并输出错误信号Serror。

可选地,错误寄存器163可以是加法寄存器(或累积寄存器),当有多个测试向量时,每次比较结果都暂存在错误寄存器163中。错误寄存器163在比较结果指示实际关心数据有误时自动累加。最终,错误寄存器163可以将错误次数、报错数据和错误数据位等内容作为错误信号Serror输出。示例性地,当错误信号Serror代表错误次数时,设置错误寄存器163中记录的初始数值为0,只要最终的错误信号Serror不为0,就说明芯片1不合格,测试失败。

本发明实施例还提供了一种芯片,包括:如本发明任意实施例所提供的接口转换电路,具有相应的有益效果。

本发明实施例还提供了一种芯片测试系统,包括如本发明任意实施例所提供的芯片,具有相应的有益效果。图4是本发明实施例提供的一种芯片测试系统的结构示意图。参见图4,该芯片测试系统包括主控设备2、软件模块3和如本发明任意实施例所提供的芯片1。

其中,软件模块3用于处理原始标准测试向量,以得到与芯片1中的接口转换电路10相匹配的测试向量并输出;主控设备2包括输入端和输出端;主控设备2的输入端与软件模块3连接,主控设备2的输出端与芯片1连接;主控设备2用于将软件模块3发送的测试向量传送给芯片1。

下面,就软件模块3处理原始标准测试向量的一种可能的方式进行说明。继续参见图4,可选地,软件模块3包括预处理单元31、指令压缩单元32和数据压缩单元33;软件模块3通过上述三个功能单元将原始的未压缩的符合IEEE1149.1的标准的原始标准测试向量进行压缩和处理。

具体地,预处理单元31对原始标准测试向量进行预处理,在原始标准测试向量的基础上,添加抽象描述硬件压缩结构的文件,对一些特殊向量进行标识。然后,指令压缩单元132根据指令集的规则,对描述硬件压缩结构的标识数据进行压缩,生成测试指令;其中,测试指令主要包含了一些特定数据的指令和一些循环指令。最后,数据压缩单元33对原始标准测试向量进行灵活的数据压缩生成原始测试数据;测试指令和原始测试数据共同构成与芯片1中接口转换电路10相匹配的测试向量。

可选地,数据压缩单元33可以根据原始标准测试向量中数据的特性来决定是否进行数据压缩和选择数据压缩的算法。比如,若原始标准测试向量存在多数数据为0的稀疏特性,可以采用硬件易实现编码方法,对数据进行压缩编码。示例性地,图5是本发明实施例提供的一种软件模块的数据压缩编码方式示意图。参见图5,针对一个多位(比如32位)的数据可以采用少位(比如5位)二进制编码指示数据中非零数据的位置。如图5所示:原始数据为00001000000000000000000100000000,可以用00101表示第5位为非零位,用11000表示第24位为非零位;这样,0010111000这个10位的数据就可以表示上述32位的数据。这样,可以用较少位的数据来表示较多位的数据,实现有效的数据压缩。

可选地,数据压缩单元33还可以根据芯片测试的阶段选择是否进行数据压缩。比如在早期芯片测试阶段(调试阶段),对测试响应的精度要求较高,此时,可以不进行数据压缩,从而帮助快速定位问题;而在测试向量和测试环境稳定之后,则可以进行数据压缩,以有效减少测试向量的传输消耗。

本发明实施例还提供了一种芯片测试方法,应用于本发明任意实施例所提供的芯片测试系统,用于对本发明任意实施例所提供的芯片进行测试,具有相应的有益效果。图6是本发明实施例提供的一种芯片测试方法的流程示意图。参见图6,该芯片测试方法包括以下步骤:

S110、主控设备将与芯片中的接口转换电路相匹配的测试向量传送给芯片中的接口转换电路。

其中,主控设备可以通过缓存模块将测试向量传输给解码模块。

S120、解码模块接收测试向量,并根据测试向量得到测试指令和原始测试数据。

其中,测试指令包含指示原始测试数据是否经过压缩处理的指令。可选地,以对一条测试向量的解码过程为例,解码模块将测试向量解码后,得到至少一条测试指令和对应的一组原始测试数据。测试指令和原始测试数据构成一整条解码后的向量。解码模块在完成解码后,将整条解码后的向量向其他模块传输。或者,解码模块将测试向量解码后,可以得到仅包含测试指令的指令向量和仅包含原始测试数据的数据向量;并将指令向量传输给控制模块,将数据向量传输给数据模块。

S130、控制模块接收测试指令,根据测试指令判断原始测试数据是否经过压缩,并将判断结果输出。

其中,控制模块可以通过判断结果控制数据模块是否对原始测试数据进行解压。

S140、数据模块接收判断结果,根据判断结果输出测试数据;其中,测试数据包括写入数据和期待响应数据。

其中,当判断结果为已压缩时,数据模块对原始测试数据进行解压后得到测试数据;当判断结果为未压缩时,数据模块将原始测试数据作为测试数据直接输出。写入数据用于对芯片进行测试,期待响应数据与写入数据一一对应,用于检测芯片反馈的读取数据是否正确。

S150、写入模块将写入数据通过测试访问端口传输给芯片。

其中,写入模块可通过并串转换模块将写入数据传输至测试访问端口的输入端。

S160、读取模块通过测试访问端口采集芯片反馈的读取数据。

其中,读取模块可以通过串并转换模块从测试访问端口的输出端读取芯片反馈的读取数据。

S170、比较输出模块根据读取数据和期待响应数据得到错误信号并输出。

其中,比较输出模块输出错误信号的方式有多种,在实际应用时可以根据需求进行设置。比如,当芯片需要对多个测试向量进行处理时,比较输出模块可以每次都将代表结果正确或错误的标识信号传输给主控设备;或者,在结果正确时不输出信号,直到出现错误结果或测试完成时才输出信号;或者,将每个测试向量对应的结果储存,在测试结束后将正确结果和错误结果的个数和它们对应的指令位置一起输出。总之,读取数据与期待响应数据的比较在芯片的内部完成,接口转换电路仅输出标识测试结果的错误信号。

可选地,由于在某些测试过程中,只关心芯片反馈的数据中的部分位是否正确,因此并不需要对读取数据中的每一位都进行判断。为了简化比较过程,该测试方法还包括:

数据模块根据原始测试数据得到掩码数据;

比较输出模块先根据读取数据和掩码数据得到实际关心数据,并过滤不关心数据;再将实际关心数据与期待响应数据进行比较,以判断芯片反馈的读取数据是否正确。其中,数据模块根据原始测试数据解析出的期待响应数据的格式与实际关心数据的格式相对应。

可选地,当测试过程中,需要对芯片中的问题定位时,该测试方法还可以包括:数据模块根据测试向量得到测试指令;

控制模块根据测试指令控制芯片测试为调试模式;

数据选择模块在控制模块的控制下从读取模块获得读取数据,并将读取数据作为测试结果输出。

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

- 接口转换电路、芯片、芯片测试系统及方法

- 用于裸芯片的测试接口板和用于裸芯片的测试系统