一种针对SiC MOSFET消隐时间可调的抗干扰短路保护电路

文献发布时间:2023-06-19 11:42:32

技术领域

本发明涉及电力电子技术领域,特别是涉及一种针对SiC MOSFET消隐时间可调的抗干扰短路保护电路。

背景技术

SiC-MOSFET作为第三代宽禁带功率半导体器件,与传统Si-IGBT相比,具有开关速度快,击穿电压高,耐高温,封装紧凑,电流密度大等优点,其可以广泛应用于高频高压功率变换器领域,如电动汽车,光伏逆变,轨道交通等。与此同时,SiC MOSFET较快的开关速度和较大的电流密度,导致其短路耐受时间较短,通常低于3μs。

SiC MOSFET短路情况分为两种,一种是在SiC MOSFET开启前功率回路已经发生短路,SiC MOSFET开启后电流迅速上升,且源漏电压Vds保持母线电压不变,这种情况称为硬开启短路。另一种是在SiC MOSFET开启后的导通状态下发生短路,此时SiC MOSFET的源漏电压Vds迅速从导通压降上升至母线电压,同时电流也迅速上升,这种情况称为负载短路。若不采取措施及时关断SiC MOSFET,这两种短路情况都会导致SiC MOSFET功耗迅速上升,直至烧毁。

为了对SiC MOSFET进行有效的短路保护,在短路发生后,需要迅速的探测到短路情况,并尽快将SiC MOSFET关断。目前针对SiC MOSFET的短路保护问题,仍然广泛沿用传统Si-IGBT常用的去饱和DESAT(Desaturation)方案。去饱和保护方案的思想是监测SiCMOSFET源漏电压Vds,将源漏电压Vds与一个参考电压进行比较,参考电压通常设定为高于器件导通压降的一个值;SiC MOSFET正常开启或导通时,源漏电压Vds应低于参考电压,如图1所示。去饱和保护方案的基本工作原理如下:对于硬开启短路情况(如图2所示),在SiCMOSFET栅极驱动信号(V_drive_logic)拉高之后,经过一个固定的消隐时间后,检测源漏电压Vds是否下降至阈值电压以下。若源漏电压Vds降至阈值电压以下,判定SiC MOSFET开启正常;若源漏电压Vds没有降至阈值电压,判定SiC MOSFET发生硬开启短路,同时将短路信号反馈给保护电路,将SiC MOSFET关断。对于负载短路情况(如图3所示),在SiC MOSFET导通后,监测源漏电压Vds是否在阈值电压以下。如果源漏电压Vds在阈值电压以下,判定SiCMOSFET工作在正常导通状态;若源漏电压Vds超过了阈值电压,判定SiC MOSFET发生了负载短路,同时将短路信号反馈给保护电路,将SiC MOSFET关断。

消隐时间决定了去饱和短路保护方案对上述两种短路情况的检测延时。延时太短,保护电路容易误触发;延时太长,无法有效保护SiC MOSFET。目前去饱和短路保护方案的消隐时间是通过电流源给电容充电至阈值电压来设置,即消隐时间为

发明内容

本发明所要解决的技术问题是提供一种针对SiC MOSFET消隐时间可调的抗干扰短路保护电路,能够调整消隐时间,且具有较强的抗干扰能力。

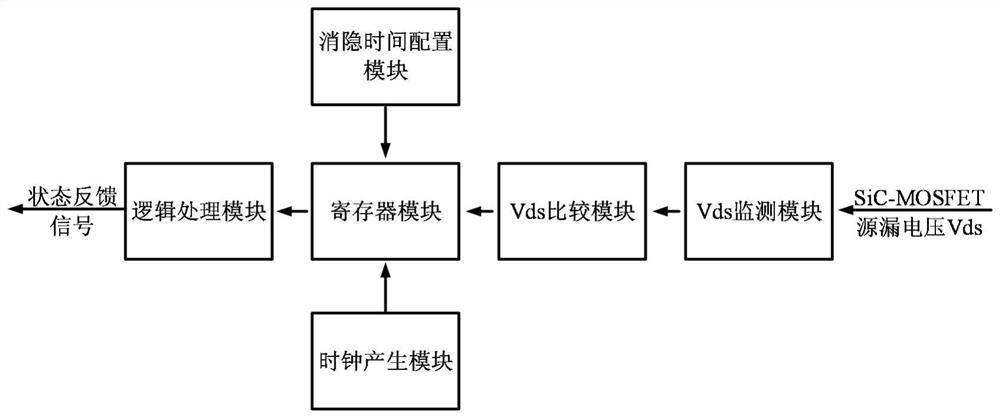

本发明解决其技术问题所采用的技术方案是:提供一种针对SiC MOSFET消隐时间可调的抗干扰短路保护电路,包括:Vds监测模块,用于监测SiC MOSFET的源漏电压Vds;Vds比较模块,用于将监测到的源漏电压Vds与阈值进行比较,并输出逻辑信号,还包括:寄存器模块,用于存储所述逻辑信号;时钟产生模块,与所述寄存器模块相连,用于产生所述寄存器模块的所需的工作时钟信号;消隐时间配置模块,与所述寄存器模块相连,用于调节所述寄存器模块的有效位数和工作时钟频率;逻辑处理模块,用于根据所述寄存器模块中存储的逻辑信号,在发生短路时输出短路保护信号。

所述Vds监测模块包括快恢复高压二极管和电流源,所述快恢复高压二极管的阴极与待监测SiC MOSFET的漏极相连,阳极与所述电流源相连。

所述Vds比较模块为比较器,所述比较器的第一输入端与所述Vds监测模块的输出端相连,第二输入端与所述阈值信号端相连,输出端与所述寄存器模块相连。

所述寄存器模块采用N位串行移位寄存器。

所述时钟产生模块采用振荡器实现。

所述逻辑处理模块采用数字芯片或逻辑电路实现逻辑控制。

有益效果

由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明通过增加的消隐时间配置模块,寄存器模块和时钟产生模块,通过改变寄存器位数和工作时钟频率实现了对消隐时间的调整,同时,由于是根据n个时钟周期的源漏电压Vds监测结果判断SiC MOSFET是否发生短路,所以可以降低源漏电压Vds振荡对保护电路的影响。

附图说明

图1是SiC MOSFET正常开关波形图;

图2是SiC MOSFET硬开启短路情况示意图;

图3是SiC MOSFET负载短路情况示意图;

图4是传统DESAT保护电路结构的电路图;

图5是本发明实施方式的结构方框图;

图6是本发明实施方式的电路实现图;

图7是本发明实施方式的正常开关时的寄存器数据示意图;

图8是本发明实施方式的开启时发生硬开启时的寄存器数据示意图;

图9是本发明实施方式的开启后发生负载短路时的寄存器数据示意图。

具体实施方式

下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本申请所附权利要求书所限定的范围。

本发明的实施方式涉及一种针对SiC MOSFET消隐时间可调的抗干扰短路保护电路,如图5所示,包括依次相连的Vds监测模块、Vds比较模块、寄存器模块和逻辑处理模块。其中,寄存器模块还与时钟产生模块和消隐时间配置模块相连。

如图6所示,Vds监测模块用于监测SiC MOSFET的源漏电压Vds,其可以包括快恢复高压二极管和电流源,所述快恢复高压二极管的阴极与待监测SiC MOSFET的漏极相连,阳极与所述电流源相连。该快恢复高压二极管可以由多个二极管串联等效而成,其反向击穿电压高于待监测SiC MOSFET的额定电压。

Vds比较模块,用于将监测到的源漏电压Vds与阈值进行比较,并输出逻辑信号,其可以通过一个比较器实现,该比较器的的正相输入端与所述Vds监测模块的输出端相连,反相输入端与所述阈值信号端相连,输出端与所述寄存器模块相连,如此当源漏电压Vds小于阈值时,比较器输出端的输出为0,当源漏电压Vds大于阈值时,比较器输出端的输出为1。

寄存器模块,用于存储所述逻辑信号。本实施方式中的寄存器模块可以采用8位串行移位寄存器,当8位串行移位寄存器的有效位数为8位时,其可以存储8个时钟周期的Vds比较模块输出的逻辑信号,因此当源漏电压Vds出现振荡时,不会直接输出短路信号,具备了较强的抗干扰能力。在初始状态下,本实施方式中的寄存器模块的初始值全为0。

时钟产生模块,用于产生所述寄存器模块的所需的工作时钟信号,该时钟产生模块可以采用振荡器实现。

消隐时间配置模块,用于调节所述寄存器模块的有效位数和工作时钟频率,通过调节寄存器模块的有效位数和工作时钟频率可以对消隐时间进行调节。本实施方式的短路保护电路的消隐时间t

逻辑处理模块,用于根据所述寄存器模块中存储的逻辑信号,在发生短路时输出短路保护信号。逻辑处理模块可以采用数字芯片实现逻辑控制,也可以采用逻辑电路实现逻辑控制,本实施方式中采用一个与门,该与门的输入端分别与8位串行移位寄存器的8个输出端相连,如此只有当8位串行移位寄存器的n个有效位数全部为1时,其才会输出短路保护信号。

下面以以SiC MOSFET的一个开关过程说明本发明的工作原理。首先,驱动电路逻辑信号拉高,SiC MOSFET栅极电压逐渐升高,源漏电压Vds随之下降,器件开始开启。比较器接收到监测到的SiC MOSFET的源漏电压Vds,当源漏电压Vds高于阈值时,比较器输出为1;当源漏电压Vds低于阈值时,比较器输出为0。驱动电路逻辑信号拉高后,开始每隔一个时钟周期读一次比较器的输出值,并将该数据移入寄存器进行保存。8个时钟周期后,若寄存器值为全1,表明源漏电压Vds没有正常下降,发生硬开启短路,并输出短路信号,如图8所示。8个时钟周期后,若寄存器值不为全1,表明Vds正常下降,SiC MOSFET开启正常。其次,SiCMOSFET正常开启后,源漏电压Vds降至低于比较器阈值的导通压降,比较器输出为0,则寄存器读入全0,表明SiC MOSFET正常导通;若源漏电压Vds存在较大幅度的开启振荡,则比较器交替输出高低电平,寄存器读入010101,因此不会出现寄存器全1的情况,因此不会输出短路信号。若SiC MOSFET在导通过程中发生负载短路情况,则源漏电压Vds迅速上升至母线电压,比较器输出为高,8个时钟周期后,寄存器读入全1,输出短路信号,如图9所示。因此,该电路可以有效的检测硬开启短路和负载短路情况,并降低了源漏电压Vds开启振荡的对短路保护电路的干扰。最后,驱动电路逻辑信号拉低,SiC MOSFET器件关闭,寄存器全部置0,保护过程结束。图7,8,9分别描述了正常开关,硬开启短路,负载短路三种情况下的寄存器数据变化波形。

通过分析SiC MOSFET的开关过程,可以看出该短路保护电路的消隐时间t

不难发现,本发明通过增加的消隐时间配置模块,寄存器模块和时钟产生模块,通过改变寄存器位数和工作时钟频率实现了对消隐时间的调整,同时,由于是根据n个时钟周期的源漏电压Vds监测结果判断SiC MOSFET是否发生短路,所以可以降低源漏电压Vds振荡对保护电路的影响。

- 一种针对SiC MOSFET消隐时间可调的抗干扰短路保护电路

- 针对用于开关模式电源的过载保护的可调消隐时间