芯片外驱动电路和信号补偿方法

文献发布时间:2023-06-19 11:45:49

技术领域

本发明内容是有关于一种芯片外驱动(off chip driver,OCD)电路和信号补偿方法,且特别是有关于改善信号失真的芯片外驱动电路和信号补偿方法。

背景技术

随着科技发展,存储器的操作速度变得越来越快速。在高速数据的数据传输中,信号的振幅会衰减,从而导致信号失真。

因此,如何改善在高速数据的数据传输中信号失真的情况是本领域的重要课题。

发明内容

本发明的目的在于提供一种芯片外驱动电路和信号补偿方法,借由补偿电路提高控制信号的转换速率,便能改善输出信号的转换速率,使得输出信号的输出数据能够清楚。

本发明内容的一实施例是关于一种芯片外驱动电路。芯片外驱动电路包含判别电路、第一补偿电路、第二补偿电路、上拉电路以及下拉电路。判别电路用以根据时脉信号和输入数据输出第一判别信号和第二判别信号。第一补偿电路耦接至判别电路,并用以响应于第一判别信号和第二判别信号以产生第一控制信号。第二补偿电路耦接至判别电路,并用以响应于第一判别信号和第二判别信号以产生第二控制信号。上拉电路用以响应于第一控制信号致能。下拉电路用以响应于第二控制信号致能。

在部分实施例中,当输入数据自第一电平转换至第二电平时,判别电路用以产生具有高电平的第一判别信号,当输入数据自第二电平转换至第一电平时,判别电路用以产生具有低电平的第二判别信号。

在部分实施例中,第一补偿电路包含第一可调变增强电路,第一可调变增强电路包含:第一增强元件,用以根据第二判别信号导通以提供高电压作为第一控制信号;以及第二增强元件,用以根据第一判别信号导通以提供低电压作为第一控制信号。第二补偿电路包含第二可调变增强电路,第二可调变增强电路包含:第三增强元件,用以根据第二判别信号导通以提供高电压作为第二控制信号;以及第四增强元件,用以根据第一判别信号导通以提供低电压作为第二控制信号。

在部分实施例中,第一补偿电路还包含第一前置驱动器,第二补偿电路还包含第二前置驱动器,第一前置驱动器和第二前置驱动器为互补式金属氧化物半导体。

在部分实施例中,第一增强元件包含:第一开关,用以根据第一致能信号导通;以及第一晶体管,耦接至第一开关,用以响应于输入数据导通。第二增强元件包含:第二开关,用以根据第二致能信号导通;以及第二晶体管,耦接至第二开关,用以响应于输入数据导通。第三增强元件包含:第三开关,用以根据第三致能信号导通;以及第三晶体管,耦接至第三开关,用以响应于输入数据导通。第四增强元件包含:第四开关,用以根据第四致能信号导通;以及第四晶体管,耦接至第四开关,用以响应于输入数据导通。

在部分实施例中,第一增强元件还包含:第一逻辑门,用以根据第二判别信号和第一选择信号产生第一致能信号以输出第一致能信号至第一开关。第二增强元件还包含:第二逻辑门,用以根据第一判别信号和第二选择信号产生第二致能信号以输出第二致能信号至第二开关。第三增强元件还包含:第三逻辑门,用以根据第二判别信号和第三选择信号产生第三致能信号以输出第三致能信号至第三开关。第四增强元件还包含:第四逻辑门,用以根据第一判别信号和第四选择信号产生第四致能信号以输出第四致能信号至第四开关。

在部分实施例中,第一增强元件还包含:第一多工器,用以根据第二判别信号和第一选择信号产生第一致能信号以输出第一致能信号至第一开关。第二增强元件还包含:第二多工器,用以根据第一判别信号和第二选择信号产生第二致能信号以输出第二致能信号至第二开关。第三增强元件还包含:第三多工器,用以根据第二判别信号和第三选择信号产生第三致能信号以输出第三致能信号至第三开关。第四增强元件还包含:第四多工器,用以根据第一判别信号和第四选择信号产生第四致能信号以输出第四致能信号至第四开关。

在部分实施例中,第一开关和第三开关为P型金氧半场效晶体管,第二开关和第四开关为N型金氧半场效晶体管。

在部分实施例中,第一开关和第三开关为搭配非门的N型金氧半场效晶体管,第二开关和第四开关为搭配非门的P型金氧半场效晶体管。

在部分实施例中,第一开关、第二开关、第三开关和第四开关为互补式金属氧化物半导体。

在部分实施例中,第一补偿电路包含第一可调变增强电路,第一可调变增强电路包含:多个第一增强元件,该些第一增强元件并联连接,用以根据该第二判别信号和多个第一选择信号导通以提供高电压作为该第一控制信号;以及多个第二增强元件,该些第二增强元件并联连接,用以根据该第一判别信号和多个第二选择信号导通以提供低电压作为该第一控制信号。第二补偿电路包含第二可调变增强电路,该第二可调变增强电路包含:多个第三增强元件,该些第三增强元件并联连接,用以根据该第二判别信号和多个第三选择信号导通以提供该高电压作为该第二控制信号;以及多个第四增强元件,该些第四增强元件并联连接,用以根据该第一判别信号和多个第四选择信号导通以提供该低电压作为该第二控制信号。

在部分实施例中,第一增强元件中的一个包含:第一开关,用以根据第一致能信号导通;以及至少一个第一晶体管,与第一开关串联连接,用以响应于输入数据导通。第二增强元件中的一个包含:第二开关,用以根据第二致能信号导通;以及至少一个第二晶体管,与第二开关串联连接,用以响应于输入数据导通。第三增强元件中的一个包含:第三开关,用以根据第三致能信号导通;以及至少一个第三晶体管,与第三开关串联连接,用以响应于输入数据导通。第四增强元件中的一个包含:第四开关,用以根据第四致能信号导通;以及至少一个第四晶体管,与第四开关串联连接,用以响应于输入数据导通。

在部分实施例中,第一控制信号的第一转换速率是根据第一选择信号和第二选择信号的数量而定,第二控制信号的第二转换速率是根据第三选择信号和第四选择信号的数量而定。

在部分实施例中,在第一增强元件的数量、第二增强元件的数量、第三增强元件的数量和第四增强元件的数量中至少一个与其他者不同。

本发明内容的另一实施例是关于一种信号补偿方法,包含:当输入数据自第一电平转为第二电平时,将第一判别信号转为高电平;当输入数据自第二电平转为第一电平时,将第二判别信号转为低电平;响应于第一判别信号和第二判别信号产生第一控制信号和第二控制信号;响应于第一控制信号致能上拉电路;以及响应于第二控制信号致能下拉电路。

在部分实施例中,信号补偿方法还包含:响应于具有第一电平的输入数据感应高电压作为第一控制信号或第二控制信号;以及响应于具有第二电平的输入数据感应低电压作为第一控制信号或第二控制信号。

在部分实施例中,信号补偿方法还包含:根据第二判别信号导通第一增强元件以提供高电压作为第一控制信号;根据第一判别信号导通第二增强元件以提供低电压作为第一控制信号;根据第二判别信号导通第三增强元件以提供高电压作为第二控制信号;根据第一判别信号导通第四增强元件以提供低电压作为第二控制信号。

在部分实施例中,信号补偿方法还包含:根据第二判别信号的至少一个第一致能信号导通第一增强元件的至少一个第一开关以提供高电压作为第一控制信号;根据第一判别信号的至少一个第二致能信号导通第二增强元件的至少一个第二开关以提供低电压作为第一控制信号;根据第二判别信号的至少一个第三致能信号导通第三增强元件的至少一个第三开关以提供高电压作为第二控制信号;以及根据第一判别信号的至少一个第四致能信号导通第四增强元件的至少一个第四开关以提供该低电压作为第二控制信号。

在部分实施例中,信号补偿方法还包含:根据至少一个第一选择信号产生至少一个第一致能信号;根据至少一个第二选择信号产生至少一个第二致能信号;根据至少一个第三选择信号产生至少一个第三致能信号;以及根据至少一个第四选择信号产生至少一个第四致能信号,其中至少一个第一致能信号的数量、至少一个第二致能信号的数量、至少一个第三致能信号的数量及至少一个第四致能信号的数量分别等于至少一个第一选择信号的数量、至少一个第二选择信号的数量、至少一个第三选择信号及至少一个第四选择信号的数量。

在部分实施例中,第一控制信号的第一转换速率是根据至少一个第一选择信号和至少一个第二选择信号的数量而定,第二控制信号的第二转换速率是根据至少一个第三选择信号和至少一个第四选择信号的数量而定。

综上所述,本发明的芯片外驱动电路和信号补偿方法,通过应用上述各个实施例中,借由增强电路,控制信号的上升和下降转换速率便能够提高,以改善输出信号上升和下降的转换速率,当输入数据转换时,使得输出信号的输出数据能够清楚。

附图说明

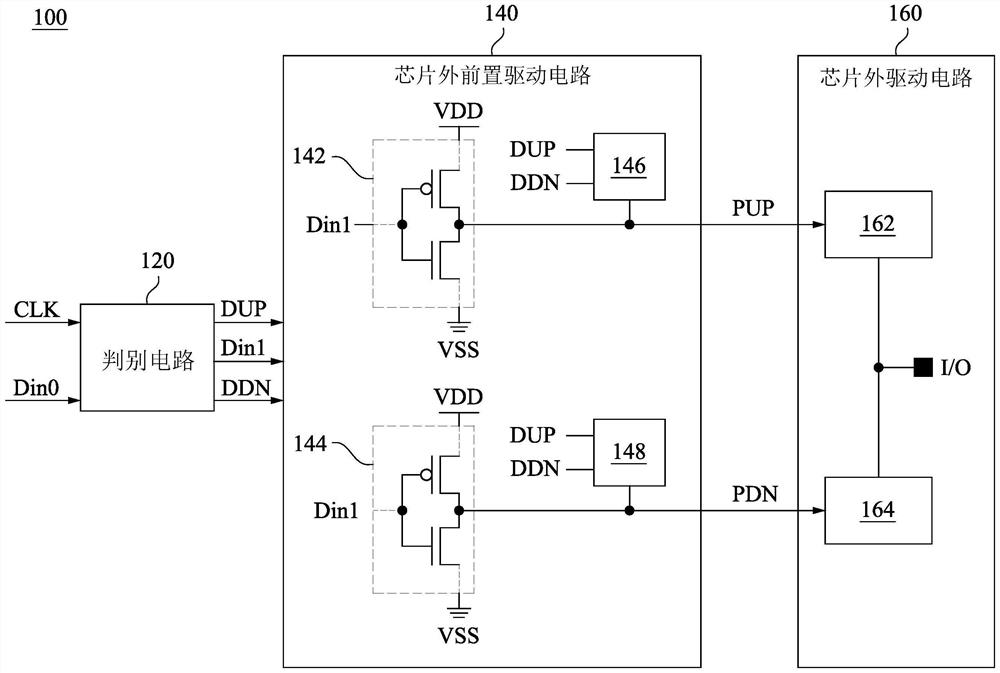

图1是根据本发明内容的部分实施例所绘示的一种芯片外驱动电路的示意图;

图2A至图2D是根据本发明内容的部分实施例所绘示的一种上拉电路的示意图;

图3A至图3D是根据本发明内容的部分实施例所绘示的一种下拉电路的示意图;

图4是根据习知技术所绘示的一种芯片外驱动电路的信号示意图;

图5是根据本发明内容的部分实施例所绘示的一种芯片外前置驱动电路的信号示意图;

图6是根据本发明内容的部分实施例所绘示的一种补偿电路的示意图;

图7是根据本发明内容的部分实施例所绘示的一种芯片外驱动电路的信号示意图;

图8A和图8B是根据本发明内容的部分实施例所绘示的一种第一开关的示意图;

图9A和图9B是根据本发明内容的部分实施例所绘示的一种第二开关的示意图;

图10A和图10B是根据本发明内容的部分实施例所绘示的一种第一增强元件的示意图;

图11A和图11B是根据本发明内容的部分实施例所绘示的一种第二增强元件的示意图。

主要附图标记说明:

100-芯片外驱动电路,120-判别电路,140-芯片外前置驱动电路,142、144-前置驱动器,146、148-增强电路,160-芯片外驱动电路,162、162a、162b、162c-上拉电路,164、164a、164b、164c-下拉电路,I/O-输入输出端,CLK-时脉信号,Din0、Din1-输入数据,DUP、DDN-判别信号,PUP-上拉控制信号,PDN-下拉控制信号,VDD-高电压,VSS-低电压,MP<1>、MP<2>~MP

具体实施方式

具体实施方式现在将在下文中参考附图更全面地描述本发明内容,附图中示出了本发明的示例性实施例。然而,本发明可以以许多不同的形式实施,不应该被解释为限于此处阐述的实施例。提供这些实施例是为了使本发明内容彻底和完整,并且向本领域技术人员充分传达本发明内容的范围。相同的附图标记表示相同的元件。

本文所使用的所有词汇具有其通常的意涵。上述的词汇在普遍常用的字典中的定义,在本说明书的内容中包含任意一个在此讨论的词汇的使用例子仅为示例,不应限制到本发明内容的范围与意涵。同样地,本发明内容也不仅以于此说明书所示出的各种实施例为限。

在本文中,使用第一、第二与第三等等的词汇,是用于描述各种元件、组件、区域、层与/或区块是可以被理解的。但是这些元件、组件、区域、层与/或区块不应该被这些术语所限制。这些词汇只限于用来辨别单一元件、组件、区域、层与/或区块。因此,在下文中的第一元件、组件、区域、层与/或区块也可被称为第二元件、组件、区域、层与/或区块,而不脱离本发明的本意。

关于本文中所使用的“耦接”或“连接”,均可指两个或多个元件相互直接作实体或电性接触,或是相互间接作实体或电性接触,也可指两个或多个元件相互操作或动作。在本文中所使用的用词“包含”、“具有”等等,均为开放性的用语,即意指“包含但不限于”。此外,本文中所使用的“及/或”,包含相关列举项目中一个或多个项目的任意一个以及其所有组合。

请参考图1。图1是根据本发明内容的部分实施例所绘示的一种芯片外驱动电路100的示意图。如图1所示,芯片外驱动电路100包含判别电路120、芯片外前置驱动电路(OCDfront-end driving circuit)140以及芯片外驱动电路(OCD driver)160。在部分实施例中,芯片外前置驱动电路140包含第一前置驱动器142、第二前置驱动器144、第一可调变增强电路146和第二可调变增强电路148。在部分实施例中,芯片外驱动电路160包含上拉电路162和下拉电路164。

结构上,判别电路120耦接至芯片外前置驱动电路140。芯片外前置驱动电路140耦接至芯片外驱动电路160。具体而言,判别电路120耦接至第一前置驱动器142、第二前置驱动器144、第一可调变增强电路146以及第二可调变增强电路148。第一前置驱动器142和第一可调变增强电路146耦接至上拉电路162。第二前置驱动器144和第二可调变增强电路148耦接至下拉电路164。

请参考图2A至图2D。图2A至图2D是根据本发明内容的部分实施例所绘示的一种上拉电路162a~162d的示意图。在部分实施例中,图1中的上拉电路162可由如图2A中的包含晶体管MP<1>的上拉电路162a所实现。晶体管MP<1>的第一端耦接至高电压VDD。晶体管MP<1>的第二端耦接至输入输出端I/O。晶体管MP<1>的控制端用以接收上拉控制信号PUP。晶体管MP<1>用以根据具有低电平的上拉控制信号PUP导通,以提供高电压VDD至输入输出端I/O。

在其他部分实施例中,图1中的上拉电路162可由如图2B中包含相互串联的晶体管MP<1>和电阻R1的上拉电路162b所实现,或者由如图2C中包含多个相互串联的晶体管MP<1>~MP

请参考图3A至图3D。图3A至图3D是根据本发明内容的部分实施例所绘示的一种下拉电路164a~164d的示意图。在部分实施例中,图1中的下拉电路164可分别由图3A至图3D中的下拉电路164a~164d所实现。下拉电路164相似于上拉电路162,但由N型晶体管MN<1>~MN

值得注意的是,上拉电路162a~162d和下拉电路164a~164d仅为说明举例,并非用以限制本发明。任何能实施上拉驱动器和下拉驱动器的电路都在本案发明的范围内。也就是说,本领域具有通常知识者可调整上拉电路和下拉电路的设计。

请回头参考图1。操作上,判别电路120用以接收时脉信号CLK和输入数据Din0,并根据输入数据Din0输出第一判别信号DUP和第二判别信号DDN。芯片外前置驱动电路140用以接收输入数据Din1、第一判别信号DUP和第二判别信号DDN。第一前置驱动器142产生上拉控制信号PUP。第二前置驱动器144产生下拉控制信号PDN。第一可调变增强电路146由第一判别信号DUP和第二判别信号DDN所控制,用以改善上拉控制信号PUP的强度。第二可调变增强电路148也由第一判别信号DUP和第二判别信号DDN所控制,用以改善下拉控制信号PDN的强度。值得注意的是时脉信号CLK仅为举例,在部分实施例中,判别电路120可在没有时脉信号CLK的情况下产生输入数据Din1、第一判别信号DUP和第二判别信号DDN。输入数据Din1是经过延迟后的输入数据Din0,借以对齐判别电路120所处理的其他信号。芯片外驱动电路160用以接收上拉控制信号PUP和下拉控制信号PDN,并相应于输入输出端I/O感应输出信号。

具体而言,第一前置驱动器142用以接收输入数据Din1,并根据输入数据Din1选择性地提供高电压VDD或低电压VSS作为上拉控制信号PUP。第二前置驱动器144用以接收输入数据Din1,并根据输入数据Din1选择性地提供高电压VDD或低电压VSS作为下拉控制信号PDN。第一可调变增强电路146用以接收第一判别信号DUP和第二判别信号DDN,并根据第一判别信号DUP和第二判别信号DDN选择性地提供高电压VDD或低电压VSS作为上拉控制信号PUP。第二可调变增强电路148用以接收第一判别信号DUP和第二判别信号DDN,根据第一判别信号DUP和第二判别信号DDN选择性地提供高电压VDD或低电压VSS作为下拉控制信号PDN。

在部分实施例中,第一前置驱动器142和第二前置驱动器144为互补式金属氧化物半导体(CMOS)。举例来说,如图1所示,第一前置驱动器142包含P型金氧半场效晶体管(PMOS)和N型金氧半场效晶体管(NMOS)。PMOS的第一端用以接收高电压VDD,NMOS的第二端用以接收低电压VSS,PMOS和NMOS的控制端皆用以接收输入数据Din1,而PMOS的第二端和NMOS的第一端用以输出上拉控制信号PUP。第二前置驱动器144相似于第一前置驱动器142,因此不再赘述。

值得注意的是,前置驱动器142、144可由CMOS之外其他的电路所实现,或者前置驱动器142、144可包含其他电路在CMOS和高电压VDD之间、在CMOS和低电压VSS之间,或者在CMOS和输入数据Din1之间。在其他部分实施例中,前置驱动器142、144可包含一或多个相互串联或并联的晶体管。

请一并参考图1和图4。图4是根据习知技术所绘示的一种芯片外驱动电路100的信号示意图。如图4所示,在期间T1,输入数据Din1位于高电平。前置驱动器142、144的PMOS关断而前置驱动器142、144的NMOS根据具有高电平的输入数据Din1导通,以提供低电压VSS作为上拉控制信号PUP和下拉控制信号PDN。因此,上拉电路162根据具有低电压VSS的上拉控制信号PUP导通,而下拉电路164根据具有低电压VSS的下拉控制信号PDN导通。如此一来,在期间T1,芯片外驱动电路160对应于输入输出端I/O感应具有高电压VDD的输出信号。

在另一方面,在期间T2,输入数据Din1位于低电平。前置驱动器142、144的PMOS导通,而前置驱动器142、144的NMOS根据具有低电平的输入数据Din1导通,以提供高电压VDD作为上拉控制信号PUP和下拉控制信号PDN。因此,上拉电路162根据具有高电压VDD的上拉控制信号PUP关断,而下拉电路164根据具有高电压VDD的下拉控制信号PDN导通。如此一来,在期间T2,芯片外驱动电路160对应于输入输出端I/O感应具有低电压VSS的输出信号。

据此,输入输出端I/O的输出信号理想上应与输入数据Din1相同。然而,在高速数据的数据传输中,如图4所示,在输入数据Din1自低电平转为高电平的一开始,如图4中期间P1所示的波形,输出信号OUT0的第一笔输出数据的电平会太低以至于不清楚。相似地,在输入数据Din1自高电平转为低电平的一开始,如图4中期间P2所示的波形,输出信号OUT0的第一笔输出数据的电平会太高以至于不清楚。因此,在本发明内容中,判别电路120和芯片外前置驱动电路140能够根据信号补偿方法增强上拉控制信号PUP和下拉控制信号PDN,因此输入输出端I/O的输出信号能够更清楚(更少失真)。关于信号补偿方法将于以下段落叙明。

请参考图5。图5是根据本发明内容的部分实施例所绘示的一种芯片外前置驱动电路140的信号示意图。如图5所示,在部分实施例中,芯片外前置驱动电路140的第一可调变增强电路146和第二可调变增强电路148两者皆包含增强元件AEDp和AEDn。

具体而言,第一可调变增强电路146的增强元件AEDp用以接收和根据高电压VDD、输入数据Din1、一个或多个选择信号UP_Popt<1>~UP_Popt

相似地,第二可调变增强电路148的增强元件AEDp用以接收并根据高电压VDD、输入数据Din1、一个或多个选择信号DN_Popt<1>~DN_Popt

请参考图6。图6是根据本发明内容的部分实施例所绘示的一种补偿电路的示意图。在部分实施例中,可调变增强电路146和148皆可由如图6所示的相同电路所实施。举例来说,图6中增强元件AEDp可用以实现图5中的增强元件AEDp,而图6中增强元件AEDn可用以实现图5中的增强元件AEDn。

值得注意的是可调变增强电路146和148可包含一个或多个增强元件AEDp和AEDn。为了方便清楚说明起见,以下描述将先以一个增强元件AEDp包含一个开关SWp<1>和一个第一晶体管Mp<11>,一个增强元件AEDn包含一个开关SWn<1>和一个第二晶体管Mn<11>作为举例。此外,为了方便清楚说明,选择信号UP_Popt<1>~UP_Popt

在部分实施例中,如图6所示,增强元件AEDp包含与门ANDp、开关SWp<1>和第一晶体管Mp<11>。增强元件AEDn包含与门ANDn、开关SWn<1>和第二晶体管Mn<11>。如图6所示,开关SWp<1>由PMOS所实现,而开关SWn<1>由NMOS所实现,但本发明不以此为限。

结构上,与门ANDp和ANDn共同耦接至节点N1。与门ANDp耦接至第一开关SWp<1>,第一开关SWp<1>与第一晶体管Mp<11>串联连接,而第一晶体管Mp<11>耦接至前置驱动器的输出端(即,节点Pout)。相似地,与门ANDn耦接至第二开关SWn<1>,第二开关SWn<1>与第二晶体管Mn<11>串联连接,而第二晶体管Mn<11>耦接至前置驱动器的输出端(即,节点Nout)。

操作上,与门ANDp用以接收选择信号Popt<1>和第二判别信号DDN,以根据选择信号Popt<1>和第二判别信号DDN产生致能信号Pen<1>,并输出致能信号Pen<1>至第一开关SWp<1>的控制端。第一开关SWp<1>用以根据具有低电平的致能信号Pen<1>导通,而第一晶体管Mp<11>用以根据具有低电平的输入数据Din1导通,以提供高电压VDD作为控制信号PUP和PDN至芯片外驱动电路160。

相似地,与门ANDn用以接收选择信号Nopt<1>和第一判别信号DUP,以根据选择信号Nopt<1>和第一判别信号DUP产生致能信号Nen<1>,并输出致能信号Nen<1>至第二开关SWn<1>的控制端。第二开关SWn<1>用以根据具有高电平的致能信号Nen<1>导通,而第二晶体管Mn<11>用以根据具有高电平的输入数据Din1导通,以提供低电压VSS作为控制信号PUP和PDN至芯片外驱动电路160。

请一并参考图6和图7。图7是根据本发明内容的部分实施例所绘示的一种芯片外驱动电路100的信号示意图。为了便于说明起见,绘示于图6中的增强元件AEDp和AEDn的操作将配合图7中的信号进行说明。如图7所示,在期间P1,判别信号DUP和DDN位于高电平,选择信号Nopt<1>和Popt<1>也位于高电平。因此,由与门ANDp和ANDn所产生的致能信号Pen<1>和Nen<1>皆位于高电平,使得第一开关SWp<1>关断和第二开关SWn<1>导通。此外,在期间P1,输入数据Din1位于高电平,使得第一晶体管Mp<11>关断而第二晶体管Mn<11>导通。据此,在期间P1,增强元件AEDn提供低电压VSS作为上拉控制信号PUP和下拉控制信号PDN至芯片外驱动电路160,以增强上拉控制信号PUP和下拉控制信号PDN的转换速率,借以改善导通上拉电路162中P型晶体管以及关断下拉电路164中N型晶体管的能力。如此一来,对应于输入输出端I/O所感应的输出信号OUT1的电平能在期间P1提早变高。

相似地,在期间P2,判别信号DUP和DDN位于低电平,选择信号Nopt<1>和Popt<1>位于高电平。因此,由与门ANDp和ANDn所产生的致能信号Pen<1>和Nen<1>两者皆位在低电平,使得第一开关SWp<1>导通而第二开关SWn<1>关断。此外,在期间P2,输入数据Din1位于低电平,使得第一晶体管Mp<11>导通而第二晶体管Mn<11>关断。据此,在期间P2,增强元件AEDp提供高电压VDD作为上拉控制信号PUP和下拉控制信号PDN至芯片外驱动电路160,以增强上拉控制信号PUP和下拉控制信号PDN的转换速率,借以改善关断上拉电路162中P型晶体管以及导通下拉电路164中N型晶体管的能力。如此一来,对应于输入输出端I/O所感应的输出信号OUT1的电平能在期间P2提早变低。

因此,借由可调变增强电路增强上拉控制信号PUP和下拉控制信号PDN的转换速率,在输入数据Din1自低电平转为高电平或者高电平转为低电平的一开始,由芯片外驱动电路160对应于输入输出端I/O所感应的输出信号OUT1便能够清楚,如图7中期间P1和P2所示的波形。

在部分实施例中,由判别电路120根据输入数据Din1和时脉信号CLK产生第一判别信号DUP和第二判别信号DDN。值得注意的是时脉信号CLK仅为举例,在部分实施例中,判别电路120可在没有时脉信号CLK的情况下产生输入数据Din1、第一判别信号DUP和第二判别信号DDN。具体而言,判别电路120接收输入数据Din1并比较前一笔和下一笔输入数据的电压电平。当下一笔的输入数据的电压电平高于当前输入数据的电压电平,判别电路120便产生第一判别信号DUP的一个脉冲(如图7中期间P1的波行所示)。当下一笔的输入数据的电压电平低于当前输入数据的电压电平,判别电路120便产生第二判别信号DDN的一个脉冲(如图7中期间P2的波行所示)。在部分实施例中,判别电路120可由前馈均衡器(feed forwardequalizer,FFE)中的部分元件或前置强化判别电路中的部分元件所实现。

请参考图8A和图8B。图8A和图8B是根据本发明内容的部分实施例所绘示的一种第一开关SWp<1>的示意图。如图8A所示,在部分实施例中,开关SWp<1>可由搭配非门的NMOS所实现。具体而言,NMOS的第一端用以接收高电压VDD,NMOS的第二端耦接至第一晶体管Mp<11>,而NMOS的控制端用以经由非门接收致能信号Pen<1>。

而如图8B所示,在其他部分实施例中,开关SWp<1>可由互补式金属氧化物半导体双向开关(CMOS bilateral switch)所实现。具体而言,CMOS双向开关由PMOS、NMOS和非门所组成。PMOS的第一端和NMOS的第一端用以接收高电压VDD。PMOS的第二端和NMOS的第二端耦接至第一晶体管Mp<11>。PMOS的控制端用以接收致能信号Pen<1>,而NMOS的控制端用以经由非门接收致能信号Pen<1>。

请参考图9A和图9B。图9A和图9B是根据本发明内容的部分实施例所绘示的一种第二开关SWn<1>的示意图。如图9A所示,在部分实施例中,开关SWn<1>可由搭配非门的PMOS所实现。具体而言,PMOS的第一端用以接收低电压VSS,PMOS的第二端耦接至第二晶体管Mn<11>,而PMOS的控制端用以经由非门接收致能信号Nen<1>。

而如图9B所示,在其他部分实施例中,开关SWn<1>可由互补式金属氧化物半导体双向开关(CMOS bilateral switch)所实现。具体而言,CMOS双向开关由PMOS、NMOS和非门所组成。PMOS的第一端和NMOS的第一端用以接收低电压VSS。PMOS的第二端和NMOS的第二端耦接至第二晶体管Mn<11>。NMOS的控制端用以接收致能信号Nen<1>,而PMOS的控制端用以经由非门接收致能信号Nen<1>。

关于可调变增强电路146、148包含多个第一增强元件的实施例,请参考图10A和图10B。图10A和图10B是根据本发明内容的部分实施例所绘示的一种第一增强元件AEDp的示意图。在部分实施例中,在图6中的第一增强元件AEDp可由如图10A和图10B所示并联多个的第一增强元件AEDp所取代。为了容易理解,在图10A和图10B中,与图6的实施例中相似的元件将以相同符号标示,详细说明将不再赘述。此外,在图10A的实施例中,第一开关SWp<2>~SWp

如图10A所示,有一个或多个第一开关SWp<1>~SWp

例如,在部分实施例中,当Y=1,代表有一个第一增强元件AEDp,其包含一个与门、一个第一开关SWp<1>和一串第一晶体管Mp<11>~Mp

此外,值得注意的是,虽然绘示于图10A中的每个第一开关所连接的第一晶体管的数量是相同的(即,Z个第一晶体管),在其他部分实施例中,由不同的第一开关所连接的第一晶体管的数量是不同的。例如,连接至第一开关SWp<1>的第一晶体管Mp<11>可为一个,连接至第一开关SWp<2>的第一晶体管Mp<12>~Mp<22>可为两个,连接至第一开关SWp<3>的第一晶体管Mp<13>~Mp<43>可为四个。

操作上,第一开关SWp<1>用以根据具有低电平的致能信号Pen<1>导通,而致能信号Pen<1>是由与门根据相应具有高电平的选择信号Popt<1>和具有低电平的第二判别信号DDN所产生的。第一开关SWp<2>用以根据具有低电平的致能信号Pen<2>导通,而致能信号Pen<2>是由与门根据相应具有高电平的选择信号Popt<2>和具有低电平的第二判别信号DDN所产生的。依此类推,第一开关SWp

如此一来,借由调整选择信号Popt<1>~Popt

请参考图10B。在图10B的实施例中,相较于图10A的实施例,第一增强元件AEDp所包含的与门由多工器MUXp所取代。如图10B所示,第一开关SWp<1>的控制端耦接至多工器MUXp的输出端。多工器MUXp中具有“L”接脚的输入端耦接至高电压VDD。多工器MUXp中具有“H”接脚的输入端用以接收第二判别信号DDN。多工器MUXp的控制端用以接收第一选择信号Popt<1>。多工器MUXp用以根据第一选择信号Popt<1>输出自两个输入端所接收的两个信号中的一个。

举例来说,当第一选择信号Popt<1>如图7所示位于高电平,多工器MUXp输出具有“H”接脚的输入端的信号,使得当第二判别信号DDN位于低电平时,则致能信号Pen<1>位于低电平,如图7中期间P1的波形所示,而当第二判别信号DDN位于高电平时,则致能信号Pen<1>位于高电平。

此外,在其他部分实施例中,图10A中的与门ANDp亦能取代为或门(OR gate),并将高电平的选择信号Popt<1>~Popt

关于可调变增强电路146、148包含多个第二增强元件的实施例,请参考图11A和图11B。图11A和图11B是根据本发明内容的部分实施例所绘示的一种第二增强元件AEDn的示意图。在部分实施例中,在图6中的第二增强元件AEDn可由如图11A和图11B所示并联多个的第二增强元件AEDn所取代。为了容易理解,在图11A和图11B中,与图6的实施例中相似的元件将以相同符号标示,详细说明将不再赘述。此外,在图11A的实施例中,第二开关SWn<2>~SWn

如图11A所示,有一个或多个第二开关SWn<1>~SWn

例如,在部分实施例中,当Y=1,代表有一个第二增强元件AEDn,其包含一个与门、一个第二开关SWn<1>和一串第二晶体管Mn<11>~Mn

此外,值得注意的是,虽然绘示于图11A中的每个第二开关所连接的第二晶体管的数量是相同的(即,Z个第二晶体管),在其他部分实施例中,由不同的第二开关所连接的第二晶体管的数量是不同的。例如,连接至第二开关SWn<1>的第二晶体管Mn<11>可为一个,连接至第二开关SWn<2>的第二晶体管Mn<12>~Mn<22>可为两个,连接至第二开关SWn<3>的第二晶体管Mn<13>~Mn<43>可为四个。

操作上,第二开关SWn<1>用以根据具有高电平的致能信号Nen<1>导通,而致能信号Nen<1>是由与门根据相应具有高电平的选择信号Nopt<1>和具有高电平的第一判别信号DUP所产生的。第二开关SWn<2>用以根据具有高电平的致能信号Nen<2>导通,而致能信号Nen<2>是由与门根据相应具有高电平的选择信号Nopt<2>和具有高电平的第一判别信号DUP所产生的。依此类推,第二开关SWn

如此一来,借由调整选择信号Nopt<1>~Nopt

请参考图11B。在图11B的实施例中,相较于图11A的实施例,第二增强元件AEDn所包含的与门由多工器MUXn所取代。如图11B所示,第二开关SWn<1>的控制端耦接至多工器MUXn的输出端。多工器MUXn中具有“L”接脚的输入端耦接至低电压VSS。多工器MUXn中具有“H”接脚的输入端用以接收第一判别信号DUP。多工器MUXn的控制端用以接收第二选择信号Nopt<1>。多工器MUXn用以根据第二选择信号Nopt<1>输出自两个输入端所接收的两个信号中的一个。

举例来说,当第二选择信号Nopt<1>如图7所示位于高电平,多工器MUXn输出具有“H”接脚的输入端的信号,使得当第一判别信号DUP位于低电平时,则致能信号Nen<1>位于低电平,而当第一判别信号DUP位于高电平时,则致能信号Nen<1>位于高电平,如图7中期间P1的波形所示。

值得注意的是上述可调变增强电路146、148仅为举例,并非用以限制本案。可以产生信号(如,致能信号Pen<1>和Nen<1>)以控制第一晶体管Mp<1>和第二晶体管Mn<1>的任何电路或逻辑门的组合皆在本发明范围内。换言之,本领域具有通常知识者可调整可调变增强电路146和148的设计。

此外,虽然绘示于图10A和10B图中的第一选择信号Popt<1>~Popt

虽然本文将所公开的方法示出和描述为一系列的步骤或事件,但是应当理解,所示出的这些步骤或事件的顺序不应解释为限制意义。例如,部分步骤可以以不同顺序发生和/或与除了本文所示和/或所描述的步骤或事件以外的其他步骤或事件同时发生。另外,实施本文所描述的一个或多个实施例或实施例时,并非所有于此示出的步骤皆为必需。此外,本文中的一个或多个步骤也可能在一个或多个分离的步骤和/或阶段中执行。

需要说明的是,在不冲突的情况下,在本发明内容各个附图、实施例及实施例中的特征与电路可以相互组合。附图中所绘示的电路仅为示例之用,是简化以使说明简洁并便于理解,并非用以限制本案。此外,上述各实施例中的各个装置、单元及元件可以由各种类型的数位或类比电路实现,也可分别由不同的集成电路芯片实现,或整合至单一芯片。上述仅为例示,本发明内容并不以此为限。

综上所述,本发明通过应用上述各个实施例中,借由可调变增强电路146和148,控制信号PUP和PDN的上升和下降转换速率便能够提高,以改善输出信号OUT1上升和下降的转换速率,当输入数据DIN转换时,使得输出信号OUT1的输出数据能够清楚。此外,借由调整自芯片外前置驱动电路140所输出的选择信号(例如,UP_Popt<1>~UP_Popt

虽然本发明已经以实施方式公开如上,然其并非限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作各种变动与润饰,因此本发明的保护范围当视权利要求所界定者为准。

- 驱动器、芯片外驱动电路及其补偿系统和信号补偿方法

- 补偿栅极驱动电路信号线阻值的方法及应用该方法的液晶显示面板