数字控制延迟线及其方法

文献发布时间:2023-06-19 11:52:33

技术领域

本发明的实施例涉及数字控制延迟线及其方法。

背景技术

延迟线,包含数字控制延迟线(DCDL),为通过级联延迟级路由的输入信号提供可编程延迟时间。DCDL电路使用可经由控制信号配置的延迟级来实现,以使得输入信号或者传递到下一个延迟级,或者传播到返回路径。为获得给定延迟时间,激活预定数量的级联延迟级,以提供输入信号的前向和返回路径。

在一些情况下,DCDL包含在延迟锁相环(DLL)电路中,在DLL电路中可编程延迟时间用于同步时钟信号。

发明内容

根据本发明的一个方面,提供了一种数字控制延迟线,包括:输入端;输出端;以及多个级,被配置为将信号沿第一信号路径从输入端传播到多个级的可选返回级,并且沿第二信号路径从多个级的返回级传播到输出端。多个级中的每一级都包括:第一反相器和第二反相器,被配置为选择性将信号沿第一信号路径传播;第三反相器和第四反相器,被配置为选择性将信号沿第二信号路径传播;以及第五反相器,被配置为选择性将信号从第一信号路径传播到第二信号路径。

根据本发明的另一个方面,提供了一种数字控制延迟线,包括:输入端;输出端;以及多个级,被配置为将信号沿第一信号路径从输入端传播到多个级的可选返回级,并且沿第二信号路径从多个级的返回级传播到输出端。多个级中的每一级都包括:第一反相器,被配置为选择性将信号沿第一信号路径传播;第二反相器,被配置为选择性将信号沿第二信号路径传播;以及第三反相器和第四反相器,串联耦合并且被配置为选择性将信号从第一信号路径传播到第二信号路径。

根据本发明的又一个方面,提供了一种控制信号延迟时间的方法,方法包括:在数字控制延迟线的多个顺序耦合级的第一级处接收输入信号;以及选择多个顺序耦合级的第二级作为返回级,从而激活第二级的第一可调反相器作为数字控制延迟线的信号延迟路径的部分,其中,对于多个顺序耦合级的每一级,选择第二级作为返回级包括激活信号延迟路径中的给定可调反相器,给定可调反相器被配置为接收具有与输入信号的信号转换的极性相同极性的信号转换,给定可调反相器是第二级的第一可调反相器或另一个激活的可调反相器。

附图说明

当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各方面。应该注意,根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

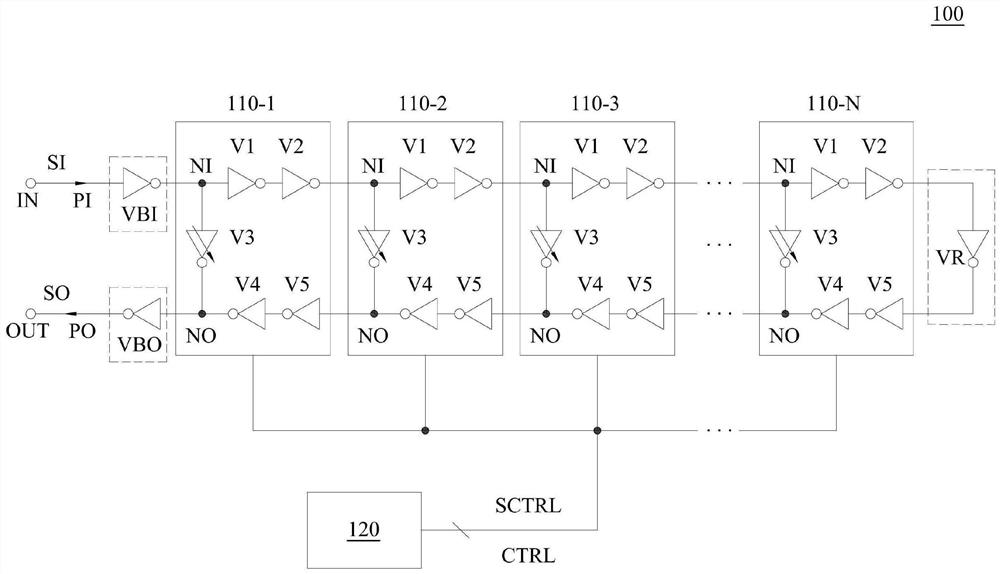

图1是根据一些实施例的DCDL电路的示意图。

图2是根据一些实施例的DCDL电路的示意图。

图3是根据一些实施例的DCDL电路的示意图。

图4是根据一些实施例的反相器的示意图。

图5是根据一些实施例的可调反相器的示意图。

图6是根据一些实施例的控制信号延迟时间的方法的流程图。

图7是根据一些实施例的DCDL电路操作参数的表示。

图8A和图8B是根据一些实施例的可调反相器的示意图。

图9A-图9D是根据一些实施例的DCDL电路的示意图。

图10是根据一些实施例的控制信号延迟时间的方法的流程图。

图11是根据一些实施例的DLL电路的示意图。

具体实施方式

以下公开内容提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面描述了组件、值、操作、材料、布置等的具体示例以简化本发明。当然,这些仅仅是实例,而不旨在限制本发明。可以设想其它的部件、值、操作、材料、布置等。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可在各个实例中重复参考标号和/或字符。该重复是为了简单和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

而且,为了便于描述,在此可以使用诸如“在…之下”、“在…下方”、“下部”、“在…之上”、“上部”等空间相对术语,以描述如图所示的一个元件或部件与另一个(或另一些)元件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的不同方位。器件可以以其他方式定向(旋转90度或在其他方位上),而本文使用的空间相对描述符可以同样地作出相应的解释。

在各种实施例中,DCDL接收给定的上升或下降信号转换中之一,并且被配置为使对应于可编程延迟时间范围的每个信号路径包含接收给定信号转换的可调延迟单元。通过始终包含在可编程延迟时间范围内接收相同信号转换极性的可调延迟单元,与每个信号路径不包含接收相同信号转换的可调延迟单元的方法相比,DCDL能够改善延迟时间控制,从而增加延迟时间的线性。

在一些实施例中,DCDL包含单侧可调延迟单元,该单侧可调延迟单元被配置为通过使用与其中可调延迟单元被配置为对上升和下降信号转换都实现可编程延迟时间的方法相比更少的晶体管,来实现给定的上升或下降信号转换中之一的可编程延迟时间,从而减小电路尺寸、复杂度,以及工艺变化影响。

图1是根据一些实施例的DCDL电路100的示意图。DCDL电路100,在一些实施例中也被称为DCDL 100,它是一种集成电路(IC),包含输入端IN、输出端OUT、级110-1...110-N、控制电路120,以及控制信号总线CTRL。在各种实施例中,如下面将论述的,DCDL电路100包含输入缓冲器VBI、输出缓冲器VBO或返回反相器VR中的一个或多个。在一些实施例中,DCDL电路100是另一个电路的一部分,例如下面参照图11论述的DLL电路1100。

级110-1耦合到输入端IN和输出端OUT中的每一个,级110-1...110-N以级联配置顺序地彼此耦合,并且级110-1...110-N中的每一级通过控制信号总线CTRL耦合到控制电路120。级110-1...110-N因此被配置为耦合到输入端IN和输出端OUT的第一到至N顺序耦合级。

两个或多个电路元件被认为是基于包含一个或多个附加电路元件(例如,一个或多个切换器件或者一个或多个逻辑门或传输门)的直接电连接或导电路径来耦合的,并且因此能够被控制,例如,由晶体管或其他切换器件使其成为电阻性的或开路的。

在一些实施例中,DCDL电路(例如,DCDL电路100)包含N个级,例如级110-1...110-N,范围从16至128。在一些实施例中,DCDL电路(例如,DCDL电路100)包含N个级,例如级110-1...110-N,范围从32至64。在一些实施例中,DCDL电路(例如,DCDL电路100)包含N个级,例如级110-1...110-N,少于16或多于128。

DCDL电路100被配置为于输入端IN处接收信号SI,并且级110-1...110-N被配置为通过响应于在控制信号总线CTRL上接收到并由控制电路120生成的控制信号SCTRL来将可编程延迟时间应用到信号SI,从而于输出端OUT处返回信号SO。输入端IN以及级110-1...110-N的可选部分因此被配置为输入路径PI,并且级110-1...110-N的可选部分以及输出端OUT因此被配置为输出路径PO。

级(例如,级110-1...110-N中之一),在一些实施例中也被称为延迟级,它是一种包含多个单元(例如,反相器)的电子电路,可响应于多个控制信号(例如,控制信号SCTRL)配置,以便选择性激活在输入路径PI和输出路径PO之间耦合的至少一个单元,或者选择性激活输出路径PO中耦合到下一个顺序耦合级的至少一个单元和输入路径PI中耦合到下一个顺序耦合级的至少一个单元。

级110-1...110-N中的每一级都包含节点NI和沿输入路径PI串联耦合的反相器V1和V2、节点NO和沿输出路径PO串联耦合的反相器V4和V5,以及于相应节点NI和NO处在输入路径PI和输出路径PO之间耦合的可调反相器V3。

在图1所示的实施例中,可调反相器V3于输入端IN与反相器V1和V2之间的节点NI处耦合到输入路径PI,并且于输出端OUT与反相器V4和V5之间的节点NO处耦合到输出路径PO。在一些实施例中,可调反相器V3于反相器V1和V2之间的节点NI处耦合到输入路径PI,并且于反相器V4和V5之间的节点NO处耦合到输出路径PO。在一些实施例中,可调反相器V3于节点NI处耦合到输入路径PI,使得反相器V1和V2位于输入端IN和节点NI之间,并且于节点NO处耦合到输出路径PO,使得反相器V4和V5位于输出入端OUT和节点NO之间。

反相器V1、V2、V4以及V5中的每一个,在一些实施例中也被称为粗调延迟单元,是被配置为响应于在控制信号总线CTRL上接收的一个或多个控制信号SCTRL而具有激活或未激活状态的三态反相器。在激活状态下,三态反相器(例如反相器V1、V2、V4或V5)被配置为生成与接收到的输入信号互补的输出信号,并且具有输入信号中的转换和输出信号中的最终转换之间的延迟时间,该延迟时间由反相器的切换速度控制。在未激活状态下,三态反相器(例如反相器V1、V2、V4或V5)被配置为具有独立于接收到的输入信号的高输出阻抗。

未激活状态的高输出阻抗对应于三态反相器的第一输出状态,响应于具有低电压电平的输入信号而具有高电压电平的输出信号对应于第二输出状态,响应于具有高电压电平的输入信号而具有低电压电平的输出信号对应于第三输出状态。

在一些实施例中,三态反相器(例如,反相器V1、V2、V4或V5)包含在电源节点和参考节点(例如,接地节点)(图1中未示出)之间串联耦合的多个p型和多个n型晶体管,并且因此被配置为在操作中具有与响应于控制信号而被断开的第一互补晶体管对(图1中未示出)相对应的未激活状态,具有与响应于控制信号而被接通的第一互补晶体管对相对应的激活状态,以及响应于于第二互补晶体管对的栅极处接收到的输入信号而输出输出信号。在一些实施例中,反相器V1、V2、V4或V5中的一个或多个是下面参照图4论述的三态反相器400。

可调反相器V3,在一些实施例中也被称为微调延迟单元,是被配置为响应于在控制信号总线CTRL上接收到的一个或多个控制信号SCTRL而具有一个未激活状态或多个激活状态中之一的反相器。在多个激活状态的每一个中,可调反相器(例如,可调反相器V3)被配置为生成与接收到的输入信号互补的输出信号,并且具有对应于多个激活状态中所选多个激活状态之一的切换速度。对应于所选激活状态的切换速度控制输入信号中的转换和输出信号中的最终转换之间的延迟时间,使得可调反相器具有对应于多个激活状态的多个延迟时间。

未激活状态的高输出阻抗对应于可调反相器的第一输出状态,响应于具有低电压电平的输入信号而具有高电压电平和第一切换速度的输出信号对应于第二输出状态,响应于具有高电压电平的输入信号而具有低电压电平和第一切换速度的输出信号对应于第三输出状态,以及响应于具有相应的低或高电压电平的输入信号而具有高或低电压电平和至少一个附加切换速度的输出信号对应于具有多于三个输出状态的可调反相器。

在一些实施例中,可调反相器(例如,可调反相器V3)包含如上面参照三态反相器所讨论的那样配置的多个p型和n型晶体管,并且还包含与多个p型和n型晶体管中相同类型晶体管并联布置的至少一个附加p型或n型晶体管。可调反相器因此被配置为在操作中具有与响应于控制信号而被接通和断开的并联晶体管的组合相对应的多个激活状态。在各种实施例中,可调反相器V3是下面参照图5论述的可调反相器500,或者是下面参照图8A和图8B论述的可调反相器800A或800B中之一。

控制电路120是一种被配置为生成和输出控制信号SCTRL的电子电路,该控制信号SCTRL被配置为使得第n级110-n(级110-1...110-N中的任何一个)的可调反相器V3具有预定的激活状态之一,并且使得每个其他级110-1...110-N的可调反相器V3具有无效状态,从而选择级110-n作为返回级,在操作中,通过该返回级,输入路径PI上的信号SI被传播到输出路径PO并生成信号SO。在一些实施例中,DCDL电路100包含返回反相器VR,并且控制电路120被配置为生成和输出控制信号SCTRL,该控制信号SCTRL被可选地配置为使得每一级110-1...110-N的可调反相器V3具有无效状态,从而使返回反相器VR在操作中将信号SI从输入路径PI传播到输出路径PO并生成信号SO。

控制电路120被配置为生成并输出控制信号SCTRL,该控制信号SCTRL被配置为进一步使得所选返回级(或返回反相器VR)的输入端IN和节点NI之间的每个反相器V1和每个反相器V2,以及所选返回级(或返回反相器VR)的输出端OUT和节点NO之间的每个反相器V4和每个反相器V5都具有有效状态。在各种实施例中,对于给定的级110-1...110-N中之一,反相器V1和V2被配置为接收同一组的控制信号SCTRL或不同组的控制信号SCTRL,并且反相器V4和V5被配置为接收同一组的控制信号SCTRL或不同组的控制信号SCTRL。

在操作中,在所选返回级(或返回反相器VR)的输入端IN和节点NI之间的激活的反相器V1和V2因此被配置为一些或全部输入路径PI,并且在所选返回级(或返回反相器VR)的节点NO和输出端OUT之间的激活的反相器V4和V5因此被配置为一些或全部输出路径PO。输入路径PI、所选返回级的可调反相器V3,以及输出路径PO因此被配置为DCDL 100的信号延迟路径。

在操作中,除非选择图1中所示的级110-1作为返回级,否则级110-1的反相器V1于节点NI处接收信号SI中的转换,并将接收到的转换作为被反相器V1的延迟时间延迟的反相转换沿输入路径PI传播到级110-1的反相器V2。相反,反相器V2将接收到的信号SI中的转换作为被反相器V2的延迟时间延迟的反相转换沿输入路径PI传播到级110-2的节点NI。沿输入路径PI,对每个激活的反相器V1和V2重复这种传播顺序。

所选返回级(或返回反相器VR)的可调反相器V3于输入路径PI上的节点NI处接收信号SI中的最终转换,并将该最终转变作为被可调反相器V3的延迟时间延迟的反相转换传播到输出路径PO的节点NO,该可调反相器V3的延迟时间对应于由控制信号SCTRL(或返回反相器VR的延迟时间)确定的预定有效状态之一。

在类似于输入路径PI的顺序中,来自所选返回级的可调反相器V3的反相转换由沿输出路径PO的每个激活反相器V4和V5作为被相应反相器V4或V5的延迟时间延迟的反相转换沿输出路径PO传播。

在操作中,在输出端OUT上因此生成信号SO,该信号SO包含相对于信号SI中的转换而被延迟了总延迟时间的转换,该总延迟时间基于以下各项的总和:输入路径PI中反相器V1和V2的每一个的延迟时间、输出路径PO中反相器V4和V5的每一个的延迟时间,以及所选返回级的可调反相器V3的延迟时间。在DCDL电路100包含返回反相器VR和没有被选择作为返回级的级110-1...110-N的一些实施例中,总延迟时间基于以下各项的总和:输入路径PI中反相器V1和V2的每一个的延迟时间、输出路径PO中反相器V4和V5的每一个的延迟时间,以及返回反相器VR的延迟时间。

在操作中,在一些实施例中,具有相对于信号SI中的转换的极性的信号SO中的转换基于以下各项的总数:包含在输入路径PI中的反相器的数量、包含在输出路径PO中的反相器的数量,以及所选返回级的可调反相器V3或返回反相器VR。因此,为奇数的反相器总数对应于具有与信号SI相反的转换极性的信号SO,为偶数的反相器总数对应于具有与信号SI相同的转换极性的信号SO。

在一些实施例中,DCDL电路100既不包含输入缓冲器VBI也不包含输出缓冲器VBO,并且反相器的总数是奇数,等于以下各项的总和:包含在输入路径PI中的反相器V1和V2的数量、包含在输出路径PO中的反相器V4和V5的数量,加上所选返回级的可调反相器V3或返回反相器VR。在操作中,在这种实施例中,于输入端IN处接收到的具有给定极性的信号SI中的转换因此使得输出端OUT的信号SO具有相反极性的转换,并且被延迟了总延迟时间,该总延迟时间等于以下各项的总和:输入路径PI中反相器V1和V2的每一个的延迟时间、输出路径PO中反相器V4和V5的每一个的延迟时间,以及所选返回级的可调反相器V3的延迟时间或返回反相器VR的延迟时间。

在一些实施例中,DCDL电路100包含输入缓冲器VBI或输出缓冲器VBO之一,并且反相器的总数是偶数,等于以下各项的总和:包含在输入路径PI中的反相器V1和V2的数量、包含在输出路径PO中的反相器V4和V5的数量、所选返回级的可调反相器V3或返回反相器VR,加上输入缓冲器VBI或输出缓冲器VBO之一。在操作中,在这种实施例中,于输入端IN处接收到的具有给定极性的信号SI中的转换因此使得输出端OUT的信号SO具有相同极性的转换,并且被延迟了总延迟时间,该总延迟时间等于以下各项的总和:输入路径PI中反相器V1和V2的每一个的延迟时间、输出路径PO中反相器V4和V5的每一个的延迟时间,所选返回级的可调反相器V3的延迟时间或返回反相器VR的延迟时间,加上输入路径PI中输入缓冲器VBI或输出路径PO中输出缓冲器VBO的延迟时间。

在操作中,反相器(例如,反相器V1、V2、V4或V5或可调反相器V3中之一)的延迟时间是基于当响应于上升输入信号转换而生成下降输出信号转换时一个或多个n型晶体管的切换速度,并且基于当响应于下降输入信号转换而生成上升输出信号转换时一个或多个p型晶体管的切换速度。因此,在为可调反相器V3的情况下,多个延迟时间的控制是基于当响应上升输入信号转换时多个n型晶体管的切换速度或当响应下降输入信号转换时多个p型晶体管的切换速度。

通过上述配置,DCDL电路100中每一级110-1...110-N的可调晶体管V3被配置为接收具有相同转换极性的输入信号。对于基于所选返回级的DCDL电路100中的每个可编程延迟时间,由相应可调反相器V3提供的延迟时间分量的控制因此基于作为相同类型晶体管的多个晶体管的切换速度。

晶体管切换速度根据制造工艺变化而变化,使得相同类型晶体管之间的切换速度变化通常小于不同类型晶体管之间的切换速度变化。可调反相器V3具有基于相同晶体管切换速度的延迟时间,通过将每个可编程延迟时间配置为基于这种可调反相器V3,与每个可编程延迟时间不基于相同晶体管切换速度的方法相比,能够改进DCDL电路100对延迟时间的控制,从而增加延迟时间线性度。

图2是根据一些实施例的DCDL电路200的示意图。DCDL电路200,在一些实施例中也被称为DCDL 200,它是一种集成电路(IC),包含输入端IN、输出端OUT、控制电路120、控制信号总线CTRL,每一个都在上面参照图1进行了论述。代替级110-1...110-N和返回反相器VR,在一些实施例中,DCDL电路200包含级210-1...210-N,以及返回路径PR。在各种实施例中,DCDL电路200包含输入缓冲器VBI或输出缓冲器VBO之一,每一个都在上面参照图1进行了论述。在一些实施例中,DCDL电路200是另一个电路的一部分,例如下面参照图11论述的DLL电路1100。

以上面参照图1论述的方式布置DCDL电路200的级210-1...210-N,并且DCDL 200因此被配置为于输入端IN处接收信号SI,并且级210-1...210-N被配置为通过响应于在控制信号总线CTRL上接收到的并由控制电路120生成的控制信号SCTRL,将可编程延迟时间应用到信号SI,而于输出端OUT处返回信号SO。输入端IN以及级210-1...210-N的可选部分因此被配置为输入路径PI,并且级210-1...210-N的可选部分以及输出端OUT因此被配置为输出路径PO。

级210-1...210-N的每一级都包含节点NI和NO、反相器V1和V5,以及可调反相器V3,每一个都在上面参照图1进行了论述。与级110-1...110-N相比,级210-1...210-N中的每一级都不包含与反相器V1串联的反相器V2或与反相器V5串联的反相器V4,而替代地包含于节点NI和节点NO之间的节点NS处与可调反相器V3串联耦合的可调反相器V6。在各种实施例中,可调反相器V6是下面参照图5论述的可调反相器500,或者是下面参照图8A和8B论述的可调反相器800A或800B中之一。

在图2所示的实施例中,可调反相器V3于输入端IN与反相器V1之间的节点NI处耦合到输入路径PI,并且可调反相器V6于输出端OUT与反相器V5之间的节点NO处耦合到输出路径PO。在一些实施例中,可调反相器V3于节点NI处耦合到输入路径PI,使得反相器V1位于输入端IN和节点NI之间,并且可调反相器V6于节点NO处耦合到输出路径PO,使得反相器V5位于输出端OUT和节点NO之间。

以上面参照图1论述的方式,包含控制电路120的DCDL电路200被配置为选择级210-1...210-N中第n级作为返回级,同时激活所选返回级的输入端IN和节点NI之间的每个反相器V1,并且激活所选返回级和输出端OUT之间的每个反相器V5,从而在操作中配置信号延迟路径,该信号延迟路径包含输入路径PI、返回路径以及输出路径PO,其中输入路径PI包含激活的反相器V1,返回路径包含可调反相器V3和V6,以及输出路径PO包含激活的反相器V5。

在操作中,除非选择图2中所示的级210-1作为返回级,否则级210-1的反相器V1于节点NI处接收信号SI中的转换,并将接收到的转换作为被反相器V1的延迟时间延迟的反相转换沿输入路径PI传播到级210-2的节点NI。沿输入路径PI,对每个激活的反相器V1重复这种传播顺序。

所选返回级的可调反相器V3于输入路径PI上的节点NI处接收信号SI中的最终转换,并且将该最终转换作为被可调反相器V3的延迟时间延迟的反相转换于节点NS处传播到相应可调反相器V6,然后相应可调反相器V6将从节点NS接收到的反相转换作为被可调反相器V6的延迟时间延迟的另一个反相转换传播到输出路径PO的节点NO。在一些实施例中,DCDL电路200被配置为通过激活级210-1...210-N中每一级的反相器V1和V5来选择返回路径PR,其中,在操作中,信号SI被直接从输入路径PI传播到输出路径PO上的信号SO,而无需被可调反相器V3和V6的延迟时间延迟。

所选返回级的可调反相器V3和V6的延迟时间对应于由控制信号SCTRL确定的预定有效状态之一。在各种实施例中,级210-1...210-N中的每一级的可调反相器V3和V6被配置为接收同一组的控制信号SCTRL或不同组的控制信号SCTRL。

相反,来自所选返回级的可调反相器V6的反相转换由沿输出路径PO的每个激活反相器V5作为被相应反相器V5的延迟时间延迟的反相转换沿输出路径PO传播。

在操作中,在输出端OUT上因此生成信号SO,该信号SO包含相对于信号SI中的转换而被延迟了总延迟时间的转换,该总延迟时间基于以下各项的总和:输入路径PI中每个反相器V1的延迟时间、输出路径PO中每个反相器V5的延迟时间,以及所选返回级的可调反相器V3和V6的延迟时间。在DCDL电路100包含返回路径PR和没有被选择作为返回级的级110-1...110-N的一些实施例中,总延迟时间基于以下各项的总和:输入路径PI中每个反相器V1的延迟时间,以及输出路径PO中每个反相器V5的延迟时间。

在操作中,基于包含在输入路径PI中、输出路径PO中的反相器数量,以及所选返回级中可调反相器V3和V6的数量的总数,信号SO中的转换具有相对于信号SI中的转换的极性,使得为奇数的反相器总数对应于具有与信号SI中相反的转换极性的信号SO,并且为偶数的反相器总数对应于具有与信号SI相同的转换极性的信号SO。

在一些实施例中,DCDL电路100既不包含输入缓冲器VBI也不包含输出缓冲器VBO,并且反相器的总数是奇数,等于以下各项的总和:包含在输入路径PI中的反相器V1的数量、包含在输出路径PO中的反相器V5的数量,加上所选返回级的可调反相器V3和V6。在操作中,在这种实施例中,于输入端IN处接收到的具有给定极性的信号SI中的转换因此使得输出端OUT的信号SO具有相同极性的转换,并且被延迟了总延迟时间,该总延迟时间等于以下各项的总和:输入路径PI中每个反相器V1的延迟时间、输出路径每个PO中反相器V5的延迟时间,以及所选返回级的可调反相器V3和V6的延迟时间。

在一些实施例中,DCDL电路100包含输入缓冲器VBI或输出缓冲器VBO之一,并且反相器的总数是偶数,等于以下各项的总和:包含在输入路径PI中的反相器V1的数量、包含在输出路径PO中的反相器V5的数量、所选返回级的可调反相器V3和V6,加上输入缓冲器VBI或输出缓冲器VBO之一。在操作中,在这种实施例中,于输入端IN处接收到的具有给定极性的信号SI中的转换因此使得输出端OUT的信号SO具有相反极性的转换,并且被延迟了总延迟时间,该总延迟时间等于以下各项的总和:输入路径PI中每个反相器V1的延迟时间、输出路径PO中每个反相器V5的延迟时间、所选返回级的可调反相器V3和V6的延迟时间,加上输入路径PI中输入缓冲器VBI或输出路径PO中输出缓冲器VBO的延迟时间。

通过上述配置,DCDL电路200中每一级210-1...210-N的可调晶体管V3和V6都被配置为共同接收具有两种转换极性的输入信号。对于基于所选返回级的DCDL电路200中每个可编程延迟时间,由相应可调反相器V3和V6提供的延迟时间分量的控制因此基于第一多个p型晶体管和第二多个n型晶体管的切换速度。

可调反相器V3和V6具有基于每个晶体管类型的切换速度的延迟时间,通过将每个可编程延迟时间配置为基于这种可调反相器V3和V6,与每个可编程延迟时间不基于每个晶体管切换速度的方法相比,能够改进DCDL电路200对延迟时间的控制,从而增加延迟时间线性度。

图3是根据一些实施例的DCDL电路300的示意图。DCDL电路300,在一些实施例中也被称为DCDL 300,它是一种集成电路(IC),包含输入端IN、输出端OUT、控制电路120、控制信号总线CTRL,以及返回反相器VR,每一个都在上面参照图1进行了论述。代替级110-1...110-N,DCDL电路300包含级310-1...310-N。在各种实施例中,DCDL电路300包含输入缓冲器VBI或输出缓冲器VBO之一,每一个都在上面参照图1进行了论述。在一些实施例中,DCDL电路300是另一个电路的一部分,例如下面参照图11论述的DLL电路1100。

以上面参照图1论述的方式布置DCDL电路300的级310-1...310-N,并且DCDL 300因此被配置为于输入端IN处接收信号SI,并且级310-1...310-N被配置为通过响应于在控制信号总线CTRL上接收到的并由控制电路120生成的控制信号SCTRL,将可编程延迟时间应用到信号SI,而于输出端OUT处返回信号SO。输入端IN以及级310-1...310-N的可选部分因此被配置为输入路径PI,并且级310-1...310-N的可选部分以及输出端OUT因此被配置为输出路径PO。

级310-1...310-N的每一级都包含节点NI和NO、反相器V5,以及可调反相器V3,每一个都在上面参照图1进行了论述。与级110-1...110-N相比,级310-1...310-N中每一个都不包含与反相器V5串联的反相器V4,并且包含可调反相器V7,并非反相器V1和V2。在一些实施例中,可调反相器V7是下面参照图5论述的可调反相器500,或者是下面参照图8A和图8B论述的可调反相器800A或800B中之一。

在图3所示的实施例中,可调反相器V3于输入端IN与反相器V7之间的节点NI处耦合到输入路径PI,并且于输出端OUT与反相器V5之间的节点NO处耦合到输出路径PO。在一些实施例中,可调反相器V3于节点NI处耦合到输入路径PI,使得反相器V7位于输入端IN和节点NI之间,并且于节点NO处耦合到输出路径PO,使得反相器V5位于输出入端OUT和节点NO之间。

以上面参照图1论述的方式,包含控制电路120的DCDL电路300被配置为选择级310-1...310-N中第n级作为返回级(或在一些实施例中,作为返回反相器VR),同时激活所选返回级的输入端IN和节点NI之间的每个反相器V7,并且激活所选返回级和输出端OUT之间的每个反相器V5,从而在操作中配置信号延迟路径,该信号延迟路径包含输入路径PI、返回路径以及输出路径PO,其中输入路径PI包含激活的反相器V7,返回路径包含可调反相器V3(或返回反相器VR),以及输出路径PO包含激活的反相器V5。

在操作中,除非选择图3中所示的级310-1作为返回级,否则级310-1的可调反相器V7于节点NI处接收信号SI中的转换,并将接收到的转换作为被可调反相器V7的延迟时间延迟的反相转换沿输入路径PI传播到级310-2的节点NI。沿输入路径PI,对每个激活的反相器V7重复这种传播顺序。

所选返回级(或返回反相器VR)的可调反相器V3于输入路径PI上的节点NI处接收信号SI中的最终转换,并将该最终转变作为被可调反相器V3的延迟时间延迟的反相转换传播到输出路径PO的节点NO。

输入路径PI的可调反相器V7和所选返回级的可调反相器V3的延迟时间对应于由控制信号SCTRL确定的预定有效状态之一(或者对应于返回反相器VR的延迟时间,而不是可调反相器V3的延迟时间)。

相反,来自所选返回级的可调反相器V3的反相转换由沿输出路径PO的每个激活反相器V5作为被相应反相器V5的延迟时间延迟的反相转换沿输出路径PO传播。

在操作中,在输出端OUT上因此生成信号SO,该信号SO包含相对于信号SI中的转换而被延迟了总延迟时间的转换,该总延迟时间基于以下各项的总和:输入路径PI中每个反相器V7的延迟时间、输出路径PO中每个反相器V5的延迟时间,以及所选返回级的可调反相器V3的延迟时间(或返回反相器VR的延迟时间)。基于包含在输入路径PI中、输出路径PO中的反相器数量,以及所选返回级中可调反相器V3的数量(或返回反相器VR的数量)的总数,信号SO中的转换具有相对于信号SI中的转换的极性,使得为奇数的反相器总数对应于具有与信号SI相反的转换极性的信号SO,并且为偶数的反相器总数对应于具有与信号SI相同的转换极性的信号SO。

在一些实施例中,DCDL电路300既不包含输入缓冲器VBI,也不包含输出缓冲器VBO,并且反相器的总数是奇数,等于以下各项的总和:包含在输入路径PI中的可调反相器V7的数量、包含在输出路径PO中的反相器V5的数量,加上所选返回级的可调反相器V3(或返回反相器VR)。在操作中,在这种实施例中,于输入端IN处接收到的具有给定极性的信号SI中的转换因此使得输出端OUT的信号SO具有相反极性的转换,并且被延迟了总延迟时间,该总延迟时间等于以下各项的总和:输入路径PI中每个反相器V7的延迟时间、输出路径PO中每个反相器V5的延迟时间,以及所选返回级的可调反相器V3的延迟时间(或返回反相器VR的延迟时间)。

在一些实施例中,DCDL电路300包含输入缓冲器VBI或输出缓冲器VBO之一,并且反相器的总数是偶数,等于以下各项的总和:包含在输入路径PI中的反相器V7的数量、包含在输出路径PO中的反相器V5的数量、所选返回级的可调反相器V3(或返回反相器VR),加上输入缓冲器VBI或输出缓冲器VBO之一。在操作中,在这种实施例中,于输入端IN处接收到的具有给定极性的信号SI中的转换因此使得输出端OUT的信号SO具有相同极性的转换,并且被延迟了总延迟时间,该总延迟时间等于以下各项的总和:输入路径PI中每个反相器V7的延迟时间、输出路径PO中每个反相器V5的延迟时间,所选返回级的可调反相器V3的延迟时间(或返回反相器VR的延迟时间),加上输入路径PI中输入缓冲器VBI或输出路径PO中输出缓冲器VBO的延迟时间。

通过上述配置,DCDL电路300中每一级310-2...310-N的可调晶体管V3和每个相应顺序耦合级310-1...310-N-1的可调反相器V7都被配置为共同接收具有两种转换极性的输入信号。对于基于选自级310-2...310-N的返回级的DCDL电路300中的每个可编程延迟时间,由相应可调反相器V3和V7提供的延迟时间分量的控制因此基于第一多个p型晶体管和第二多个n型晶体管的切换速度。

可调反相器V3和V6具有基于每个晶体管类型的切换速度的延迟时间,通过将在相应级310-2...310-N范围内的每个可编程延迟时间配置为基于这种可调反相器V3和V6,与在相应范围内的每个可编程延迟时间不基于每个晶体管的切换速度的方法相比,能够改进DCDL电路300对延迟时间的控制,从而增加延迟时间线性度。

图4是根据一些实施例的三态反相器400的示意图。三态反相器400可用作上面参照图1-图3论述的以及下面参照图9A-图9D论述的反相器V1、V2、V4或V5中的一个或多个。

三态反相器400包含被配置为承载电源电压(未标记)的电源节点VDD、被配置为承载参考电压(例如,接地电压)(未标记)的参考节点VSS、互补晶体管对PS/NS,以及互补晶体管对P1/N1。

p型晶体管PS耦合到电源节点VDD,n型晶体管NS耦合到参考节点VSS,以及晶体管PS和NS中的每一个的栅极耦合到被配置为接收输入信号400SI的输入端400I。

p型晶体管P1和n型晶体管N1在互补晶体管对PS/NS之间串联耦合,晶体管P1和N1中的每一个的栅极耦合到上面参照图1论述的控制信号总线CTRL,以及晶体管P1和N1的源极端于输出端400O处耦合在一起。晶体管P1的栅极被配置为接收控制信号SC1,并且晶体管N1的栅极被配置为接收与控制信号SC1互补的控制信号SC1b,控制信号SC1和SC1b是由控制电路120生成的一组控制信号SCTRL,在上面参照图1-3进行了论述。

在操作中,晶体管P1和N1因此被配置为响应于具有高电压电平的控制信号SC1和具有低电压电平的控制信号SC1b而被断开,从而对应于上面参照图1-图3论述的三态反相器400的未激活状态。响应于具有低电压电平的控制信号SC1和具有高电压电平的控制信号SC1b,晶体管P1和N1在操作中被接通,从而对应于上述激活状态,其中,三态反相器400被配置为在输出节点400O上生成输出信号400SO,该输出信号400SO与输入信号400SI互补且具有对应于晶体管PS、P1、NS以及N1的切换速度的延迟时间。

如上面参照图1-图3和下面参照图9A-图9D所论述的,包含三态反相器400的DCDL电路100-300或900A-900D因此能够生成包含三态反相器400延迟时间的总延迟时间,该总延迟时间具有上面参照DCDL电路100-300和下面参照DCDL电路900A-900D论述的那些优点。

图5是根据一些实施例的可调反相器500的示意图。可调反相器500可用作上面参照图1-图3论述的可调反相器V3、V6或V7中的一个或多个。

可调反相器500包含电源节点VDD、参考节点VSS,以及互补晶体管对PS/NS和P1/N1,它们如上面参照图4论述的那样布置。晶体管PS和NS中的每一个的栅极耦合到被配置为接收输入信号500SI的输入端500I,并且晶体管P1和N1的源极端耦合到输出端500O。

晶体管P1是并联布置在调谐部分500TP中的数量为K的p型晶体管P1-PK中的一个p型晶体管,并且晶体管N1是并联布置在调谐部分500TP中的数量为K的n型晶体管N1-NK中的一个n型晶体管。晶体管P1-PK和N1-NK中的每一个的栅极耦合到上面参照图1-4论述的控制信号总线CTRL,如上面参照图1-图4所论述的,晶体管P1-PK因此被配置为接收控制信号SF1-SFK,并且晶体管N1-NK因此被配置为接收与相应控制信号SF1-SFK互补的控制信号SF1b-SFKb,控制信号SF1-SFK和SF1b-SFKb是由控制电路120生成的一组控制信号SCTRL。

在各种实施例中,数量K等于2,使得可调反相器500在调谐部分500TP中总共包含两个p型和两个n型晶体管,数量K等于3,使得可调反相器500在调谐部分500TP中总共包含三个p型和三个n型晶体管,或者数量K大于3,使得可谐反相器500在调谐部分500TP中总共包含多于三个p型晶体管和多于三个n型晶体管。

在操作中,多个由P1-PK和相应N1-NK组成的晶体管对因此被配置为响应于具有高电压电平的相应控制信号SF1-SFK和具有低电压电平的相应控制信号SF1b-SFKb而被断开,从而对应于上面参照图1-图4论述的可调反相器的未激活状态。响应于给定的具有低电压电平的控制信号SF1-SFK和具有高电压电平的相应控制信号SF1b-SFKb之一,相应的由晶体管P1-PK和N1-NK组成的晶体管对在操作中被接通。具有低电压电平的控制信号SF1-SFK的各种组合和具有高电压电平的相应控制信号SF1b-SFKb对应于上述多个激活状态,其中,可调反相器500被配置为在输出节点500O上生成输出信号500SO,该输出信号500SO与输入信号500SI互补且具有对应于一些或所有由P1-PK和N1-NK组成的晶体管对的切换速度的延迟时间。

如上面参照图1-图3论述的,包含可调反相器500的DCDL电路100-300因此能够生成包含多个可调反相器500延迟时间的总延迟时间,该总延迟时间具有上面参照DCDL电路100-300论述的那些优点。

图6是根据一个或多个实施例的控制信号延迟时间的方法600的流程图。方法600可用与DCDL电路,例如上面参照相应的图1-图3论述的DCDL电路100-300。

图6中所示的方法600的操作的顺序仅是说明性的;能够以不同于图6中所示的顺序执行方法600的操作。在一些实施例中,除图6中所示的那些操作之外,可在图6中所示的操作之前、中间、期间和/或之后执行。在一些实施例中,方法600的操作是操作电路的一部分,例如,下面参照图11论述的DLL电路1100。

在操作610中,在一些实施例中,于DCDL的多个顺序耦合级的第一级处接收第一信号。在一些实施例中,于多个顺序耦合级的第一级处接收第一信号包含于DCDL的输入端处接收第一信号。在一些实施例中,于多个顺序耦合级的第一级处接收第一信号包含于上面参照图1-图3论述的DCDL电路100-300之一中的输入端IN处接收信号SI。

在各种实施例中,于多个顺序耦合级的第一级处接收输入信号包含于多个顺序耦合级的第一级的三态反相器或可调反相器处接收第一信号。在一些实施例中,于多个顺序耦合级的第一级处接收第一信号包含于上面参照图1论述的DCDL电路100中的级110-1或上面参照图2论述的DCDL电路200中的级210-1的反相器V1处接收第一信号。在一些实施例中,于多个顺序耦合级的第一级处接收第一信号包含于上面参照图3论述的DCDL电路300中的级310-1的可调反相器V7处接收第一信号。

在一些实施例中,于多个顺序耦合级的第一级处接收第一信号包含从输入缓冲器接收第一信号。在一些实施例中,于多个顺序耦合级的第一级处接收第一信号包含于上面参照图1-图3论述的DCDL电路100-300之一中的输入缓冲器VBI第一信号。

在操作620,选择多个顺序耦合级的第二级作为返回级,从而激活第二级的可调反相器作为DCDL的信号延迟路径的一部分。对于多个顺序耦合级的每一级,选择第二级包含激活信号延迟路径中的给定可调反相器,该给定可调反相器被配置为接收具有与输入信号中的信号转换的极性相同极性的信号转换,该给定可调反相器是第二级的第一可调反相器或另一个激活的可调反相器。

激活第二级的第一可调反相器包含激活在信号延迟路径的第一信号路径与信号延迟路径的第二信号路径之间耦合的第一可调反相器。在各种实施例中,如上面参照图1-图3所论述的,激活第二级的第一可调反相器包含激活在信号路径PI中的所选返回级的节点NI与信号路径PO中的所选返回级的节点NO之间耦合的可调反相器V3。

在一些实施例中,选择多个顺序耦合级的第二级作为返回级包含激活第一级的两个三态反相器作为第一信号路径的一部分,并且激活第一级的两个三态反相器作为第二信号路径的一部分,以及激活给定可调反相器包含激活第二级的第一可调反相器。在一些实施例中,如上面参照图1所论述的,选择多个顺序耦合的级的第二级作为返回级包含激活级110-1的反相器V1和V2作为信号路径PI的一部分,并且激活级110-1的反相器V4和V5作为信号路径PO的一部分,以及激活给定可调反相器包含激活级110-2...110-N中之一的可调反相器V3作为返回级。

在一些实施例中,选择多个顺序耦合级的第二级作为返回级包含激活第二级的第二可调反相器,该第二可调反相器与在第一信号路径和第二信号路径之间的第一可调反相器串联耦合,并且激活给定可调反相器包含激活第一可调反相器或第二可调反相器之一。在一些实施例中,如上面参照图2所论述的,选择多个顺序耦合的级的第二级作为返回级包含激活可调反相器V6,该可调反相器V6与在信号路径PI和信号路径PO之间的可调反相器V3串联耦合,并且激活给定可调反相器包含激活级210-1...210-N中之一的一个可调反相器V3或V6作为返回级。

在一些实施例中,其中,于多个顺序耦合级的第一级处接收输入信号包含在操作610于多个顺序耦合级的第一级的可调反相器处接收输入信号,选择多个顺序耦合级的第二级作为返回级包含激活多个顺序耦合级的第一级的可调反相器作为第一信号路径的一部分。如上面参照图3所论述的,在一些实施例中,其中,于多个顺序耦合级的第一级处接收输入信号包含在操作610于多个顺序耦合级的第一级的可调反相器处接收输入信号,选择多个顺序耦合级的第二级作为返回级包含激活级310-1的可调反相器V7作为信号路径PI的一部分。

在操作630,在一些实施例中,从DCDL的多个顺序耦合级的第一级输出第二信号。输出第二信号包含在操作620基于选择多个顺序耦合级的第二级输出第二信号,该第二信号包含相对于第一信号中的转换而具有延迟时间的转换。在各种实施例中,输出包含该转换的第二信号包含具有与第一信号中的转换的极性相同或相反极性的转换。

在一些实施例中,从多个顺序耦合级的第一级输出第二信号包含从DCDL的输入端输出第二信号。在一些实施例中,从多个顺序耦合级的第一级输出第二信号包含从上面参照图1-图3论述的DCDL电路100-300之一中的输出端OUT输出信号SO。

在一些实施例中,从多个顺序耦合级的第一级输出第二信号包含从多个顺序耦合级的第一级的三态反相器输出第二信号。在一些实施例中,从多个顺序耦合级的第一级输出第二信号包含从上面参照图1论述的DCDL电路100中的级110-1的反相器V4输出信号SO。在一些实施例中,从多个顺序耦合级的第一级输出第二信号包含从上面参照图2论述的DCDL电路200中的级210-1或上面参照图3论述的DCDL电路300中的级310-1的反相器V5输出信号SO。

在一些实施例中,从多个顺序耦合级的第一级输出第二信号包含将第二信号输出到输出缓冲器。在一些实施例中,从多个顺序耦合级的第一级输出第二信号包含将第二信号输出到上面参照图1-图3论述的DCDL电路100-300之一中的输出缓冲器VBO。

通过执行操作方法600的一些或全部,通过使对应于可编程延迟时间范围的DCDL电路的每个信号路径包含可调延迟单元来控制信号延迟时间,该可调延迟单元接收具有与DCDL电路接收的信号转换的极性相同极性的信号转换,从而获得上面参照DCDL电路100-300论述的那些优点。

图7是根据一些实施例的DCDL电路操作参数的表示。图7包含对应于包含在信号延迟路径中的DCDL级数的水平轴和对应于与级数相关的延迟时间的垂直轴。

曲线702、704以及706中的每一条都是基于电路模拟,并且对于其中n型和p型晶体管都具有目标速度特性的TT工艺变化情况,表示延迟时间相对于级数的线性。曲线702是基于上面参照图1论述的DCDL电路100的非限制性实例,曲线704是基于上面参照图2论述的DCDL电路200的非限制性实例,以及曲线706表示一种DCDL电路,对于级数范围内的每条信号路径,该DCDL电路不包含可调延迟单元,该可调延迟单元接收具有与DCDL电路接收的信号转换的极性相同极性的信号转换。

如图7所示,与曲线706相比,曲线702和704中的每一条都表示线性增加。在一些实施例中,对于TT工艺变化的情况,曲线702和704中的每一条的微分非线性(DNL)从曲线706的DNL减少了多于三倍。在一些实施例中,基于快-慢(FS)和慢-快(SF)工艺变化情况的模拟,相当于曲线702和704的DNL减少了大约一半。

图8A和图8B是根据一些实施例的相应可调反相器800A和800B的示意图。可调反相器800A和800B中的每一个都包含上面参照图5论述的元件可调反相器500的子集。

如图8A所示,可调反相器800A包含电源节点VDD、参考节点VSS、互补晶体管对PS/NS、p型晶体管P1-PK,以及n型晶体管N1,它们如上面参照图5论述的那样布置。晶体管PS和NS中的每一个的栅极耦合到被配置为接收输入信号800ASI的输入端800AI,并且晶体管P1-PK和N1的源极端耦合到输出端800AO。

晶体管P1-PK和N1中的每一个的栅极耦合到控制信号总线CTRL,从而被配置为以上面参照图5论述的方式接收并在操作中响应包含控制信号SF1-SFK和SF1b的一组控制信号SCTRL。调谐部分800ATP因此包含数量为K的P型晶体管P1-PK和单个N型晶体管N1。

在操作中,晶体管P1-PK和N1因此被配置为响应于具有高电压电平的控制信号SF1-SFK和具有低电压电平的控制信号SF1b而被断开,从而对应于上面参照图5论述的可调反相器500的未激活状态。响应于分别具有低电压电平和高电压电平的控制信号SF1和SF1b,晶体管对P1/N1在操作中被接通。响应于给定的具有低电压电平的控制信号SF2-SFK之一,相应晶体管P2-PK在操作中被接通。具有低电压电平的控制信号SF1-SFK的各种组合和具有高电压电平的控制信号SF1b因此对应于上述多个激活状态,其中,可调反相器800A被配置为在输出节点800AO上生成输出信号800ASO,该输出信号800ASO与输入信号800ASI互补且具有对应于一些或所有晶体管P1-PK和N1的切换速度的延迟时间。

如上面参照图1所论述的,延迟时间控制基于响应上升输入信号转换时的n型晶体管切换速度,以及基于响应下降输入信号转换时的p型晶体管切换速度。可调反相器800A因此被配置为单侧可调反相器,在一些实施例中也被称为单侧可调延迟单元,其中,一组控制信号SCTRL被配置为实现对应于输入信号800ASI的下降沿的多个可编程延迟时间,以及对应于输入信号800ASI的上升沿的单个延迟时间。

如图8B所示,可调反相器800B包含电源节点VDD、参考节点VSS、互补晶体管对PS/NS、p型晶体管P1,以及n型晶体管N1-NK,它们如上面参照图5论述的那样布置。晶体管PS和NS中的每一个的栅极耦合到被配置为接收输入信号800BSI的输入端800BI,并且晶体管P1和N1-NK的源极端耦合到输出端800BO。

晶体管P1和N1-NK中的每一个的栅极耦合到控制信号总线CTRL,从而被配置为以上面参照图5论述的方式接收并在操作中响应包含控制信号SF1和SF1b-SFKb的一组控制信号SCTRL。调谐部分800BTP因此包含单个P型晶体管P1和数量为K的N型晶体管N1-NK。

在操作中,晶体管P1和N1-NK因此被配置为响应于具有高电压电平的控制信号SF1和具有低电压电平的控制信号SF1b-SFKb而被断开,从而对应于上面参照图5论述的可调反相器500的未激活状态。响应于分别具有低电压电平和高电压电平的控制信号SF1和SF1b,晶体管对P1/N1在操作中被接通。响应于给定的具有高电压电平的控制信号SF2b-SFKb之一,相应晶体管N2-NK在操作中被接通。具有低电压电平的控制信号SF1和具有高电压电平的相应控制信号SF1b-SFKb的各种组合对应于上述的多个激活状态,其中,可调反相器800B被配置为在输出节点800BO上生成输出信号800BSO,该输出信号800BSO与输入信号800BSI互补且具有对应于一些或所有晶体管P1和N1-NK的切换速度的延迟时间。

可调反相器800B因此被配置为单侧可调反相器,在一些实施例中也被称为单侧可调延迟单元,其中,一组控制信号SCTRL被配置为实现对应于输入信号800BSI的上升沿的多个可编程延迟时间,以及对应于输入信号800BSI的下降沿的单个延迟时间。

如上面参照图1-图3论述的,包含可调反相器800A或800B中一个或多个的DCDL电路100-300因此能够生成包含相应可调反相器800A或800B的多个延迟时间的总延迟时间,该总延迟时间具有上面参照DCDL电路100-300论述的那些优点。

此外,DCDL电路(例如下面参照图9A-图9D论述的DCDL电路之一)包含被配置为实现相应的下降或上升输入信号转换的可编程延迟时间的一个或多个单侧可调延迟单元800A或800B,其使用比其中可调延迟单元被配置为实现上升和下降信号转换的可编程延迟时间的方法相比更少的晶体管,从而减小电路的尺寸、复杂性以及工艺变化影响。

图9A-图9D是根据一些实施例的DCDL电路900A-900D的示意图。DCDL电路900A-900D中的每一级都包含上面参照图8A和图8B论述的可调反相器800A或800B中的一个或两者,下面将进一步进行论述。

DCDL电路900A对应于上面参照图1论述的DCDL电路100,其中级110-1...110-N由级910A-1...910A-N代替,级910A-1...910A-N包含可调反相器800A或800B之一,而不是可调反相器V3。在各种实施例中,级910A-1...910A-N中的每一级都包含可调反相器800A或可调反相器800B,其中可调反相器800A被配置为具有对应于相应输入信号中的下降转换的多个延迟时间,可调反相器800B被配置为具有对应于相应输入信号中的上升转换的多个延迟时间。

在图9A所示的实施例中,级910A-1...910A-N中的每一级都包含可调反相器800A或800B之一。在各种实施例中,级910A-1...910A-N中的一个或多个包含可调800A或800B之一,并且级910A-1...910A-N中的一个或多个包含可调反相器V3。

DCDL电路900B对应于上面参照图2论述的DCDL电路200,其中级210-1...210-N由级910B-1...910B-N代替,级910B-1...910B-N包含可调反相器800A和800B中各一个,而不是可调反相器V3和V6。在图9B所示的实施例中,每个奇数级910B-1-910B-N包含可调反相器800A和可调反相器800B,其中可调反相器800A被配置为具有对应于节点NI上的相应输入信号的下降转换的多个延迟时间,可调反相器800B被配置为具有对应于节点NS上的相应输入信号的上升转换的多个延迟时间,并且,每个偶数级910B-1-910B-N包含可调反相器800B和可调反相器800A,其中可调反相器800B被配置为具有对应于节点NI上的相应输入信号的上升转换的多个延迟时间,可调反相器800A被配置为具有对应于节点NS上的相应输入信号的下降转换的多个延迟时间。在一些实施例中,DCDL电路900B包含互补配置的可调反相器800A和800B。

在图9B所示的实施例中,级910B-1...910B-N中的每一级都包含可调反相器800A和800B中各一个。在各种实施例中,级910B-1...910B-N包含不同于图9B所示可调反相器800A、800B、V3以及V6的组合,使得级910B-1...910B-N中的至少一个包含如上所述配置的可调反相器800A或800B。

DCDL电路900C对应于上面参照图3论述的DCDL电路300,其中级310-1...310-N由级910C-1...910C-N代替,级910C-1...910C-N包含可调反相器800A或800B中各两个,而不是可调反相器V3和V7。在图9C所示的实施例中,每个奇数级910C-1-910C-N包含可调反相器800A的两个实例,该两个可调反相器800A被配置为具有对应于节点NI上的相应输入信号的下降转换的多个延迟时间,并且,每个偶数级910C-1-910C-N包含可调反相器800C的两个实例,该两个可调反相器800C被配置为具有对应于节点NI上的相应输入信号的上升转换的多个延迟时间。在一些实施例中,DCDL电路900C包含互补配置的可调反相器800A和800B。

在图9C所示的实施例中,级910C-1...910C-N中的每一级都包含两个可调反相器800A或800B中之一。在各种实施例中,级910C-1...910C-N包含不同于图9C所示可调反相器800A、800B、V3以及V7的组合,使得级910C-1...910C-N中的至少一个包含如上所述配置的可调反相器800A或800B。

DCDL电路900D是一种包含输入端IN、输出端OUT、信号路径PI和PO、控制电路120,以及控制信号总线CTRL的DCDL,每一个都在上面参照图1进行了论述。代替级110-1...110-N,DCDL 900D包含级910D-1...910D-N,级910D-1...910D-N包含上面参照图1论述的反相器V1和V5以及可调反相器800A或800B中各一个。在图9D所示的实施例中,每个奇数级910D-1-910D-N包含可调反相器800A,该可调反相器800A被配置为具有对应于节点NI上的相应输入信号的下降转换的多个延迟时间,并且,每个偶数级910D-1-910D-N包含可调反相器800B,该可调反相器800B被配置为具有对应于节点NI上的相应输入信号的上升转换的多个延迟时间。在一些实施例中,DCDL电路900D包含互补配置的可调反相器800A和800B。

在图9D所示的实施例中,级910D-1...910D-N中的每一级都包含可调反相器800A或800B之一。在各种实施例中,级910D-1...910D-N中的一个或多个包含可调800A或800B之一,并且级910D-1...910D-N中的一个或多个替代地包含另一种可调反相器,例如上面参照图1论述的可调反相器V3。

通过包含可调反相器800A或可调反相器800B中的至少一个,DCDL电路900A-900D中的每一个被配置为使用比其中可调延迟单元被配置为对上升和下降信号转换都实现可编程延迟时间的方法相比更少的晶体管来实现相应下降或上升输入信号转换的可编程延迟时间,从而实现上面参照可调反相器800A和800B论述的那些优点。

图10是根据一些实施例的控制信号延迟的方法1000的流程图。方法1000可用与DCDL电路,例如上面参照相应的图1-图3论述的DCDL电路100-300或上面参照图9A-图9D论述的DCDL电路900A-900D。

图10中所示的方法1000的操作的顺序仅是说明性的;能够以不同于图10中所示的顺序执行方法1000的操作。在一些实施例中,除图10中所示的那些操作之外,可在图10中所示的操作之前、中间、期间和/或之后执行。在一些实施例中,方法1000的操作是操作电路的一部分,例如,下面参照图11论述的DLL电路1100。

在操作1010,在一些实施例中,于DCDL的输入端处接收第一信号。在一些实施例中,于DCDL的输入端处接收第一信号包含于上面参照图1-图3论述的DCDL电路100-300或上面参照图9A-图9D论述的DCDL电路900A-900D之一中的输入端IN处接收信号SI。

在一些实施例中,于DCDL的输入端处接收第一信号包含于输入缓冲器处接收第一信号。在一些实施例中,于DCDL的输入端处接收第一信号包含于上面参照图1-图3论述的DCDL电路100-300或上面参照图9A-图9D论述的DCDL电路900A-900D之一中的输入缓冲器VBI处接收第一信号。

在操作1020,选择DCDL的多个级中的一级作为返回级,从而激活在输入路径和输出路径之间耦合的所选级的可调反相器,该可调反相器包含与n型晶体管数量不同的若干个p型晶体管。

在一些实施例中,激活包含与n型晶体管数量不同的若干个p型晶体管的可调反相器包含激活可调反相器800A,如上面参照图8A论述的,该可调反相器800A包含数量为K的p型晶体管P1-PK和单个n型晶体管N1。在一些实施例中,激活包含与n型晶体管数量不同的若干个p型晶体管的可调反相器包含激活可调反相器800B,如上面参照图8B论述的,该可调反相器800B包含单个p型晶体管P1和数量为K的n型晶体管N1-NK。

在一些实施例中,激活包含与n型晶体管数量不同的若干个p型晶体管的可调反相器包含激活不同数量的p型和n型晶体管。在各种实施例中,激活不同数量的p型和n型晶体管包含激活上面参照图8A论述的可调反相器800A的晶体管P1-PK中的一些或全部和晶体管N1,或者激活上面参照图8B论述的可调反相器800B的晶体管P1和晶体管N1-NK中的一些或全部。

在各种实施例中,选择DCDL的多个级中的一级包含选择上面参照图1论述的级110-1...110-N中之一,上面参照图2论述的级210-1...210-N中之一,上面参照图3论述的级310-1...310-N中之一,上面参照图9A论述的级910A-1...910A-N中之一,上面参照图9B论述的级910B-1...910B-N中之一,上面参照图9C论述的级910C-1...910C-N中之一,或上面参照图9D论述的级910D-1...910D-N中之一。

在操作1030,在一些实施例中,将第二信号输出到DCDL的输出端。在一些实施例中,将第二信号输出到DCDL的输出端包含将信号SO输出到上面参照图1-图3论述的DCDL电路100-300或上面参照图9A-图9D论述的DCDL电路900A-900D之一中的输出端OUT。

在一些实施例中,将第二信号输出到DCDL的输出端包含从输出缓冲器输出第二信号。在一些实施例中,将第二信号输出到DCDL的输出端包含从上面参照图1-图3论述的DCDL电路100-300或上面参照图9A-图9D论述的DCDL电路900A-900D中之一的输出缓冲器VBI输出第二信号。

通过执行操作方法1000中的一些或全部,使用与其中可调延迟单元被配置为对上升和下降信号转换都实现可编程延迟时间的方法相比更少的晶体管来实现相应下降或上升输入信号转换的可编程延迟时间,从而实现上面参照可调反相器800A和800B论述的那些优点。

图11是根据一些实施例的DLL电路1100的示意图。DLL电路1100包含相位检测器1110、低通滤波器1120,以及DCDL电路1130。相位检测器1110包含被配置为接收参考时钟信号CLKR和系统时钟信号CLKS的输入端(未标记),以及耦合到低通滤波器1120的输入端(未标记)的输出端(未标记)。DCDL电路1130包含耦合到低通滤波器1120的输出端(未标记)的输入端(未标记),以及被配置为输出系统时钟信号CLKS的输出端(未标记)。

相位检测器1110是一种被配置为检测参考时钟信号CLKR和系统时钟信号CLKS之间的相位差,然后输出指示检测到的相位差的电压电平的电子电路。

低通滤波器1120是一种被配置为将电压电平从相位检测器1110传递到DCDL1130,同时衰减交流(AC)信号分量的电子电路。

DCDL电路1130是上面参照图1-图3论述的DCDL电路100-300或上面参照图9A-图9D论述的DCDL电路900A-900D中之一,包含控制电路120,该控制电路120被配置为基于从低通滤波器1120接收的电压电平通过实现可编程延迟时间从而使得DCDL电路1130生成系统时钟信号CLKS。

DLL电路1100因此被配置为生成具有与参考时钟信号CLKR的相位同步相位的系统时钟信号CLKS。

通过包含DCDL电路100-300或900A-900B之一,DLL电路1100能够基于根据上述实施例生成的延迟时间来同步时钟信号CLKR和CLKS,从而实现上面参照DCDL电路100-300和900A-900D论述的那些优点。

在一些实施例中,DCDL包含:输入端;输出端;以及多个级,该多个级被配置为将信号沿第一信号路径从输入端传播到多个级的可选返回级,然后沿第二信号路径从多个级的返回级传播到输出端。该多个级中的每一级包含:第一和第二反相器,被配置为选择性将该信号沿该第一信号路径传播;第三和第四反相器,被配置为选择性将该信号沿该第二信号路径传播;以及第五反相器,被配置为选择性将该信号从该第一信号路径传播到第二信号路径。在一些实施例中,第五反相器耦合到输入端与第一和第二反相器之间的第一信号路径,并且耦合到输出端与第三和第四反相器之间的第二信号路径。在一些实施例中,第一至第四反相器中的每一个包含三态反相器。在一些实施例中,第一至第四反相器中的每一个都被配置为接收同一对互补控制信号。在一些实施例中,第五反相器具有对应于多于三个输出状态的可调选择配置。在一些实施例中,第五反相器包含第一p型晶体管和第一n型晶体管,第一p型晶体管和第一n型晶体管中的每一个都包含被配置为接收信号的栅极,以及在第一p型晶体管和第一n型晶体管之间耦合的调谐部分,该调谐部分包含并联配置并且是p型或n型中的同一种的两个独立可控晶体管。在一些实施例中,调谐部分还包含与两个晶体管串联耦合并且是p型或n型中的另一种的第三晶体管,其中,第三晶体管是调谐部分中p型或n型中另一种的唯一晶体管。在一些实施例中,DCDL包含在延迟锁相环(DLL)电路中。

在一些实施例中,DCDL包含:输入端;输出端;以及多个级,该多个级被配置为将信号沿第一信号路径从输入端传播到多个级的可选返回级,然后沿第二信号路径从多个级的返回级传播到输出端。多个级中的每一级都包含:第一反相器,被配置为选择性将信号沿第一信号路径传播;第二反相器,被配置为选择性将信号沿第二信号路径传播;以及第三和第四反相器,串联耦合并且被配置为选择性将信号从第一信号路径传播到第二信号路径。在一些实施例中,第三反相器耦合到输入端与第一反相器之间的第一信号路径,并且第四反相器耦合到输出端与第二反相器之间的第二信号路径。在一些实施例中,第一和第二反相器中的每一个都包含三态反相器。在一些实施例中,第三和第四反相器中的每一个都具有对应于多于三个输出状态的可调选择配置。在一些实施例中,第三和第四反相器中的每一个都包含第一p型晶体管和第一n型晶体管,第一p型晶体管和第一n型晶体管中的每一个都包含被配置为接收信号的栅极;以及调谐部分,该调谐部分耦合在第一p型晶体管和第一n型晶体管之间,该调谐部分包含并联配置的多个独立可控p型晶体管和并联配置的多个独立可控n型晶体管,其中,多个独立可控p型晶体管与多个独立可控n型晶体管串联耦合。在一些实施例中,第三和第四反相器被配置为接收同一组控制信号。在一些实施例中,DCDL还包含第五反相器,该第五反相器耦合在多个级与输入端或输出端之一之间。

在一些实施例中,一种控制信号延迟时间的方法,包含于DCDL的多个顺序耦合级的第一级处接收输入信号,然后选择多个顺序耦合级的第二级作为返回级,从而激活第二级的第一可调反相器作为该DCDL的信号延迟路径的一部分。对于多个顺序耦合级的每一级,选择第二级作为返回级包含激活信号延迟路径中的给定可调反相器,该给定可调反相器被配置为接收具有与输入信号的信号转换的极性相同极性的信号转换,该给定可调反相器是第二级的第一可调反相器或另一个激活的可调反相器。在一些实施方式中,激活第二级的第一可调反相器包含激活在信号延迟路径的第一信号路径与信号延迟路径的第二信号路径之间耦合的第一可调反相器。在一些实施例中,选择多个顺序耦合级的第二级作为返回级包含激活第一级的两个三态反相器作为第一信号路径的一部分,并且激活第一级的两个三态反相器作为第二信号路径的一部分,以及激活给定可调反相器包含激活第二级的第一可调反相器。在一些实施例中,选择多个顺序耦合级的第二级作为返回级包含激活第二级的第二可调反相器,该第二可调反相器与在第一信号路径和第二信号路径之间的第一可调反相器串联耦合,并且激活给定可调反相器包含激活第一可调反相器或第二可调反相器之一。在一些实施例中,于多个顺序耦合级的第一级处接收输入信号包含于多个顺序耦合级的第一级的第二可调反相器处接收输入信号,然后选择多个顺序耦合级的第二级作为返回级包含激活多个顺序耦合级的第一级的第二可调反相器作为第一信号路径的一部分。

上面概述了若干实施例的特征,使得本领域技术人员可以更好地理解本发明的方面。本领域技术人员应该理解,它们可以容易地使用本发明作为基础来设计或修改用于实施与本文所介绍实施例相同的目的和/或实现相同优势的其它工艺和结构。本领域技术人员也应该意识到,这种等同构造并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,本文中它们可以做出多种变化、替换以及改变。

- 数字控制延迟线及其方法

- 数字控制延迟线