静电放电阻隔电路

文献发布时间:2023-06-19 11:57:35

技术领域

本发明是有关于一种静电放电阻隔电路,特别是有关于一种具有静电放电释放元件的静电放电阻隔电路。

背景技术

集成电路的静电放电(electrostatic discharge;ESD)事件,指的是具有高电压的静电电荷,通过集成电路芯片的释放过程。虽然如此的静电电荷量通常不多,但是,因为高电压的原因,其释放的瞬间能量也相当的可观,如果没有善加处理,往往会造成集成电路的烧毁。

因此,ESD已经是半导体产品中重要的可靠度考虑之一。比较为一般人熟悉的ESD测试有两种,人体放电模式(human body model,HBM)以及机器放电模式(machine model,MM)。一般商业用的集成电路都必须具备一定程度的HBM以及MM的耐受度,才可以贩售,否则,集成电路非常容易因为偶然的ESD事件而损毁。也因此,如何制造一个有效率的ESD防护装置/元件,来保护集成电路,也是业界一直不断探讨与研究的课题。

发明内容

本发明提供一种静电放电阻隔电路,包括一内部电路、一肖特基二极管以及一静电放电释放元件。肖特基二极管耦接于一特定节点与内部电路之间。静电放电释放元件耦接于特定节点与一电源端之间。当一静电放电事件发生于特定节点时,静电放电释放元件导通,用以将一静电放电电流由特定节点释放至电源端。

本发明可以保护集成电路。

附图说明

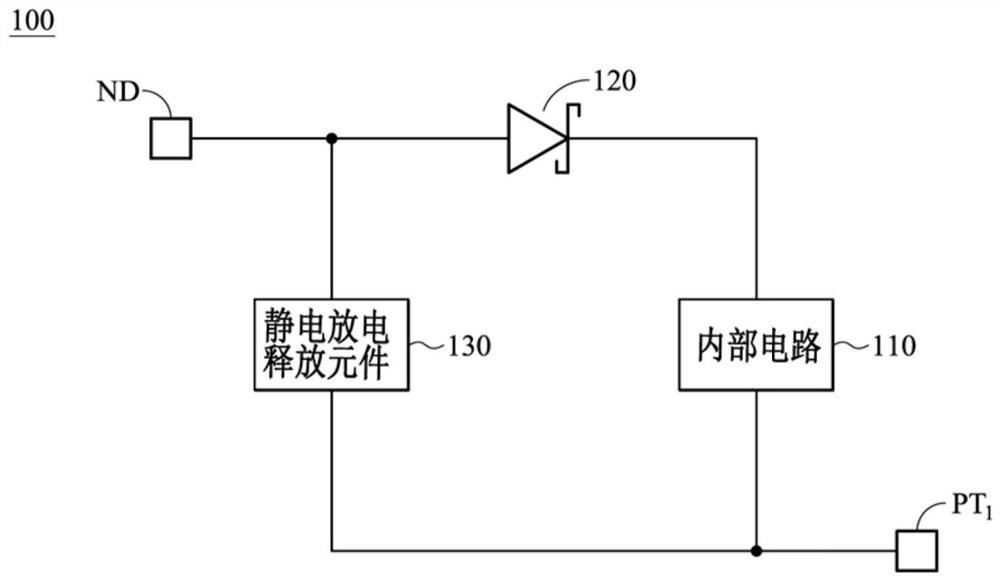

图1为本发明的静电放电阻隔电路的架构示意图。

图2为本发明的静电放电阻隔电路的一可能实施例。

图3为本发明的静电放电阻隔电路的另一实施例。

图4为本发明的静电放电阻隔电路的另一实施例。

图5为本发明的静电放电阻隔电路的另一实施例。

附图标号

100:静电放电阻隔电路

110:内部电路

120,411,511:肖特基二极管

130:静电放电释放元件

PT

ND:特定节点

VPP

VDD,VSS:操作电压

211:存取电路

212:存储阵列

313,414,514:P型晶体管

312:双极晶体管

413:输出级

513:输入级

311,314,315,412,415,512,515:N型晶体管

具体实施方式

为让本发明的目的、特征和优点能更明显易懂,下文特举出实施例,并配合所附图式,做详细的说明。本发明说明书提供不同的实施例来说明本发明不同实施方式的技术特征。其中,实施例中的各元件的配置为说明之用,并非用以限制本发明。另外,实施例中图式标号的部分重复,是为了简化说明,并非意指不同实施例之间的关联性。

图1为本发明的静电放电阻隔电路的架构示意图。如图所示,静电放电阻隔电路100包括一内部电路110、一肖特基二极管(schottky diode)120及一静电放电释放元件130。内部电路110耦接于肖特基二极管120的阴极与电源端PT

当一静电放电事件发生于特定节点ND,并且电源端PT

当静电放电事件未发生时,静电放电阻隔电路100操作于一正常模式。在正常模式下,由于肖特基二极管120具有较低的直流阻抗(DC resistance),故当特定节点ND接收到外部信号或电压时,肖特基二极管120可快速地导通,用以将特定节点ND的信号或电压传送至内部电路110。在此示意图中,内部电路110根据特定节点ND的信号或电压而动作。本发明并不限定内部电路110的架构。任何需要ESD保护的电路均可作为内部电路110。

图2为本发明的静电放电阻隔电路的一可能实施例。在本实施例中,特定节点ND作为一输入节点,用以提供信号或电压予内部电路110。在一可能实施例中,特定节点ND接收并提供电压VPP

内部电路110根据操作电压VDD及VSS开始动作。在本实施例中,操作电压VDD与VSS作为内部电路110的操作电压,故操作电压VDD与VSS必需分别稳定于一固定值。举例而言,操作电压VDD可能维持于3.3V,而操作电压VSS维持于0V。当操作电压VDD与VSS不稳定时,内部电路110可能无法正常工作。

相对于操作电压VDD与VSS,特定节点ND的电压并不会维持在一固定值。举例而言,在一第一期间(如一写入期间),特定节点ND的电压等于电压VPP

本发明并不限定内部电路110的架构。在一可能实施例中,内部电路110为一次性可编程存储器(one time programmable memory;OTP memory),并具有一存取电路211以及一存储阵列212。

存取电路211用以存取存储阵列212。本发明并不限定存取电路211的架构。在一可能实施例中,存取电路211根据电压VPP

存储阵列212具有多个存储单元(未显示)。本发明并不限定存储单元的结构。在一可能实施例中,存储阵列212的每一存储单元具有至少一晶体管,每一晶体管具有一浮动栅极(floating gate)。在进行写入操作时,存取电路211提供电压VPP

在另一可能实施例中,存储阵列212的每一存储单元具有至少一晶体管。在此例中,存取电路211可能利用电压VPP

在其它实施例中,存储阵列212的每一存储单元具有至少一熔丝(fuse)。在此例中,存取电路211可能利用电压VPP

当一静电放电事件发生于特定节点ND,并且电源端PT

图3为本发明的静电放电阻隔电路的另一可能实施例。在本实施例中,特定节点ND作为一电源端,用以接收操作电压VDD。内部电路110根据操作电压VDD与VSS开始动作。在一可能实施例中,内部电路110包括一P型晶体管313、N型晶体管314及315。

P型晶体管313的源极耦接肖特基二极管120的阴极。P型晶体管313的漏极耦接N型晶体管314的漏极。N型晶体管314的源极耦接电源端PT

当一静电放电事件发生在特定节点ND,并且电源端PT

在本实施例中,静电放电释放元件130包括一N型晶体管311。N型晶体管311的漏极耦接特定节点ND,其栅极与源极耦接电源端PT

图4为本发明的静电放电阻隔电路的另一实施例。在本实施例中,特定节点ND作为一输出节点,用以输出内部电路110的信号。由于内部电路110可能输出负电压,故静电放电阻隔电路100更包括一肖特基二极管411。在其它实施例中,如果内部电路110所输出的信号或电压的位准只会在一正位准与一接地位准(如0V)之间变化时,则可省略肖特基二极管411。

在本实施例中,肖特基二极管411并联肖特基二极管120。如图所示,肖特基二极管120的阴极耦接肖特基二极管411的阳极以及输出级413。肖特基二极管120的阳极与肖特基二极管411的阴极耦接特定节点ND。当内部电路110输出正位准时,肖特基二极管411导通。因此,特定节点ND的位准为正位准。然而,当内部电路110输出负电压时,肖特基二极管120导通。因此,特定节点ND的位准为负位准。

本发明并不限定内部电路110的架构。任何可输出信号或电压的电路,均可作为内部电路110。在本实施例中,内部电路110包括一输出级413。输出级413根据一控制信号S

在本实施例中,输出级413包括一P型晶体管414以及一N型晶体管415。P型晶体管414的源极耦接电源端PT

当一静电放电事件未发生时,静电放电阻隔电路100操作于一正常模式。在正常模式下,当电源端PT

当一静电放电事件发生于特定节点ND并且电源端PT

图5为本发明的操作电路的另一实施例。在本实施例中,特定节点ND作为一输入节点,用以提供信号或电压予内部电路110。由于特定节点ND所接收的信号或电压的位准可能为正值或负值,故在本实施例中,静电放电阻隔电路100更包括一肖特基二极管511。

肖特基二极管511并联肖特基二极管120。如图所示,肖特基二极管120的阴极与肖特基二极管511的阳极耦接输入级513,并且肖特基二极管120的阳极与肖特基二极管511的阴极耦接特定节点ND。当特定节点ND接收一正值的信号或电压时,肖特基二极管120导通,用以传送特定节点ND的信号或电压予内部电路110。然而,当特定节点ND接收一负值的信号或电压时,肖特基二极管511导通,用以传送负值的信号或电压予内部电路110。

本发明并不限定内部电路110的架构。任何可接收外部信号或电压的电路,均可作为内部电路110。在本实施例中,内部电路110包括一输入级513。输入级513根据特定节点ND的电压而动作。举例而言,当特定节点ND的信号或电压的位准等于一第一位准(如正位准)时,输入级513输出操作电压VSS。当特定节点ND的信号或电压的位准等于一第二位准(如负位准)时,输入级513输出操作电压VDD。在其它实施例中,当特定节点ND的信号或电压的位准等于一接地位准(如0V)时,输入级513也输出操作电压VDD。在一些实施例中,当特定节点ND的信号或电压在一正位准与一接地位准变化时,则可省略肖特基二极管511。

在本实施例中,输入级513包括一P型晶体管514以及一N型晶体管515。P型晶体管514的源极耦接电源端PT

当一静电放电事件发生于特定节点ND并且电源端PT

除非另作定义,在此所有词汇(包含技术与科学词汇)均属本发明所属技术领域中相关技术人员的一般理解。此外,除非明白表示,词汇于一般字典中的定义应解释为与其相关技术领域的文章中意义一致,而不应解释为理想状态或过分正式的语态。

虽然本发明已以较佳实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中相关技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰。举例来,本发明实施例的系统、装置或是方法可以硬件、软件或硬件以及软件的组合的实体实施例加以实现。因此本发明的保护范围当视权利要求所界定者为准。

- 静电放电电路、具有静电放电电路的显示面板和静电放电方法

- 静电放电阻隔电路