多通道的NAND FLASH差错控制方法

文献发布时间:2023-06-19 12:10:19

技术领域

本发明涉及差错控制方法,具体地,涉及一种基于BCH及类RAID技术的多通道NANDFLASH差错控制方法及系统。

背景技术

NAND Flash具有非易失性、可靠性高、体积小、重量轻、功耗小、抗震能力强、工作温度范围宽等优点,业已广泛用于各个领域,尤其是航空航天。但NAND FLASH随着使用以及数据存储时间的变长,存储在里面的数据容易发生比特翻转,出现随机性的错误。此外,随着FLASH块擦写次数增多,氧化层逐渐老化,电子进出存储单元越来越容易,因此存储在里面的电荷容易发生异常,导致块失效。

目前,常用的方法采用差错编码控制,如海明校验、BCH、LDPC等差错控制编码。该方法可以满足在误码率较低的应用场合,随着误码率提高,当超出算法纠错能力后将无法完成数据纠错;其次,算法纠错能力越强,其复杂度越高,无法满足高速数据纠错的场合。

发明内容

针对现有技术中的缺陷,本发明的目的是提供一种基于BCH及类RAID技术的多通道NAND FLASH差错控制方法,从抑制、纠错、替换三个维度采取设计措施降低NAND FLASH的误码率。

根据本发明提供的多通道的NAND FLASH差错控制方法,包括:

S1:对输入数据按通道数N进行分组生成N组通道数据,将通道数据按照通道数N进行交织;N≥2;

S2:将N组通道数据按通道数进行按位异或生成校验数据;

S3:将校验数据和N组通道数据形成N+1组通道数据分别进行并行加扰;

S4:将校验数据和N组通道数据分别进行BCH并行编码,并按FLASH存储芯片的页长进行分块后存储在存储阵列中,所述存储阵列包括N+1颗FLASH存储芯片,N+1颗FLASH存储芯片与N+1组通道数据一一对应;

S5:读取存储阵列中N+1组通道数据,对N+1组通道数据分别进行并行BCH译码,并给出译码是否成功的状态;

S6:将N+1组通道数据分别进行并行解扰;

S7:根据所述译码是否成功的状态,对N+1组通道数据进行容错控制;

S8:将完成差错控制的通道数据进行解交织恢复。

优选地,每一通道数据的位宽与存储阵列中的FLASH存储芯片的位宽保持一致;所述校验数据的位宽与FLASH存储芯片的位宽保持一致。

优选地,所述存储阵列包括N+1组通道,其中N组通道用于数据存储,1组通道用于校验信息存储。

优选地,在步骤S2中,以通道为单位按位进行奇偶校验,生成校验数据。

优选地,在步骤S4中,将N+1组通道数据分别进行BCH并行编码,其中并行宽度与通道位宽一致,编码块长L为FLASH存储芯片页长的公约数。

优选地,在步骤S7中,根据N+1组通道数据组BCH译码的“成功状态”进行容错控制,具体为,若N组通道数据BCH译码均成功,则输出译码数据;若N组通道数据仅有一组BCH译码失败且校验数据BCH译码成功,则将所有译码成功的通道数据进行异或生成新数据,然后自动替代译码失败的通道数据,并将该组的FLASH块标记为坏块;若N组通道数据有多于两组BCH译码失败,则给出系统错误信息。

优选地,在BCH编码、BCH译码、加扰、解扰、存储或读取数据时均采用多通道并行处理技术,且每个通道数据与存储芯片一一对应,通道数据的位宽与存储芯片的位宽一致。

优选地,所述BCH并行编码的纠错能力t必须大于或等于通道位宽。

优选地,所述BCH并行编码的信息位长度k与加扰、解扰编码的块长度一致。

优选地,步骤S3中,N+1组通道数据分别进行加扰,完成数据随机化;在步骤S6中,对N+1组通道数据分别进行解扰,恢复数据。

与现有技术相比,本发明具有如下的有益效果:

1、本发明运用数据随机化的方式,让存储在FLASH芯片中的0和1分布充分隔离,降低了相邻单元之间的耦合电压产生的影响,减小了翻转概率。

2、本发明采用BCH纠错编译码,降低了多通道NAND FLASH存储系统误码率;并结合类RAID3容错技术,自主地实现了故障通道数据的恢复,提高了数据存储的可靠性。

3、本发明提通过数据分组,采用FPGA多通道并行数据处理技术,提高了数据随机化和纠错的速度。

附图说明

通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

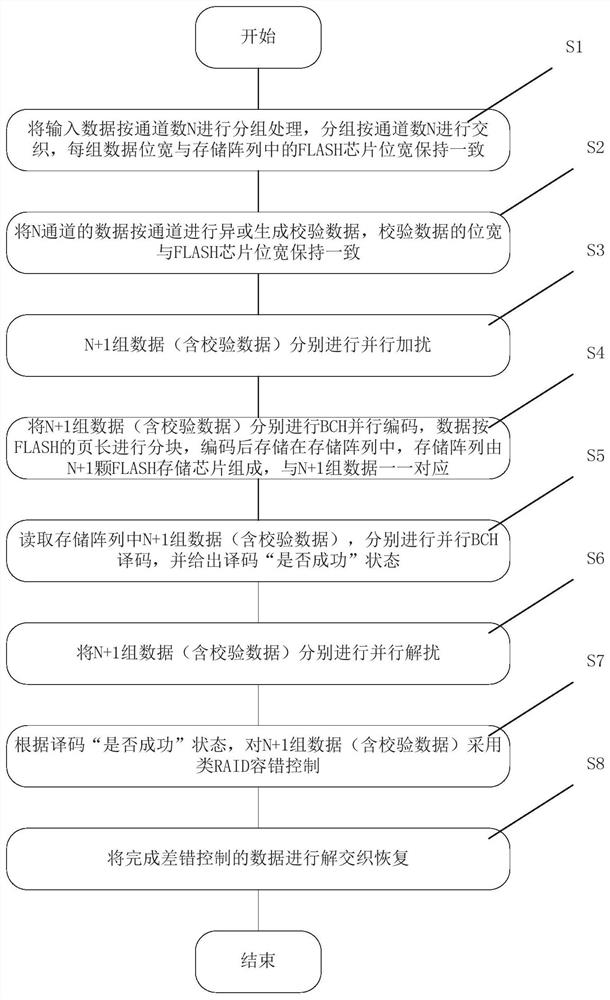

图1为本发明实施例中基于BCH及类RAID技术的多通道NAND FLASH差错控制方法的整体流程图;

图2为本发明实施例中基于BCH及类RAID技术的多通道NAND FLASH差错控制方法的FPGA模块原理框图;

图3为本发明实施例中基于BCH及类RAID技术的多通道NAND FLASH差错控制方法的BCH(4200,4096,8)编码数据及校验信息存储示意图。

具体实施方式

下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进。这些都属于本发明的保护范围。

在本发明实施例中,如图1所示,本发明提供的一种基于BCH及类RAID技术的多通道NAND FLASH差错控制方法,包括以下步骤:

S1:对输入8位并行数据按通道数N(N=8)进行分组,交织深度I为8,每组通道数据的位宽为8位,存储阵列中选用的FLASH存储芯片为3Dplus公司的3DFN128G08VS8308,位宽为8比特,页长为4320字节,其中包含空白区224字节;

S2:将N(N=8)组数据按通道进行按位异或生成8位校验数据,校验数据的位宽与FLASH芯片位宽保持一致;

S3:将包含的校验数据9组数据分别进行并行加扰;

S4:将9组数据分别进行BCH并行编码,数据按FLASH的页长中不含空白区4096字节进行分块,每块码长为512字节,即4096比特,编码后分别一一对应存储在存储阵列中,存储阵列由9颗(N+1)FLASH存储芯片组成;

S5:读取存储阵列中9组(N+1)组数据(含校验数据),分别进行并行BCH译码,并给出译码“是否成功”状态;

S6:将9组(N+1)组数据(含校验数据)分别进行并行解扰;

S7:根据译码“是否成功”状态,对9组(N+1)数据(含校验数据)采用RAID技术容错控制;

S8:将完成差错控制的数据进行解交织恢复。

进一步,图2为本发明实施例中基于BCH及类RAID技术的多通道NAND FLASH差错控制方法的FPGA模块原理框图,如图2所示,本发明还包括FPGA和存储阵列。

进一步,所述存储阵列为多通道,含有9个通道,其中8个通道用于数据存储,1个通道专门用于校验信息存储。

进一步,所述存储阵列的数据存储与校验按类RAID3(Redundant Array ofIndependent Disks)容错技术方式控制,每颗FLASH存储芯片作为一个“磁盘”,每一个通道对应一片FLASH存储芯片。

进一步,在步骤S1中,对输入的数据进行交织处理,交织后每组通道数据的位宽与存储阵列中的FLASH存储芯片的位宽一致,位宽B为8,然后存入缓存,完成数据转换。

进一步,在步骤S2中,以通道为单位按位进行奇偶校验,生成8位校验数据。

进一步,在步骤S3中,将9组数据(含校验数据)分别进行并行加扰,完成数据随机化。码长为512字节,生成多项式为F(X)=X

进一步,图3为本发明提供的基于BCH及类RAID技术的多通道NAND FLASH差错控制方法的BCH(4200,4096,8)编码数据及校验信息存储示意图,如图3所示,在步骤S4中,将9组数据(含校验数据)分别进行BCH并行编码,编码宽度为8比特;编码块长为512字节,即信息长度k=4096;BCH纠错能力t=8,校验位长度为13×8=104比特,总长度n=4200(525字节)。FLASH存储芯片一页长度为4096字节+224字节的空白区,顺序交替存储8块BCH(4200,4096,8)的信息码和校验码。

进一步,读取存储阵列中的9组数据,存入缓存,在步骤S5中,以3倍速率将9组数据(含校验数据)分别进行BCH(4200,4096,8)并行译码,并给出每组译码“是否成功”状态。

进一步,在步骤S6中,将9组数据(含校验数据)分别进行并行解扰,完成数据恢复。码长为512字节,生成多项式为F(X)=X

进一步,在步骤S7中,根据9组BCH译码“是否成功”状态进行类RAID3技术容错控制。若8组数据BCH译码均成功,则输出译码数据不变;若8组数据仅有一组BCH译码失败且校验数据BCH译码成功,则将所有译码成功的通道数据进行异或生成新数据,然后替代译码失败的数据组,并将该通道的FLASH块标记为坏块;若9组数据有多于两组BCH译码失败,则给出系统错误信息。

进一步,在步骤S8中,将数据解交织恢复输出。

进一步,BCH编码、BCH译码、加扰、解扰、存储或读取均采用多通道处理技术,9组数据并行处理,且每组通道数据与存储芯片一一对应,通道数据位宽与芯片位宽均为8比特。

进一步,BCH(4200,4096,8)纠错能力t等于通道位宽。BCH编码块信息位长度k与加、解扰编码的块长度一致,均为512字节。

在本发明实施例中,运用数据随机化的方式,让存储在FLASH芯片中的0和1分布充分隔离,降低了相邻单元之间耦合电压产生的影响,减小了翻转概率;其次,通过采用BCH纠错编译码,降低了多通道NAND FLASH存储系统误码率;并结合类RAID3容错技术,自主地实现了故障通道数据的恢复,提高了数据存储的可靠性。最后,通过数据分组,利用FPGA多通道并行数据处理技术,提高了数据随机化和纠错的速度。

以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变形或修改,这并不影响本发明的实质内容。

- 多通道的NAND FLASH差错控制方法

- 一种NAND Flash固态存储自适应差错控制方法