高动态范围图像传感器

文献发布时间:2023-06-19 12:11:54

本申请为发明名称为“高动态范围图像传感器”、申请号为201810310719.3、申请日为2018年4月9日的中国发明专利申请的分案申请。

技术领域

本发明大体上涉及图像传感器,且更具体来说,本发明涉及高动态范围图像传感器。

背景技术

标准图像传感器具有约60到70dB的有限动态范围。但是,真实世界的亮度动态范围大得多。自然场景的范围通常跨90dB及以上。为了同时捕获高光和阴影,已经在图像传感器中使用HDR技术来增大捕获的动态范围。增大动态范围的最常用技术是将用标准(低动态范围)图像传感器捕获的多个曝光合并成单个线性HDR图像,其具有远大于单个曝光图像的动态范围。

最常见的HDR传感器解决方案之一将是在一个单个图像传感器上进行多次曝光。在不同曝光积分时间或不同灵敏度(例如通过插入中性密度滤波器)的情况下,一个图像传感器在单个图像传感器中可具有2、3、4甚至更多次不同的曝光。使用此HDR图像传感器,在单次拍摄中可获得多个曝光图像。但是,与正常全分辨率图像传感器相比,使用此HDR传感器使总体图像分辨率降低。例如,对于将4个不同曝光组合在一个图像传感器中的HDR传感器,每个HDR图像将仅为全分辨率图像的四分之一分辨率图像。

发明内容

本发明的一个实施例涉及一种用于高动态范围(HDR)图像传感器中的像素电路。所述用于高动态范围(HDR)图像传感器中的像素电路包括:光电二极管,其安置在第一半导体晶片中,所述光电二极管经调适以在所述HDR图像传感器的单个图像捕获的单次曝光期间响应于入射光而光产生电荷载子;浮动扩散部,其安置在所述第一半导体晶片中,且经耦合以接收所述光电二极管中光产生的所述电荷载子;转移晶体管,其安置在所述第一半导体晶片中且耦合在所述光电二极管与所述浮动扩散部之间,其中所述转移晶体管经调适以接通从而将所述光电二极管中光产生的所述电荷载子转移到所述浮动扩散部;像素内电容器,其安置在第二半导体晶片中,其中所述第一半导体晶片与所述第二半导体晶片堆叠且耦合到所述第二半导体晶片;及双浮动扩散(DFD)晶体管,其安置在所述第一半导体晶片中且经耦合在所述浮动扩散部与所述像素内电容器之间,其中所述像素内电容器通过所述DFD晶体管选择性地耦合到所述浮动扩散部,其中所述浮动扩散部响应于所述像素内电容器经耦合到所述浮动扩散部而设定为低转换增益,且其中所述浮动扩散部响应于所述像素内电容器从所述浮动扩散部解耦而设定为高转换增益。

本发明的另一实施例涉及一种高动态范围(HDR)成像传感器系统。所述高动态范围(HDR)成像传感器系统包括:像素电路的像素阵列,其中所述像素电路中的每一者包含:光电二极管,其安置在第一半导体晶片中,所述光电二极管经调适以在所述HDR图像传感器系统的单个图像捕获的单次曝光期间响应于入射光而光产生电荷载子;浮动扩散部,其安置在所述第一半导体晶片中,且经耦合以接收所述光电二极管中光产生的所述电荷载子;转移晶体管,其安置在所述第一半导体晶片中且耦合在所述光电二极管与所述浮动扩散部之间,其中所述转移晶体管经调适以接通以将所述光电二极管中光产生的所述电荷载子转移到所述浮动扩散部;像素内电容器,其安置在第二半导体晶片中,其中所述第一半导体晶片与所述第二半导体晶片堆叠且耦合到所述第二半导体晶片;及双浮动扩散(DFD)晶体管,其安置在所述第一半导体晶片中且耦合在所述浮动扩散部与所述像素内电容器之间,其中所述像素内电容器通过所述DFD晶体管选择性地耦合到所述浮动扩散部,其中所述浮动扩散部响应于所述像素内电容器耦合到所述浮动扩散部而设定为低转换增益,且其中所述浮动扩散部响应于所述像素内电容器从所述浮动扩散部解耦而设定为高转换增益;控制电路,其耦合到所述像素阵列以控制所述像素阵列的操作;及读出电路,其耦合到所述像素阵列以从所述多个像素读出图像数据。

附图说明

参考下列诸图描述本发明的非限制性及非穷举性实施例,其中除非另外指定,否则贯穿各个视图,类似参考数字指类似部分。

图1是图示说明根据本发明的教示的包含彩色像素阵列的成像系统的一个实例的图,其中每个像素电路是实现高动态范围(HDR)成像的包含堆叠架构的双转换增益电路。

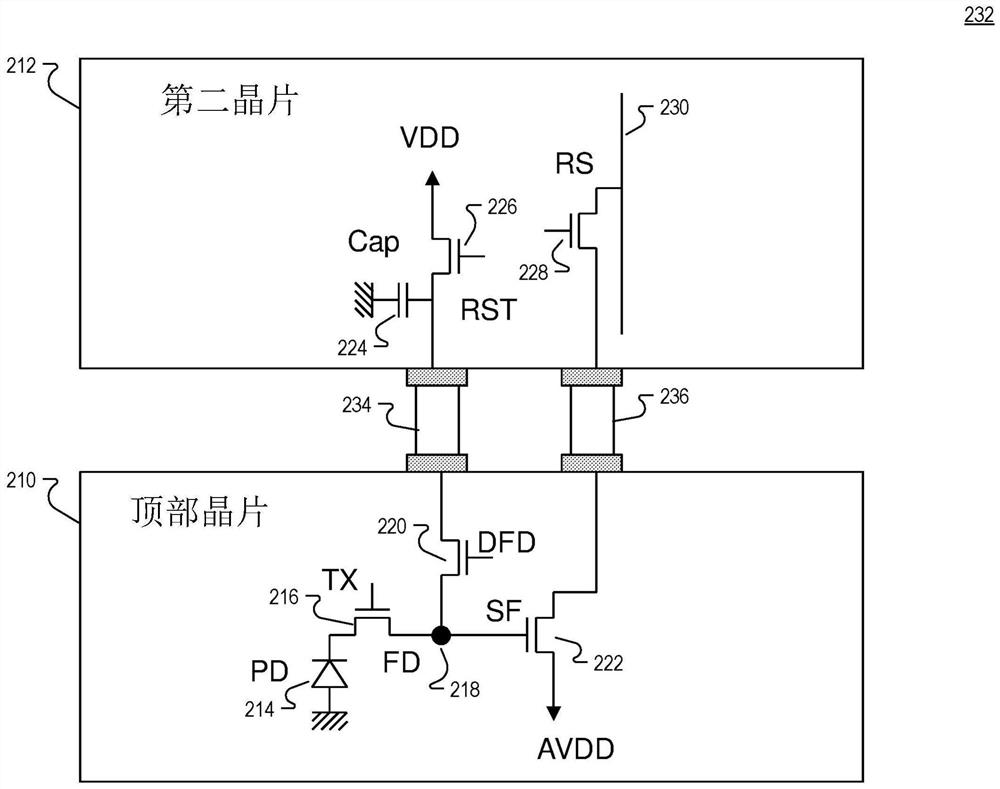

图2是图示说明根据本发明的教示的实现HDR成像的具有在堆叠架构中实施的双转换增益的像素电路的一个实例的图。

图3是图示说明根据本发明的教示的实现HDR成像的具有在堆叠架构中实施的双转换增益的像素电路的另一实例的图。

贯穿附图的若干视图的对应参考符号指示对应组件。本领域的技术人员将了解,诸图中的元件是出于简明和清晰的目的图示说明且不一定按比例绘制。例如,诸图中的一些元件的尺寸可相对其它元件放大来帮助改进对本发明的各种实施例的理解。同样地,通常不描绘商业上可行的实施例中有用或必要的常见又充分理解的元件,以便促进对本发明的这些各种实施例的较少阻碍视图。

具体实施方式

在下列描述中,陈述许多特定细节以便提供对本发明的通透理解。但是,所属领域的技术人员将了解,不需要采取特定细节来实践本发明。在其它实例中,不详细描述众所周知的材料或方法以便避免混淆本发明。

贯穿此说明书的对“一个实施例”、“实施例”、“一个实例”或“实例”的参考意味着结合实施例或实例描述的特定特征、结构或特性包含在本发明的至少一个实施例中。因此,贯穿此说明书出现在各种位置的片语“在一个实施例中”、“在实施例中”、“一个实例”或“实例”不一定都指同一实施例或实例。此外,特定特征、结构或特性可在一或多个实施例或实例中以任何适当组合和/或子组合进行组合。特定特征、结构或特性可包含在集成电路、电子电路、组合逻辑电路或提供所描述功能性的其它适当组件中。另外,所属领域的技术人员将了解,此处提供的图是出于解释的目的且附图不一定按比例绘制。

根据本发明的教示的实例描述彩色像素阵列,在所述彩色像素阵列中,根据本发明的教示,每个像素电路以双转换增益读出以实现HDR成像。在实例中,根据本发明的教示,每个像素电路在包含至少两个半导体晶片的堆叠架构中实施以实现HDR成像,其中光电二极管、浮动扩散部(FD)、转移晶体管和双浮动扩散(DFD)晶体管安置在第一半导体晶片中,且像素内电容器安置在与第一半导体晶片堆叠并耦合到第一半导体晶片的第二半导体晶片中。因此,所述晶片中的一者包含像素阵列,且所述晶片中的另一者为逻辑晶片。

在一个实例中,通过启用或停用将像素内电容器耦合到FD节点的DFD晶体管将像素阵列的像素电路中的转换增益设定为高或低。凭借此结构,高转换增益可相当高,且低转换增益可相当低。如将揭示,根据本发明的教示,此结构在关断双浮动扩散晶体管时提供具有小满井容量的高转换增益,并在接通双浮动扩散晶体管时提供具有大满井容量的低转换增益,甚至对于小尺寸像素也如此。

因此,每一帧都可以高转换增益和低转换增益读出,并且通过接通或关断双浮动扩散晶体管而数字化地选择使用哪一个转换增益。如此,根据本发明的教示的彩色像素阵列可根据本发明的教示可以在同一帧中以单一曝光或单一积分时间同时捕获明亮对象和灰暗对象两者。因此,高曝光时间和低曝光时间的多重曝光不再是必要的,这可带来挑战,这是因为多重曝光时间不会同时发生。由于根据本发明的教示的彩色像素阵列输出具有不同转换增益的像素值,以每帧输出产生仅一个积分时间的HDR图像,因此消除重像和光闪烁的问题。

为了图示说明,图1是图示说明根据本发明的教示的包含彩色像素阵列102的高动态范围(HDR)成像系统100的一个实例的图,其中每个像素电路以双转换增益读出以实现HDR成像。如在所描绘的实例中展示,HDR成像系统100包含耦合到控制电路108和读出电路104的像素阵列102,读出电路104耦合到功能逻辑106。

在一个实例中,像素阵列102是图像传感器像素电路132(例如,P1、P2、P3、…、Pn)的二维(2D)阵列。如图示说明,每个像素电路132经布置成行(例如,行R1到Ry)及列(例如,列C1到Cx)以获取人员、位置、对象等的图像数据,所述图像数据可接着用于呈现人员、位置、对象等的2D图像。

在一个实例中,在每个像素电路132(例如,P1、P2、P3、…、Pn)已经获取到其图像数据或图像电荷之后,图像数据通过位线130由读出电路104读出且接着转移到功能逻辑106。在各种实例中,读出电路104可包含放大电路、模/数(ADC)转换电路或其他。功能逻辑106可仅存储图像数据或甚至通过应用图像后效果(例如,剪裁、旋转、移除红眼、调整亮度、调整对比度或其它)而操纵图像数据。在一个实例中,读出电路104可沿着读出列线一次读出一行图像数据(所图示说明)或可使用各种其它技术(未图示说明)(例如,串行读出所有像素或同时全部并行读出所有像素)读出图像数据。

在一个实例中,控制电路108耦合到像素阵列102以控制像素阵列102的像素电路132的操作特性。在一个实例中,控制电路108可经耦合以产生用于控制每个像素电路132的图像获取的全局快门信号。在实例中,全局快门信号同时启用像素阵列102内的所有像素电路132(例如,P1、P2、P3、…、Pn)以同时启用像素阵列102中的所有像素电路132以在单个获取窗期间从每个各别光电检测器同时转移图像电荷。

如在所描绘的实例中展示,且如将在下文进一步详细描述,根据本发明的教示,像素阵列102的光电二极管以及浮动扩散部(FD)、转移晶体管和双浮动扩散(DFD)晶体管安置在第一半导体晶片110中,且像素阵列102的像素内电容器、复位晶体管及行选择晶体管安置在与第一半导体晶片110堆叠并耦合到第一半导体晶片110的第二半导体晶片112中以实现HDR成像,两个半导体晶片呈堆叠晶片架构。换句话说,在一个实例中,根据本发明的教示,第一半导体晶片110包含像素阵列102,且第二半导体晶片112是逻辑晶片。

图2是图示说明根据本发明的教示的实现HDR成像的在堆叠架构中实施的具有双转换增益的像素电路232的一个实例的图。应注意,像素电路232可为图1的像素阵列102的像素电路132中的一者的实例,且下文引用的类似命名且编号的元件类似于上文描述般耦合且起作用。如在图2中描绘的实例中展示,像素电路232包含安置在第一半导体晶片210(在图2中还标记为“顶部晶片”)中的光电二极管PD 214。在实例中,光电二极管PD 214经调适以在HDR图像传感器的单个图像捕获的单次曝光期间响应于入射光而光产生电荷载子。浮动扩散部(FD)安置在第一半导体晶片210中,且经耦合以接收光电二极管PD 214中光产生的电荷载子。转移晶体管216安置在第一半导体晶片210中,且耦合在光电二极管PD 214与浮动扩散部218之间。转移晶体管216经调适以响应于转移信号TX接通和关断从而将光电二极管PD 214中光产生的电荷载子选择性地转移到浮动扩散部218。

双浮动扩散(DFD)晶体管220安置在第一半导体晶片210中,且耦合到浮动扩散部218和像素内电容器。像素内电容器224安置在第二半导体晶片212中。在所描绘的实例中,像素内电容器224端接到接地。在各种实例中,应注意,可用金属氧化物半导体(MOS)电容器、金属绝缘体金属(MIM)电容器、沟槽电容器或任何其他适当类型的电容器实施像素内电容器224。

在实例中,第一半导体晶片210在堆叠晶片架构中与第二半导体晶片212堆叠且耦合到第二半导体晶片212。因此,像素内电容器224响应于双浮动扩散信号DFD通过DFD晶体管220选择性地耦合到浮动扩散部218。因此,响应于像素内电容器224通过DFD晶体管220耦合到浮动扩散部,将浮动扩散部218设定为低转换增益。另外,响应于通过响应于DFD信号关断DFD晶体管220而使像素内电容器224从浮动扩散部218解耦,将浮动扩散部218设定为高转换增益。

如在所描绘的实例中展示,像素电路232还包含安置在第一半导体晶片210中的放大器晶体管222。在一个实例中,放大器晶体管222是耦合源极跟随器(SF)的场效晶体管(FET),且因此包含耦合到浮动扩散部218的栅极端子,以在放大器晶体管222的源极端子处产生像素电路232的输出信号。在实例中,放大器晶体管222的漏极耦合到AVDD电压。

继续图2中描述的实例,行选择晶体管228安置在第二半导体晶片212中,并耦合到第一半导体晶片210中的放大器晶体管222,以响应于行选择信号RS,将像素电路232的输出信号从放大器晶体管222通过通孔236选择性地耦合到第二半导体晶片212中的输出位线230。在实例中,通孔236因此经耦合在第一半导体晶片210和第二半导体晶片212之间,且耦合在行选择晶体管228和放大器晶体管222之间。在一个实例中,输出位线230可耦合到包含在第二半导体晶片中的读出电路,例如如图1所图示说明的读出电路104。

在图2中描绘的实例也图示说明,复位晶体管安置在第二半导体晶片212中,并通过通孔234耦合到第二半导体晶片中的像素内电容器224和第一半导体晶片中的DFD晶体管220。因此,通孔234耦合在第一半导体晶片210和第二半导体晶片212之间,且耦合在复位晶体管226和DFD晶体管220之间。在操作中,复位晶体管226经耦合以响应于复位信号RST选择性地复位浮动扩散部218和光电二极管PD 214。在实例中,响应于DFD信号用复位晶体管226选择性地接通DFD晶体管220以复位浮动扩散部218和光电二极管PD 214。

在一个实例中,应了解,第二半导体晶片212中的像素内电容器224、行选择晶体管228和复位晶体管226以与第一半导体晶片210中的相应像素电路的间距相同的间距布置在第二半导体晶片212上。

图3是图示说明根据本发明的教示的实现HDR成像的在堆叠架构中实施的具有双转换增益的像素电路332的另一实例的图。应注意,像素电路332可为图1的像素阵列102的像素电路132中的一者的实例,且下文引用的类似命名且编号的元件类似于上文描述般耦合且起作用。另外,应注意,图3的像素电路332也与图2的像素电路232共享许多相似点。实际上,如在图3中描绘的实例中展示,像素电路332包含安置在第一半导体晶片310(还标记为“顶部晶片”)中的光电二极管PD 314。浮动扩散部(FD)安置在第一半导体晶片310中,且经耦合以接收光电二极管PD 314中光产生的电荷载子。在实例中,浮动扩散部318也以电容方式耦合到升压信号340。转移晶体管316安置在第一半导体晶片310中,且耦合在光电二极管PD 314与浮动扩散部318之间。转移晶体管3216经调适以响应于转移信号TX接通和关断从而将光电二极管PD 314中光产生的电荷载子选择性地转移到浮动扩散部318。

双浮动扩散(DFD)晶体管320安置在第一半导体晶片310中,且耦合到浮动扩散部318和像素内电容器。像素内电容器324安置在第二半导体晶片312中。在所描绘的实例中,像素内电容器324还耦合到脉冲驱动信号338以增大实际处理能力。在各种实例中,应注意,可用金属氧化物半导体(MOS)电容器、金属绝缘体金属(MIM)电容器、沟槽电容器或任何其他适当类型的电容器实施像素内电容器324。

在实例中,第一半导体晶片310在堆叠晶片架构中与第二半导体晶片312堆叠且耦合到第二半导体晶片312。因此,像素内电容器324响应于双浮动扩散信号DFD通过DFD晶体管320选择性地耦合到浮动扩散部318。因此,响应于像素内电容器324通过DFD晶体管320耦合到浮动扩散部,将浮动扩散部318设定为低转换增益。另外,响应于通过响应于DFD信号关断DFD晶体管320而使像素内电容器324与浮动扩散部318解耦,将浮动扩散部318设定为高转换增益。

如在所描绘的实例中展示,像素电路332还包含安置在第一半导体晶片310中的放大器晶体管322。在一个实例中,放大器晶体管322是耦合源极跟随器(SF)的场效晶体管(FET),且因此包含耦合到浮动扩散部318的栅极端子,以在放大器晶体管222的源极端子处产生像素电路332的输出信号。在实例中,放大器晶体管322的漏极经耦合到AVDD电压。

继续图3中描述的实例,行选择晶体管328安置在第二半导体晶片312中,并耦合到第一半导体晶片310中的放大器晶体管322,以响应于行选择信号RS,将像素电路332的输出信号从放大器晶体管322通过通孔336选择性地耦合到第二半导体晶片312中的输出位线330。在实例中,通孔336因此耦合在第一半导体晶片310和第二半导体晶片312之间,且耦合在行选择晶体管328和放大器晶体管322之间。在一个实例中,输出位线330可耦合到包含在第二半导体晶片中的读出电路,例如如图1所图示说明的读出电路104。

在图3中描绘的实例也图示说明,复位晶体管安置在第二半导体晶片312中,并通过通孔334耦合到第二半导体晶片中的像素内电容器324和第一半导体晶片中的DFD晶体管320。因此,通孔334耦合在第一半导体晶片310和第二半导体晶片312之间,且耦合在复位晶体管326和DFD晶体管320之间。在操作中,复位晶体管326经耦合以响应于复位信号RST选择性地复位浮动扩散部318和光电二极管PD 314。在实例中,响应于DFD信号用复位晶体管326选择性地接通DFD晶体管320以复位浮动扩散部318和光电二极管PD 314。

本发明的绘示性实例的以上描述(包含[摘要]中的描述内容)并不意在为详尽的或限于所揭示的精确形式。虽然在本文中出于绘示性目的描述了本发明的特定实施例和实例,但在不脱离本发明的更广阔精神和范围的情况下,各种等效修改是可能的。

鉴于以上详细描述内容,可对本发明的实例做出这些修改。用于所附权利要求书中的术语不应被解释为将本发明限制于说明书和权利要求书中揭示的特定实施例。事实上,将完全通过所附权利要求书确定范围,其应根据所确立的权利要求解释的教义来阐释。本说明书和诸图因此被视为绘示性的而非限制性的。

- 用于高动态范围图像传感器的图像传感器像素

- 固态高动态范围图像传感器的像素电路和所述图像传感器