外延结构、外延生长方法及光电器件

文献发布时间:2023-06-19 12:16:29

技术领域

本发明属于半导体技术领域,具体涉及一种外延结构、外延生长方法及光电器件。

背景技术

高In组分(x>0.68)In

为解决这个问题,现有技术中常通过采用缓冲层技术来抑制失配产生的位错,提升材料质量。缓冲层生长方式为线性变换式生长,包括:组分线性变换式、组分步进变换式。

线性变换式生长过程中由于没有陡峭清晰的界面,在生长初期产生的位错会一直延伸到外延层中,降低外延层质量;单一组分变换生长对缓冲层组分要求较为严格,若组分有所偏差,则极易导致目标外延层表面粗糙。

在缓冲层材料方面,常规的缓冲层材料多为混合阳离子材料,如In

另一方面,In

因此,针对上述技术问题,有必要提供一种外延结构、外延生长方法及光电器件。

发明内容

有鉴于此,本发明的目的在于提供一种外延结构、外延生长方法及光电器件,以突破外延层和衬底之间晶格常数的限制,释放晶格失配应力,降低外延层表面粗糙度,获得高质量的高In组分InGaAs外延层。

为了实现上述目的,本发明一实施例提供的技术方案如下:

一种外延结构,所述外延结构由下向上依次包括InP衬底、第一缓冲层、第二缓冲层及In

所述第一缓冲层为InP缓冲层;

所述第二缓冲层包括若干由下向上As组分递增的InAs

所述In

一实施例中,所述第二缓冲层包括至少五层由下向上As组分递增的InAs

一实施例中,最下层InAs

一实施例中,所述InAs

一实施例中,所述InP衬底的晶向为[001];和/或,所述InP缓冲层的厚度不低于50nm;和/或,所述In

本发明另一实施例提供的技术方案如下:

一种外延生长方法,所述外延生长方法包括:

S1、提供InP衬底;

S2、在InP衬底上外延生长第一缓冲层,第一缓冲层为InP缓冲层;

S3、在第一缓冲层上外延生长第二缓冲层,第二缓冲层包括若干由下向上As组分递增的InAs

S4、在第二缓冲层上外延生长In

一实施例中,所述步骤S1还包括:

对InP衬底进行脱氧处理以去除InP衬底表面的氧化层,脱氧处理的温度为480~550℃,气压为P氛围,压力为2E-8Torr以上。

一实施例中,所述第一缓冲层、第二缓冲层及In

一实施例中,所述第二缓冲层包括至少五层由下向上As组分递增的InAs

最下层InAs

所述InAs

本发明再一实施例提供的技术方案如下:

一种光电器件,所述光电器件包括上述的外延结构。

本发明具有以下有益效果:

本发明通过生长As组分递增的InAs

附图说明

为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请中记载的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

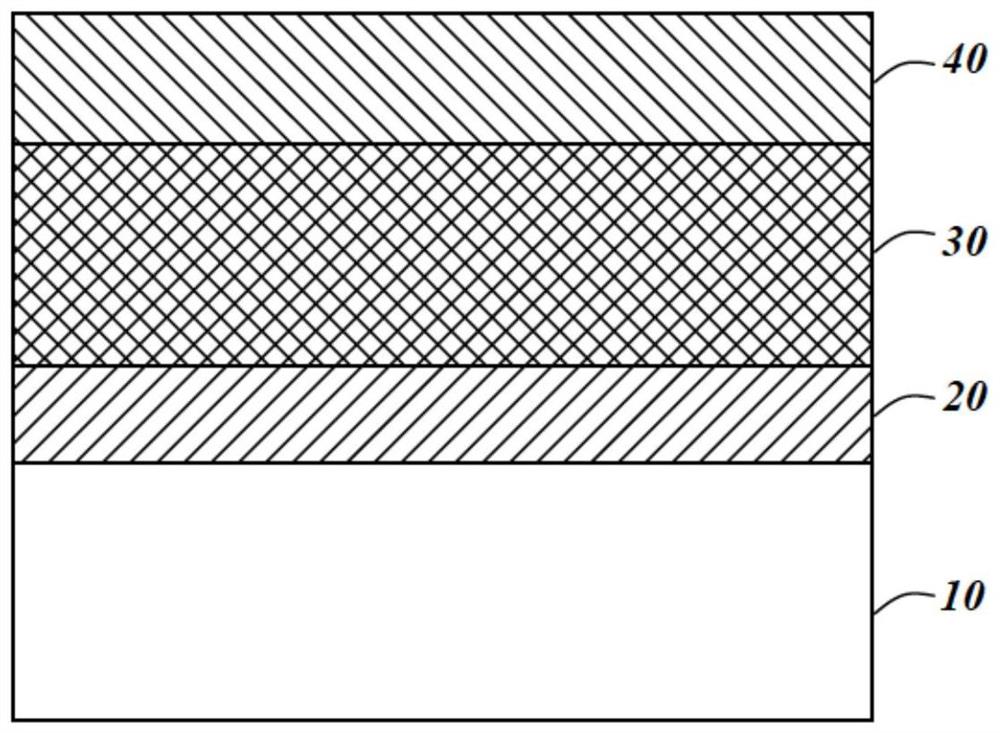

图1为本发明中外延结构的结构示意图;

图2为本发明中第二缓冲层的结构示意图;

图3为本发明中外延生长方法的流程示意图;

图4为本发明一具体实施例中第二缓冲层的结构示意图;

图5a、5b分别为组分步进式结构和应力调制式外延结构中In

图6a、6b分别为组分步进式结构和应力调制式外延结构中In

具体实施方式

为了使本技术领域的人员更好地理解本发明中的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

参图1所示,本发明公开了一种外延结构,该外延结构由下向上依次包括InP衬底10、第一缓冲层20、第二缓冲层30及In

InP衬底10的晶向为[001];

第一缓冲层20为InP缓冲层,InP缓冲层的厚度不低于50nm;

第二缓冲层30包括若干由下向上As组分递增的InAs

In

结合图2所示,本发明中的第二缓冲层30包括至少五层由下向上As组分递增的InAs

优选地,最下层InAs

进一步地,InAs

参图3所示,本发明还公开了一种外延生长方法,包括以下步骤:

S1、提供InP衬底;

S2、在InP衬底上外延生长第一缓冲层,第一缓冲层为InP缓冲层;

S3、在第一缓冲层上外延生长第二缓冲层,第二缓冲层包括若干由下向上As组分递增的InAs

S4、在第二缓冲层上外延生长In

进一步地,步骤S1还包括:

对InP衬底进行脱氧处理以去除InP衬底表面的氧化层,脱氧处理的温度为480~550℃,气压为P氛围,压力为2E-8Torr以上。

优选地,第一缓冲层、第二缓冲层及In

本发明中前一缓冲层中的上层应力调制缓冲层与下一层中的下层应力调制缓冲层As组分相差较大,可以增加二者之间的应力,可以将失配位错有效地被限制在界面处而不至于穿透至下一缓冲层。此时上层应力调制缓冲层所受到应力为张应力,可以使晶格具有向外扩张的趋势而产生较为平坦的表面形貌;但下层应力调制缓冲层厚度过厚,则会使其产生新的失配位错,因此,本发明中下层应力调制缓冲层的厚度优选为30~150nm。

另外,本发明中第一缓冲层、第二缓冲层及In

以下结合具体实施例对本发明作进一步说明。

本发明一具体实施例中的外延结构,由下向上依次包括InP衬底10、第一缓冲层20、第二缓冲层30及In

InP衬底10的晶向为[001];

第一缓冲层20为InP缓冲层,InP缓冲层的厚度为200nm;

第二缓冲层30包括五层由下向上As组分递增的InAs

In

结合图4所示,本实施例中的第二缓冲层30包括8层由下向上As组分递增的InAs

InAs

InAs

InAs

InAs

InAs

InAs

InAs

InAs

InAs

本实施例中外延结构的外延生长方法可在InP衬底上生长In组分为0.78的In

1、首先将晶向为[001]的InP衬底放入生长腔内,温度升至495℃,通入P源使衬底处于P氛围(压力为2E-8Torr以上)保护下进行脱氧处理5分钟,以去除衬底表面的氧化物。优选地,在放入生长腔之前,在预处理室内升温至350℃处理1小时。

2、在晶向为[001]的InP衬底上生长InP缓冲层。具体为:

利用全固态分子束外延工艺,InP生长速率为0.5μm/h,生长温度为490℃,V/III为100,腔体压力约5E-6Torr,生长一层厚度为200nm的InP缓冲层。

3、在InP缓冲层上生长As组分递增的InAs

采用分子束外延工艺,将生长温度控制在475℃,生长速率为1.5μm/h,V/III比为70,P源束流保持不变,改变As源束流。

首先生长As组分为12%的第一InAs

接着生长As组分为18%的第一InAs

接着生长As组分为24%的第一InAs

以此依次生长第一InAs

最后一层InAs

4、最后在As组分递增的InAs

采用分子束外延工艺,将生长温度控制在485℃,生长速率为1μm/h,V/III比为30,厚度为2000nm。

对比图5a、5b所示,现有技术组分步进式结构中的In

对比图6a、6b所示,从XRD的倒空间mapping图可以看出,现有技术组分步进式结构中的In

本实施例的外延结构及外延生长方法中,通过生长As组分递增的InAs

由以上技术方案可以看出,本发明具有以下优点:

本发明通过生长As组分递增的InAs

对于本领域技术人员而言,显然本发明不限于上述示范性实施例的细节,而且在不背离本发明的精神或基本特征的情况下,能够以其他的具体形式实现本发明。因此,无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本发明的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本发明内。不应将权利要求中的任何附图标记视为限制所涉及的权利要求。

此外,应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

- 外延生长方法、外延结构及光电器件

- 抑制具有异质结的光电器件中外延生长的方法和光电器件