像素阵列基板

文献发布时间:2023-06-19 18:29:06

技术领域

本发明涉及一种像素阵列基板。

背景技术

显示器的应用日益广泛,举凡家用的视听娱乐、公共场合的信息显示看板、电竞用的显示器及可携式电子产品都可见其踪迹。近几年来,显示器大多兼具有触控功能。显示器的触控种类大致上可分为外挂(out-cell)式、晶胞上(on-cell)式及内嵌式(In-celltouch)。内嵌式触控(In-cell touch)技术具有易薄型化的优势,因此在近几年逐渐成为触控显示器的主流。然而,整合于显示器中的数据线及/或栅极线和用以供间隙物站立的导电图案易产生耦合效应,进而造成漏光问题。

发明内容

本发明提供一种像素阵列基板,性能佳。

本发明一实施例的像素阵列基板包括栅极线、数据线、主动(有源)元件、像素电极、共用电极、触控信号线及导电图案。数据线与栅极线交错设置。主动元件具有第一端、第二端及控制端。主动元件的第一端电连接至数据线,且主动元件的控制端电连接至栅极线。像素电极电连接至主动元件的第二端。共用电极重叠于像素电极。触控信号线电连接于共用电极。导电图案设置于触控信号线旁,电性隔离于触控信号线,且用以与间隙物重叠。数据线具有曲线段。在像素阵列基板的俯视图中,数据线的曲线段绕过导电图案且与导电图案隔开。

本发明一实施例的像素阵列基板包括栅极线、数据线、主动元件、像素电极、共用电极、触控信号线及导电图案。数据线与栅极线交错设置。主动元件具有第一端、第二端及控制端。主动元件的第一端电连接至数据线,且主动元件的控制端电连接至栅极线。像素电极电连接至主动元件的第二端。共用电极重叠于像素电极。触控信号线电连接于共用电极。导电图案设置于触控信号线旁,电性隔离于触控信号线,且用以与间隙物重叠。栅极线具有曲线段。在像素阵列基板的俯视图中,栅极线的曲线段绕过导电图案且与导电图案隔开。

本发明一实施例的像素阵列基板包括栅极线、数据线、主动元件、像素电极、共用电极、触控信号线及导电图案。数据线与栅极线交错设置。主动元件具有第一端、第二端及控制端。主动元件的第一端电连接至数据线,且主动元件的控制端电连接至栅极线。像素电极电连接至主动元件的第二端。共用电极重叠于像素电极。触控信号线电连接于共用电极。导电图案设置于触控信号线旁,电性隔离于触控信号线,且用以与间隙物重叠。导电图案具有多个主要部。在像素阵列基板的俯视图中,多个主要部位数据线与栅极线的至少一者的不同侧。

本发明一实施例的像素阵列基板包括栅极线、数据线、主动元件、像素电极、共用电极、触控信号线及导电图案。数据线与栅极线交错设置。主动元件具有第一端、第二端及控制端。主动元件的第一端电连接至数据线,且主动元件的控制端电连接至栅极线。像素电极电连接至主动元件的第二端。共用电极重叠于像素电极。触控信号线电连接于共用电极。导电图案设置于触控信号线旁,电性隔离于触控信号线,且用以与间隙物重叠。导电图案电连接至像素电极。

附图说明

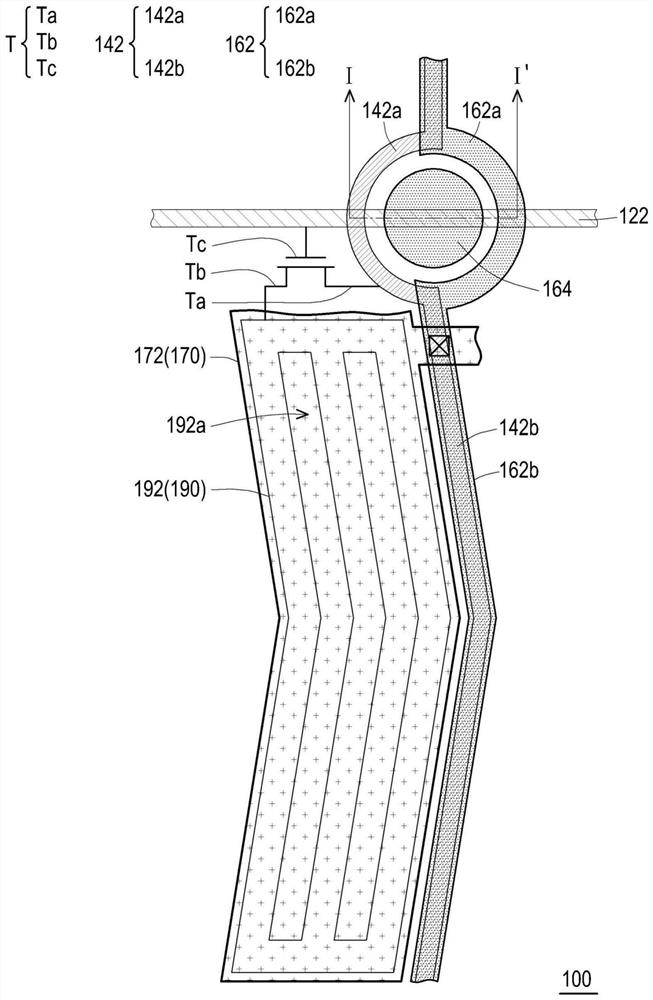

图1为本发明一实施例的像素阵列基板100的俯视示意图;

图2为本发明一实施例的显示面板10的剖面示意图;

图3为本发明另一实施例的像素阵列基板100A的俯视示意图;

图4为本发明又一实施例的像素阵列基板100B的俯视示意图;

图5为本发明再一实施例的像素阵列基板100C的俯视示意图;

图6为本发明一实施例的像素阵列基板100D的俯视示意图;

图7为本发明另一实施例的像素阵列基板100E的俯视示意图;

图8为本发明又一实施例的像素阵列基板100F的俯视示意图。

符号说明

10:显示面板

100、100A、100B、100C、100D、100E、100F:像素阵列基板110:基底

120:第一金属层

122、122A:栅极线

122a、142a、162a:曲线段

130:第一绝缘层

140:第二金属层

142、142B、142C、142D:数据线

142b、162b:折线段

150:第二绝缘层

160:第三金属层

162:触控信号线

164、164B、164D、164E、164F:导电图案164B-1、164B-2、164C-1、164C-2、164C-3、164C-4:主要部170:第一透明导电层

172:共用电极

182:第三绝缘层

184:第四绝缘层

190:第二透明导电层

192:像素电极

192a:狭缝

200:对向基板

300:显示介质

T:主动(有源)元件

Ta:第一端

Tb:第二端

Tc:控制端

PS:间隙物

I-I’:剖线

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

应当理解,当诸如层、膜、区域或基板的元件被称为在另一元件“上”或“连接到”另一元件时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反,当元件被称为“直接在另一元件上”或“直接连接到”另一元件时,不存在中间元件。如本文所使用的,“连接”可以指物理及/或电连接。再者,“电连接”或“耦合”可以是二元件间存在其它元件。

本文使用的“约”、“近似”、或“实质上”包括所述值和在本领域普通技术人员确定的特定值的可接受的偏差范围内的平均值,考虑到所讨论的测量和与测量相关的误差的特定数量(即,测量系统的限制)。例如,“约”可以表示在所述值的一个或多个标准偏差内,或±30%、±20%、±10%、±5%内。再者,本文使用的“约”、“近似”或“实质上”可依光学性质、蚀刻性质或其它性质,来选择较可接受的偏差范围或标准偏差,而可不用一个标准偏差适用全部性质。

除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

图1为本发明一实施例的像素阵列基板100的俯视示意图。

图2为本发明一实施例的显示面板10的剖面示意图。图2对应图1的剖线I-I’。图1省略图2的基底110。

请参照图1及图2,像素阵列基板100包括基底110。基底110用以承载像素阵列基板100的其它元件。举例而言,在本实施例中,基底110的材质可为玻璃、石英、有机聚合物、或是不透光/反射材料(例如:晶片、陶瓷、或其它可适用的材料)、或是其它可适用的材料。

像素阵列基板100还包括栅极线122,设置于基底110上。像素阵列基板100还包括数据线142,与栅极线122交错设置。举例而言,在本实施例中,栅极线122及数据线142可分别属于不同的第一金属层120及第二金属层140,其中第一金属层120与第二金属层140之间设有第一绝缘层130,但本发明不以此为限。

像素阵列基板100还包括主动元件T,具有第一端Ta、第二端Tb及控制端Tc,其中主动元件T的第一端Ta电连接至数据线142,且主动元件T的控制端Tc电连接至栅极线122。举例而言,在本实施例中,主动元件T可包括薄膜晶体管,第一端Ta、第二端Tb及控制端Tc可分别为薄膜晶体管的源极、漏极与栅极,薄膜晶体管还包括沟道(未绘示),其中源极与漏极分别与沟道的不同两区电连接。在本实施例中,薄膜晶体管的栅极例如是属于第一金属层120,薄膜晶体管的源极与漏极例如是属于第二金属层140,而第一绝缘层130例如是设置于沟道与栅极之间的栅绝缘层,但本发明不以此为限。

像素阵列基板100还包括像素电极192及共用电极172。像素电极192电连接至主动元件T的第二端Tb。共用电极172与像素电极192相重叠。举例而言,在本实施例中,像素电极192具有多个狭缝192a,重叠于共用电极172。在显示时间区间,共用电极172与像素电极192之间的电位差可形成边缘电场,以驱动显示介质300(例如但不限于:液晶),进而显示画面。像素阵列基板100还包括触控信号线162,电连接于共用电极172。在触控时间区间,共用电极172是作为触控感测垫使用。

在本实施例中,像素阵列基板100还包括设置于第二金属层140上的第二绝缘层150,第三金属层160设置于第二绝缘层150上,而触控信号线162例如是属于第三金属层160;像素阵列基板100还包括设置于第三金属层160上的第三绝缘层182;像素阵列基板100还包括设置于第三绝缘层182上的第一透明导电层170,而共用电极172例如是属于第一透明导电层170;像素阵列基板100还包括设置于第一透明导电层170上的第四绝缘层184;像素阵列基板100还包括设置于第四绝缘层184上的第二透明导电层190,而像素电极192例如是属于第二透明导电层190;但本发明不以此为限。

举例而言,在本实施例中,第一透明导电层170及第二透明导电层190的材质例如是铟锡氧化物、铟锌氧化物、铝锡氧化物、铝锌氧化物、铟锗锌氧化物、其它合适的氧化物、或者是上述至少两者的堆叠层,但本发明不以此为限。

像素阵列基板100还包括导电图案164,设置于触控信号线162旁,电性隔离于触控信号线162,且用以与间隙物PS重叠。具体而言,在本实施例中,显示面板10包括像素阵列基板100、对向基板200及设置于像素阵列基板100与对向基板200之间的显示介质300;间隙物PS设置于对向基板200与像素阵列基板100之间,以维持显示面板10的晶胞间隙(cellgap),而导电图案164是用以作为供间隙物PS站立的平台。

举例而言,在本实施例中,导电图案164与触控信号线162同属第三金属层160,且导电图案164与触控信号线162于结构上分离。此外,在本实施例中,导电图案164例如是浮置的(floating),但本发明不以此为限。

请参照图1,值得注意的是,数据线142具有曲线段142a。在像素阵列基板100的俯视图中,数据线142的曲线段142a绕过导电图案164且与导电图案164隔开。举例而言,在本实施例中,数据线142的曲线段142a可为一圆弧段,但本发明不以此为限。

在本实施例中,触控信号线162具有曲线段162a。在像素阵列基板100的俯视图中,触控信号线162的曲线段162a及数据线142的曲线段142a分别经由导电图案164的相对两侧绕过导电图案164。举例而言,在本实施例中,触控信号线162的曲线段162a可为一圆弧段,但本发明不以此为限。

在本实施例中,数据线142还具有折线段142b,位于像素电极192旁且与曲线段142a连接。触控信号线162还具有折线段162b,与曲线段162a连接。在像素阵列基板100的俯视图中,数据线142的折线段142b与触控信号线162的折线段162b可相重叠,但本发明不以此为限。

值得一提的,由于数据线142利用曲线段142a绕过供间隙物PS站立的导电图案164,因此,导电图案164与数据线142的耦合效应可降低。如此一来,因导电图案164受数据线142影响造成显示介质300(例如:液晶)转动而产生的漏光问题可获得改善。

在此必须说明的是,下述实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,下述实施例不再重述。

图3为本发明另一实施例的像素阵列基板100A的俯视示意图。

图3的像素阵列基板100A与图1的像素阵列基板100类似,两者的差异在于:两者的栅极线122、122A不同。请参照图3,具体而言,在本实施例中,栅极线122A具有曲线段122a。在像素阵列基板100的俯视图中,栅极线122A的曲线段122a绕过导电图案164且与导电图案164隔开。举例而言,在本实施例中,栅极线122A的曲线段122a可为一圆弧段,但本发明不以此为限。

由于栅极线122A利用曲线段122a绕过供间隙物PS站立的导电图案164,因此,导电图案164与栅极线122A的耦合效应可降低。如此一来,因导电图案164受到栅极线122A影响而造成显示介质300(可参考图2)转动而产生的漏光问题可获得改善。

在本实施例中,在像素阵列基板100A的俯视图中,栅极线122A的曲线段122a与数据线142的曲线段142a可选择性地部分地重叠,但本发明不以此为限。在本实施例中,在像素阵列基板100A的俯视图中,栅极线122A的曲线段122a可选择性地与触控信号线162的曲线段162a部分地重叠,但本发明不以此为限。

图4为本发明又一实施例的像素阵列基板100B的俯视示意图。图4的像素阵列基板100B与图1的像素阵列基板100类似,两者的差异在于:两者的数据线142、142B不同,且两者的导电图案164、164B不同。

请参照图4,具体而言,在本实施例中,数据线142B可不具有曲线段142a。导电图案164B可具有多个主要部164B-1、164B-2。在像素阵列基板100B的俯视图中,多个主要部164B-1、164B-2位数据线142B与栅极线122的至少一者的不同侧。举例而言,在本实施例中,导电图案164B的多个主要部164B-1、164B-2包括第一主要部164B-1及第二主要部164B-2;在像素阵列基板100B的俯视图中,第一主要部164B-1及第二主要部164B-2分别位数据线142B的相对两侧。

值得一提是,在本实施例中,通过将导电图案164B分为位于数据线142B相对两侧的多个主要部164B-1、164B-2,可降低导电图案164B与数据线142B的重叠面积及其耦合效应。如此一来,因导电图案164B受数据线142B影响造成显示介质300(可参考图2)转动而产生的漏光问题可获得改善。

图5为本发明再一实施例的像素阵列基板100C的俯视示意图。图5的像素阵列基板100C与图1的像素阵列基板100类似,两者的差异在于:两者的数据线142、142C不同,且两者的导电图案164、164C不同。

请参照图5,具体而言,在本实施例中,数据线142C可不具有曲线段142a。导电图案164C可具有多个主要部164C-1、164C-2、164C-3、164C-4。在像素阵列基板100C的俯视图中,多个主要部164C-1、164C-2、164C-3、164C-4位数据线142C与栅极线122的至少一者的不同侧。

举例而言,在本实施例中,导电图案164C的多个主要部164C-1、164C-2、164C-3、164C-4包括第一主要部164C-1、第二主要部164C-2、第三主要部164C-3及第四主要部164C-4;在像素阵列基板100C的俯视图中,第一主要部164C-1及第二主要部164C-2位数据线142C的相对两侧,且位于栅极线122的一侧(例如:上侧);在像素阵列基板100C的俯视图中,导电图案164C的第一主要部164C-1及第三主要部164C-3位于数据线142C的一侧(例如:右侧)和栅极线122的相对两侧(例如:上下侧);在像素阵列基板100C的俯视图中,第三主要部164C-3及第四主要部164C-4位数据线142C的相对两侧,且位于栅极线122的另一侧(例如:下侧)。

图6为本发明一实施例的像素阵列基板100D的俯视示意图。

图6的像素阵列基板100D与图1的像素阵列基板100类似,两者的差异在于:两者的数据线142、142D不同,且两者的导电图案164、164D不同。

请参照图6,具体而言,在本实施例中,数据线142D可不具有曲线段142a。导电图案164D可电连接至像素电极192而非浮置。

值得一提的是,在本实施例中,通过将导电图案164D电连接至像素电极192,即使导电图案164D与数据线142D/栅极线122耦合,导电图案164D仍具有与像素电极192相同的电位。由此,可避免导电图案164D对显示介质300(可参考图2)造成不良影响,进而改善漏光问题。

图7为本发明另一实施例的像素阵列基板100E的俯视示意图。图7的像素阵列基板100E与图3的像素阵列基板100A类似,两者的差异在于:在图7的实施例中,导电图案164E电连接至像素电极192。

图8为本发明又一实施例的像素阵列基板100F的俯视示意图。图8的像素阵列基板100F与图5的像素阵列基板100C类似,两者的差异在于:在图8的实施例中,导电图案164F电连接至像素电极192。

- 像素电路及其驱动方法、阵列基板、显示面板

- 像素阵列基板

- 像素阵列基板

- 像素阵列基板及显示设备

- 一种像素结构、阵列基板及液晶显示装置

- 像素阵列基板和包括像素阵列基板的显示装置

- 像素阵列基板及使用该像素阵列基板的显示面板