半导体器件及显示面板

文献发布时间:2023-06-19 18:30:43

技术领域

本发明涉及显示技术领域,具体涉及一种半导体器件及一种显示面板。

背景技术

将像素驱动电路、栅极驱动器、源极驱动器及时序控制器等电路集成在基板上(system on glass,SOG)可以极大的提高显示面板的集成度,从而降低对驱动芯片的依赖,降低成本。而为实现SOG设计,就需要使半导体器件具有更短的沟道长度、更高的迁移率及更小的体积,以提高晶体管的集成度、最大工作频率及电流密度。但现有的有源层采用平面放置,如图1所示,受曝光精度和刻蚀精度的限制,半导体器件的沟道长度在2微米以上,且沟道内存在较多的晶界,器件迁移率较低。

发明内容

本发明实施例提供一种半导体器件,可以使半导体器件具有短沟道及高迁移率。

本发明实施例提供一种半导体器件,包括衬底、有源定义部以及有源层。所述有源定义部位于所述衬底上,所述有源定义部包括在厚度方向上间隔设置的第一表面和第二表面,以及连接于所述第一表面和所述第二表面之间且呈倾斜设置的连接面。所述有源层包括位于所述第一表面上的第一掺杂部、位于所述第一掺杂部靠近所述第二表面的一侧的第二掺杂部,以及位于所述连接面上且连接于所述第一掺杂部和所述第二掺杂部之间的沟道部。

其中,所述沟道部的长度小于或等于1微米,且所述沟道部的晶粒的数量小于或等于3。

可选地,在本发明的一些实施例中,所述沟道部的长度小于或等于0.3微米,所述沟道部的晶粒数量等于1。

可选地,在本发明的一些实施例中,所述连接面与所述第一表面具有第一夹角;其中,所述第一夹角大于或等于90°且小于或等于135°。

可选地,在本发明的一些实施例中,所述半导体器件还包括第一绝缘层,所述第一绝缘层位于所述衬底和所述有源层之间,所述第一绝缘层包括所述有源定义部。

可选地,在本发明的一些实施例中,所述第一表面为所述第一绝缘层的顶面,所述第二表面为所述第一绝缘层的底面且与所述第一表面平行,所述连接面为所述第一绝缘层的外侧面。

可选地,在本发明的一些实施例中,所述第一绝缘层设有凹槽,所述第一表面为所述凹槽的底面,所述第二表面为所述第一绝缘层的顶面,所述连接面为所述凹槽的侧表面。

可选地,在本发明的一些实施例中,所述半导体器件还包括栅极层,所述栅极层位于所述有源层上,所述栅极层包括对应于所述沟道部的栅极,所述栅极相对于所述第一表面朝向所述沟道部倾斜,且呈环形。

可选地,在本发明的一些实施例中,所述半导体器件还包括栅极层,所述栅极层位于所述衬底和所述有源层之间,所述栅极层包括栅极,所述栅极包括所述有源定义部。

可选地,在本发明的一些实施例中,所述第一表面为所述栅极的顶面,所述第二表面为所述栅极的底面且与所述第一表面平行,所述连接面为所述栅极的外侧面。

可选地,在本发明的一些实施例中,所述半导体器件还包括源漏极层,所述源漏极层位于所述有源层上,所述源漏极层包括与所述第一掺杂部电性连接的第一电极和与所述第二掺杂部电性连接的第二电极,所述第一电极连接于所述第一掺杂部的中部。

本发明还提供一种显示面板,所述显示面板包括任一上述的半导体器件。

本发明提供一种半导体器件及一种显示面板,半导体器件包括衬底、有源定义部及有源层。有源定义部位于衬底上,有源定义部包括在厚度方向上间隔设置的第一表面和第二表面,以及连接于第一表面和第二表面之间且呈倾斜设置的连接面。有源层包括位于第一表面上的第一掺杂部、位于第一掺杂部靠近第二表面的一侧的第二掺杂部,以及位于连接面上且连接于第一掺杂部和第二掺杂部之间的沟道部。通过使沟道部的长度小于或等于1微米,且沟道部的晶粒的数量小于或等于3,以使半导体器件在连接面上生成的晶粒数量较少,从而控制晶界数量,以提高半导体器件的迁移率,利于使半导体器件实现短沟道及高迁移率的设计。显示面板包括半导体器件。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是现有技术中半导体器件的结构示意图;

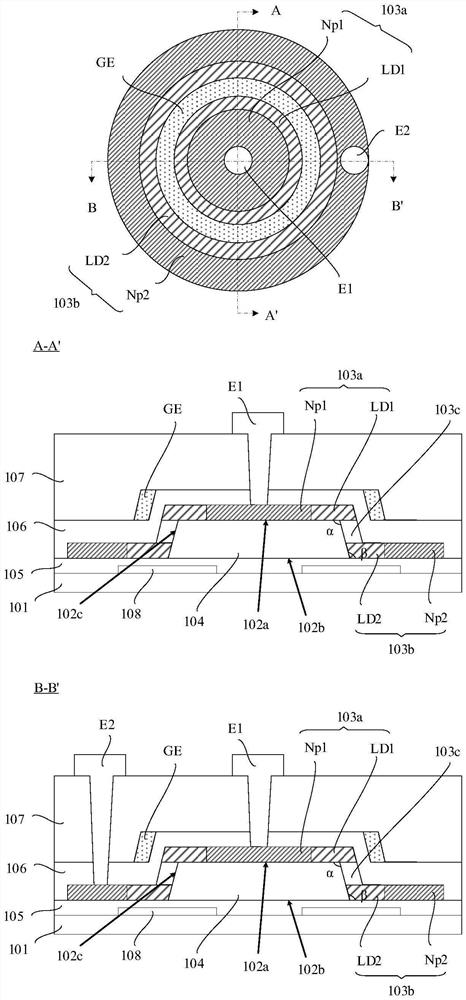

图2A~图2E是本发明实施例提供的半导体器件的结构示意图;

图3A~图3G是图2A所示的半导体器件的制备过程示意图;

图4是本发明实施例提供的显示面板的结构示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。在本发明中,在未作相反说明的情况下,使用的方位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。

具体地,如图1是现有技术中半导体器件的结构示意图。其中,poly表示有源层,GE表示栅极,SD表示源漏极层。在现有技术中,有源层poly均设置在同一平面内,受曝光、刻蚀工艺的限制,半导体器件的沟道长度一般在2微米以上,且沟道内存在较多晶界,半导体器件的迁移率较低。

如图2A~图2E是本发明实施例提供的半导体器件的结构示意图。本发明实施例提供一种半导体器件,包括衬底101、有源定义部以及有源层。

可选地,所述衬底101包括柔性衬底和刚性衬底。可选地,所述衬底101包括玻璃、聚酰亚胺等。

所述有源定义部位于所述衬底101上,所述有源定义部包括第一表面102a、第二表面102b及连接面102c。所述第一表面102a和所述第二表面102b在所述半导体器件的厚度方向上间隔设置(即所述第一表面102a和所述第二表面102b位于不同的平面上),所述连接面102c连接于所述第一表面102a和所述第二表面102b之间且呈倾斜设置。

可选地,所述有源定义部可呈凸台状设计,也可呈凹槽状设计。可选地,在所述有源定义部呈凸台状设计且所述有源定义部具有两平面时,所述第一表面102a为凸台的顶面,所述第二表面102b为凸台的底面。可选地,在所述有源定义部呈凸台状设计且所述有源定义部具有三平面时,所述第一表面102a为凸台的顶面,所述第二表面102b为位于所述凸台的顶面和所述凸台的底面之间的平面。可选地,在所述有源定义部呈凹槽状设计时,所述第一表面102a为凹槽的底面,所述第二表面102b为凹槽的顶面。

所述有源层包括第一掺杂部103a、第二掺杂部103b及沟道部103c。可选地,所述第一掺杂部103a位于所述第一表面102a上;所述第二掺杂部103b位于所述第一掺杂部103a靠近所述第二表面102b的一侧,所述沟道部103c位于所述连接面102c上且连接于所述第一掺杂部103a和所述第二掺杂部103b之间。

可选地,在所述有源定义部呈凸台状设计时,所述第二掺杂部103b位于所述第一掺杂部103a靠近所述第二表面102b的一侧则表示所述第二掺杂部103b位于与所述第一表面102a不同表面的表面上。可选地,在所述有源定义部呈凸台状设计,且所述有源定义部具有两平面时,所述第二掺杂部103b位于与所述第二表面102b相接触的表面上。可选地,在所述有源定义部呈凸台状设计,且所述有源定义部具有三平面时,所述第二掺杂部103b位于所述第二表面102b上。可选地,在所述有源定义部呈凹槽状设计时,所述第二掺杂部103b位于所述第一掺杂部103a靠近所述第二表面102b的一侧则表示所述第二掺杂部103b可位于所述第二表面102b上。

可选地,所述沟道部103c的长度小于或等于1微米,且所述沟道部103c的晶粒的数量小于或等于3,以使所述半导体器件具有较短的沟道长度,从而使所述半导体器件在所述连接面102c上生成的晶粒数量较少,以控制晶界的数量,继而提高半导体器件的迁移率,有利于使半导体器件实现短沟道及高迁移率的设计。

可选地,所述沟道部103c的长度等于1微米、0.95微米、0.9微米、0.85微米、0.8微米、0.75微米、0.7微米、0.65微米、0.6微米、0.55微米、0.5微米、0.45微米、0.4微米、0.35微米、0.3微米、0.25微米、0.2微米、0.15微米、0.1微米、0.09微米、0.08微米、0.07微米、0.06微米、0.05微米、0.04微米、0.03微米、0.02微米或0.01微米等。

可选地,所述沟道部103c的晶粒的数量等于3个、2个或1个。

可选地,所述沟道部103c的长度小于或等于1个晶粒的长度,以使所述沟道部的晶粒数量等于1,从而使所述半导体器件在所述连接面102c上仅生成一个晶粒,继而使得所述半导体器件在载流子迁移方向上仅通过一个晶粒,而不通过晶界,以大幅度提升所述半导体器件的迁移率。

可选地,所述沟道部103c的长度小于或等于0.3微米,以适配现有的准分子激光退火(Excimer laser annealing,ELA)工艺所形成的晶粒尺寸。目前ELA晶化形成的晶粒尺寸在0.3微米左右,而通过控制所述连接面102c的长度小于或等于0.3微米,可使沿着沟道长度方向,所述连接面102c上只存在一个晶粒,如此,便可使半导体器件在载流子迁移方向上只通过一个晶粒,而不存通过晶界,从而使半导体器件的迁移率大幅提升。

可选地,所述沟道部103c围绕所述第一掺杂部103a设置,所述第二掺杂部103b围绕所述沟道部103c设置,且由于所述第一掺杂部103a和所述第二掺杂部103b位于不同的平面上,因而使得所述半导体器件具有的沟道宽度即为所述沟道部103c的周长,因此可在有限的空间内增大所述半导体器件的沟道宽度,从而提高所述半导体器件的开态电流。

可选地,在所述有源定义部呈凹槽状设计时,所述连接面102c与所述第一表面102a具有第一夹角α;其中,所述第一夹角α大于或等于90°且小于或等于135°,以使所述有源层在采用ELA工艺结晶时,在所述第一夹角α处形成籽晶,并沿着所述连接面102c进行生长,利于使所述沟道部103c的晶粒的数量小于或等于3,以使所述半导体器件的沟道长度控制在1微米及以下。

可选地,所述第一夹角α等于90°、91°、92°、93°、94°、95°、……、100°、……、105°、……、110、……、115°、……、120°、……、125°、……、130°、131°、132°、133°、134°、135°。

可选地,在所述有源定义部呈凸台状设计,且所述有源定义部具有两平面时,所述连接面102c与和所述第二表面102b相接触的表面具有第二夹角β,所述第二夹角β大于或等于90°且小于或等于135°,以使所述有源层在采用ELA工艺结晶时,在所述第二夹角β处形成籽晶,并沿着所述连接面102c进行生长,利于使所述沟道部103c的晶粒的数量小于或等于3,以使所述半导体器件的沟道长度控制在1微米及以下。

可选地,在所述有源定义部呈凸台状设计,且所述有源定义部具有三平面时,所述连接面102c与所述第二表面102b具有第二夹角β,所述第二夹角β大于或等于90°且小于或等于135°,以使所述有源层在采用ELA工艺结晶时,在所述第二夹角β处形成籽晶,并沿着所述连接面102c进行生长,利于使所述沟道部103c的晶粒的数量小于或等于3,以使所述半导体器件的沟道长度控制在1微米及以下。

可选地,所述第二夹角β等于90°、91°、92°、93°、94°、95°、……、100°、……、105°、……、110、……、115°、……、120°、……、125°、……、130°、131°、132°、133°、134°、135°。

可以理解的,在所述第一表面102a和所述第二表面102b平行时,所述第一夹角α和所述第二夹角β中的一个被确定后,所述第一夹角α和所述第二夹角β中的另一个也相继被确定;即将所述第一夹角α确定为大于或等于90°且小于或等于135°,就可以使所述第二夹角β被确定为大于或等于90°且小于或等于135°。

可选地,所述第一表面102a距所述第二表面102b之间的距离小于或等于7000埃米,以在所述第一夹角α大于或等于90°且小于或等于135°,或所述第二夹角β大于或等于90°且小于或等于135°的基础上,使所述连接面102c的长度小于或等于1微米,以利于使所述半导体器件的沟道长度控制在1微米及以下。

可选地,所述第一表面102a距所述第二表面102b之间的距离等于7000埃米、6900埃米、6800埃米、6700埃米、6500埃米、6000埃米、5500埃米、5000埃米、4500埃米、4000埃米、3500埃米、3000埃米、2500埃米、2000埃米、1500埃米或1000埃米等。

通过控制所述第一表面102a距所述第二表面102b之间的距离以及所述第一夹角α或所述第二夹角β,可使所述半导体器件的沟道长度很容易的被控制在1微米及以下,即可使所述半导体器件的沟道长度可以被缩小至0.01微米~1微米,所述半导体器件的沟道宽度可控制在0.3微米~10微米。

可选地,所述半导体器件的沟道宽度等于0.3微米、0.4微米、0.5微米、……、1微米、……、1.5微米、……、2微米、……、2.5微米、……、3微米、……、4微米、……、5微米、……、6微米、……、7微米、……、8微米、……、8.5微米、……、9微米、……、9.5微米、9.6微米、9.7微米、9.8微米、9.9微米或10微米。

可选地,可通过不同的膜层实现有源定义部的设计。具体的,如图2A~图2E所示。

请继续参阅图2A~图2D,所述半导体器件还包括第一绝缘层104,所述第一绝缘层104位于所述衬底101和所述有源层之间,所述第一绝缘层104包括所述有源定义部。

请继续参阅图2A,所述第一表面102a为所述第一绝缘层104的顶面,所述第二表面102b为所述第一绝缘层104的底面且与所述第一表面102a平行,所述连接面102c为所述第一绝缘层104的外侧面,所述第一表面102a和所述第二表面102b对应为所述有源定义部呈凸台状设计时所具有的两平面。所述第一掺杂部103a位于所述第一绝缘层104的顶面上,所述第二掺杂部103b位于与所述第二表面102b相接触且未被所述第一绝缘层104覆盖的膜层表面上,所述沟道部103c位于所述第一绝缘层104的外侧面上且连接于所述第一掺杂部103a和所述第二掺杂部103b之间。

可选地,所述第一绝缘层104和所述衬底101之间还设置有缓冲层105,所述第一绝缘层104的底面(即所述第二表面102b)与所述缓冲层105的顶面相接触,所述第二掺杂部103b位于所述缓冲层105未被所述第一绝缘层104覆盖的顶面上,所述第一绝缘层104的外侧面与所述缓冲层105的顶面之间形成所述第二夹角β,所述第一绝缘层104的外侧面与所述第一绝缘层104的顶面之间形成所述第一夹角α。

可选地,所述第一绝缘层104复用作阻挡层,以降低制程工序及制程难度。

请继续参阅图2B,所述第一绝缘层104设有凹槽,所述第一表面102a为所述凹槽的底面,所述第二表面102b为所述第一绝缘层104的顶面,所述连接面102c为所述凹槽的侧表面,所述第一掺杂部103a位于所述凹槽的底面上,所述第二掺杂部103b位于所述第二表面102b上,所述沟道部103c位于所述凹槽的侧表面上且连接于所述第一掺杂部103a和所述第二掺杂部103b之间,所述凹槽的侧表面与所述凹槽的底面之间形成所述第一夹角α,所述凹槽的侧表面与所述第一绝缘层104的顶面之间形成所述第二夹角β。

可选地,所述第一绝缘层104复用作缓冲层,以降低制程工序及制程难度。

请继续参阅图2C,所述第一表面102a为所述第一绝缘层104的顶面,所述第二表面102b为位于所述第一绝缘层104的顶面和所述第一绝缘层104的底面之间的平面,所述连接面102c为连接于所述第一表面102a和所述第二表面102b之间的侧面,所述第一表面102a、所述第二表面102b和所述第一绝缘层104的底面对应为所述有源定义部呈凸台状设计时所具有的三平面。所述第一掺杂部103a位于所述第一绝缘层104的顶面上,所述第二掺杂部103b位于所述第二表面102b上,所述沟道部103c位于所述连接面102c上且连接于所述第一掺杂部103a和所述第二掺杂部103b之间。所述连接面102c与所述第二表面102b之间形成所述第二夹角β,所述连接面102c与所述第一绝缘层104的顶面之间形成所述第一夹角α。

请继续参阅图2D,所述第一绝缘层104可设置成多层的形式。如所述第一绝缘层104可包括第一子绝缘层1041和第二子绝缘层1042,所述第一子绝缘层1041位于所述第二子绝缘层1042和所述衬底101之间,所述第二子绝缘层1042中设有过孔以暴露出所述第一子绝缘层1041的顶面。其中,所述第一表面102a为所述过孔所暴露出的所述第一子绝缘层1041的顶面,所述第二表面102b为所述第二子绝缘层1042的顶面,所述连接面102c为所述过孔的侧表面,所述第一掺杂部103a位于所述过孔所暴露出的所述第一子绝缘层1041的顶面上,所述第二掺杂部103b位于所述第二子绝缘层1042的顶面上,所述沟道部103c位于所述过孔的侧表面上,所述过孔的侧表面与所述过孔所暴露出的所述第一子绝缘层1041的顶面之间形成所述第一夹角α,所述过孔的侧表面与所述第一子绝缘层1041的顶面之间形成所述第二夹角β。

请继续参阅图2A~图2D,所述半导体器件还包括栅极层,所述栅极层位于所述有源层上,所述栅极层包括对应于所述沟道部103c的栅极GE,所述栅极GE相对于所述第一表面102a朝向所述沟道部103c倾斜,且呈环形,以使所述半导体器件具有较短的沟道长度和较大的沟道宽度。

可选地,所述半导体器件还包括源漏极层,所述源漏极层位于所述有源层上,所述源漏极层包括与所述第一掺杂部103a电性连接的第一电极E1和与所述第二掺杂部103b电性连接的第二电极E2,以通过同一制程同时制得所述第一电极E1和所述第二电极E2,降低制程工序和制程难度。

可选地,所述第一电极E1连接于所述第一掺杂部103a的中部,以保持结构的对称性,从而使所述半导体器件具有较均匀的性能。

请继续参阅图2A和图2C,所述栅极GE距所述第二电极E2的最小距离大于或等于安全距离,以防止所述栅极GE和所述第二电极E2之间出现短路等问题。请继续参阅图2B和图2D,所述栅极GE距所述第一电极E1的最小距离大于或等于安全距离,以防止所述栅极GE和所述第一电极E1之间出现短路等问题。可选地,所述安全距离可等于3微米。可选地,请继续参阅图2B和图2D,所述第二电极E2距所述沟道部103c靠近所述第二掺杂部103b的一端的距离需在保持安全距离的条件下尽量小(如所述第二电极E2距所述沟道部103c靠近所述第二掺杂部103b的一端的距离等于安全距离),以避免所述第二电极E2距所述沟道部103c靠近所述第二掺杂部103b的一端的距离太大而引入串联电阻,影响所述半导体器件的性能。

可以理解的,所述第二掺杂部103b的宽度可根据实际需求进行设置。所述第一绝缘层104的材料包括无机材料。可选地,所述第一绝缘层104包括氧化硅等材料。

请继续参阅图2A~图2D,所述半导体器件还包括栅绝缘层106和层间介电层107,所述栅绝缘层106位于所述栅极层和所述有源层之间,所述层间介电层107位于所述源漏极层和所述栅极层之间,所述第一电极E1和所述第二电极E2分别通过同时贯穿所述绝缘层106和所述层间介电层107的过孔电性连接于所述第一掺杂部和所述第二掺杂部。

可选地,请继续参阅图2A~图2D,所述第一掺杂部103a还包括第一轻掺杂部LD1和第一重掺杂部Np1,所述第二掺杂部103b还包括第二轻掺杂部LD2和第二重掺杂部Np2。其中,所述第一电极E1与所述第一重掺杂部Np1电性连接,所述第二电极E2与所述第二重掺杂部Np2电性连接,所述第一轻掺杂部LD1位于所述沟道部103c和所述第一重掺杂部Np1之间,所述第二轻掺杂部LD2位于所述沟道部103c和所述第二重掺杂部Np2之间。

请继续参阅图2E,所述半导体器件还包括栅极层,所述栅极层位于所述衬底101和所述有源层之间,所述栅极层包括栅极GE,所述栅极GE包括所述有源定义部。

可选地,所述第一表面102a为所述栅极GE的顶面,所述第二表面102b为所述栅极GE的底面且与所述第一表面102a平行,所述连接面102c为所述栅极GE的外侧面,所述第一掺杂部103a位于所述栅极GE的顶面上,所述第二掺杂部103b位于与所述第二表面102b相接触且未被所述栅极GE覆盖的膜层表面上,所述沟道部103c位于所述栅极GE的外侧面上且连接于所述第一掺杂部103a和所述第二掺杂部103b之间。

可选地,所述栅极层和所述衬底101之间还设置有缓冲层105,所述栅极GE的底面(即所述第二表面102b)与所述缓冲层105的顶面相接触,所述第二掺杂部103b位于所述缓冲层105未被所述栅极GE覆盖的顶面上,所述栅极GE的外侧面与所述缓冲层105的顶面之间形成所述第二夹角β,所述栅极GE的外侧面与所述栅极GE的顶面之间形成所述第一夹角α。

可选地,所述栅极层的制备材料包括金属材料。

可选地,所述半导体器件还包括栅绝缘层106和层间介电层107,所述栅绝缘层106位于所述栅极层和所述有源层之间,所述层间介电层107位于所述源漏极层和所述有源层之间,所述第一电极E1和所述第二电极E2分别通过贯穿所述层间介电层107的过孔电性连接所述第一掺杂部和所述第二掺杂部。

可选地,在俯视视角下,所述第一表面102a呈圆形,所述第二表面102b和所述连接面102c均呈环形,以使所述半导体器件在具有较短的沟道长度的同时具有较大的沟道宽度,从而有利于实现半导体器件的高迁移率和高开态电流的设计。

可选地,所述半导体器件还包括位于所述有源定义部和所述衬底101之间的遮光层108。可选地,所述遮光层108包括对应于所述沟道部103c设置的遮光部,以降低光线对半导体器件的影响。

相较于图2E所示的半导体器件,图2A~图2D所示的半导体器件,由于栅极GE设置在所述连接面102c上,因而可以利用栅极自对准掺杂形成轻掺杂漏(Lightly DopedDrain,LDD)结构,使得半导体器件的电性更加稳定,且栅极GE的厚度可单独调试,不用受到所述连接面102c的限制。

以图2A所示的半导体器件结构为例对半导体器件的制备过程进行简要说明,图2B~图2E所示的半导体结构的制备过程与图2A的制备逻辑相似,在此不再进行赘述。

具体的,图3A~图3G是图2A所示的半导体器件的制备过程示意图;本申请还提供一种半导体器件的制备方法,包括以下步骤:

步骤S100:提供衬底101,如图3A所示。

步骤S200:在所述衬底101上制备有源定义部。其中,所述有源定义部包括第一表面102a、第二表面102b及连接面102c。所述第一表面102a和所述第二表面102b在所述半导体器件的厚度方向上间隔设置,所述连接面102c连接于所述第一表面102a和所述第二表面102b之间且呈倾斜设置,如图3B所示。

步骤S300:制备所述有源层。其中,所述有源层包括第一掺杂部103a、第二掺杂部103b及沟道部103c。所述第一掺杂部103a位于所述第一表面102a上;所述第二掺杂部103b位于所述第一掺杂部103a靠近所述第二表面102b的一侧,所述沟道部103c位于所述连接面102c上且连接于所述第一掺杂部103a和所述第二掺杂部103b之间,如图3C~图3D所示。

可选地,在所述步骤S200中,包括在所述衬底101上制备第一绝缘层104,所述第一绝缘层104包括所述有源定义部。在所述步骤S300之后,还包括:

步骤S400:制备栅绝缘层106和栅极层。其中,所述栅极层包括对应所述沟道部103c设置的栅极GE,如图3E所示。

步骤S500:制备层间介电层107,并制备同时贯穿所述层间介电层107和所述栅绝缘层106且分别暴露出部分所述第一掺杂部103a和所述第二掺杂部103b的过孔,如图3F所示。

步骤S600:制备源漏极层。其中,所述源漏极层包括与所述第一掺杂部103a电性连接的第一电极E1和与所述第二掺杂部103b电性连接的第二电极E2,如图3G所示。

可选地,在所述步骤S200之前,还包括在所述衬底101上制备遮光层108及缓冲层105。可选地,所述遮光层108包括对应于所述沟道部103c设置的遮光部。

可选地,在所述步骤S200中,包括在所述衬底101上制备栅极层及栅绝缘层106,所述栅极层包括所述有源定义部。在所述步骤S300之后,还包括:制备层间介电层107并制备贯穿所述层间介电层107且分别暴露出部分所述第一掺杂部103a和所述第二掺杂部103b的过孔;以及制备源漏极层,所述源漏极层包括与所述第一掺杂部103a电性连接的第一电极E1和与所述第二掺杂部103b电性连接的第二电极E2。

本发明还提供一种显示面板,所述显示面板包括任一上述的半导体器件。

如图4是本发明实施例提供的显示面板的结构示意图,本发明还提供一种显示面板,包括上述的半导体器件(如图4中的401所示)。

可选地,所述显示面板包括自发光显示面板、被动式发光显示面板、触控显示面板等。

可选地,所述显示面板还包括平坦层402、底电极403、保护层404及顶电极405。其中,所述平坦层402位于所述源漏极层上;所述底电极403位于所述平坦层402和所述保护层404之间;所述顶电极405位于所述保护层404上,且与第一电极E1或第二电极E2电性连接。

可选地,所述底电极403为触控电极,所述顶电极405为像素电极。可选地,所述底电极403和所述顶电极405均为透明电极。

可选地,所述显示面板还包括阵列基板、彩膜基板及位于所述阵列基板和所述彩膜基板之间的液晶分子,所述阵列基板和所述彩膜基板相对设置,所述阵列基板包括所述半导体器件。

可选地,所述显示面板还包括发光器件,所述发光器件与第一电极E1或第二电极E2电性连接。可选地,所述发光器件包括有机发光二极管、次毫米发光二极管及微型发光二极管等。

本发明还提供一种显示装置,所述显示装置包括任一上述的显示面板。可以理解地,所述显示装置包括可移动显示装置(如笔记本电脑、手机等)、固定终端(如台式电脑、电视等)、测量装置(如运动手环、测温仪等)等。

本发明提供的半导体器件可沿用现有工艺进行制备。即在现有工艺下即可制得具有短沟道、高迁移率的半导体器件,有利于提高器件的集成度、最大工作频率和电流密度,从而在玻璃基板上实现驱动电路集成设计。

本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

- 发光器件以及制造具有该发光器件的显示面板的方法

- 显示面板及其制作方法、电致发光器件、显示装置

- 一种显示面板及其显示器件

- 微显示器件及其制备方法、显示面板

- 微显示器件及其制备方法、显示面板

- 一种半导体器件制程方法、半导体器件及显示面板

- 半导体装置、半导体器件模块、显示面板驱动器以及显示模块