应用于芯片的N电极及制备方法和VCSEL芯片

文献发布时间:2023-06-19 18:32:25

技术领域

本发明涉及光电子、微电子领域及功率器件技术领域,具体而言,本发明涉及应用于芯片的N电极及制备方法和VCSEL芯片。

背景技术

垂直腔面发射激光器(Vertical Cavity Surface Emitting Laser,VCSEL)有别于LED(Light Emitting Diode,发光二极管)和LD(Laser Diode,激光二极管)等其它光源,具有体积小、圆形输出光斑、单纵模输出、阈值电流小且易集成大面积阵列等优点,被广泛应用于光通信、光互连和光存储等领域。随着科学技术的不断发展,各种各样的VCSEL芯片已广泛应用于人们的日常生活、工作以及工业中,为人们的生活带来了极大的便利。

VCSEL芯片中的N电极金属普遍采用蒸镀AuGeNi合金+Au的方式。其中,AuGeNi合金中各金属的比例为:金属Ni占总摩尔质量的3%~5%,Au占除Ni之外摩尔质量的88%,Ge占除Ni之外摩尔质量的12%。AuGeNi合金层与N型GaAs衬底直接接触,Au层设置在AuGeNi合金层的远离GaAs衬底的表面上。电极金属体系制备完成后使用RTA设备(快速退火炉)在400~450℃下进行退火处理,30s~3min的无氧氛围退火后,N电极与N型GaAs之间会形成欧姆接触,接触电阻Rc为10

但是,该技术具有如下缺点:

1、AuGeNi合金需要使用400~450℃、30s~3min的快速热处理对合金层进行退火处理,来降低N电极与N型GaAs衬底之间的接触电阻。而VCSEL芯片中除了N电极,还包括其它多层材料,各层材料的热膨胀系数存在差异,N电极的快速热处理的高温工艺会对器件可靠性存在不利影响,需尽量降低退火温度,但是温度过低又无法达到对AuGeNi合金层进行退火处理的目的。

2、AuGeNi合金为Au、Ge和Ni三元金属合金,各金属在同一蒸汽压下熔点不一样,蒸发速率也不一样。因此,在蒸镀工艺中,会导致电极中各金属的比例较标准值会逐渐出现偏差,最终影响与N型GaAs的接触电阻。

3、AuGeNi合金的共熔温度在350℃~370℃,AuGeNi合金要形成良好欧姆接触的退火温度已超过AuGeNi层共熔温度,从而导致AuGeNi层经过高温退火工艺后,在金属电极表面起球,从而出现在金属表面形成小球状合金点(球缩现象),不仅影响产品外观,也会影响后续SiN与电极的粘附。

发明内容

本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的一个目的在于提出应用于芯片的N电极及制备方法和VCSEL芯片。本发明的Pd层和Ge层通过较低的退火温度就能实现与GaAs衬底具有较低的接触电阻,从而进一步提高了器件的可靠性。同时,Pd层为Pd金属单质层,Ge层为Ge金属单质层,两层可分别蒸镀形成,在蒸镀工艺中便于实现各金属比例的控制,因此不存在AuGeNi合金成分出现偏差的问题。另外,本发明通过设置Pd层和Ge层作为N电极,退火后具有更好的金属表面外观,便于后续PECVD SiN沉积工艺。

在本发明的一个方面,本发明提出了一种应用于芯片的N电极。根据本发明的实施例,该应用于芯片的N电极包括:Pd层,所述Pd层设置在所述芯片的GaAs衬底上;Ge层,所述Ge层设置在所述Pd层的远离所述GaAs衬底的至少部分表面上;金属黏附层,所述金属黏附层设置在所述Ge层的远离所述Pd层的至少部分表面上;金属阻挡层,所述金属阻挡层设置在所述金属黏附层的远离所述Ge层的至少部分表面上;金属打线层,所述金属打线层设置在所述金属阻挡层的远离所述金属黏附层的至少部分表面上。

根据本发明上述实施例的应用于芯片的N电极,Pd层和Ge层通过较低的退火温度就能实现与GaAs衬底具有较低的接触电阻,从而进一步提高了器件的可靠性。同时,Pd层为Pd金属单质层,Ge层为Ge金属单质层,两层可分别蒸镀形成,在蒸镀工艺中便于实现各金属比例的控制,因此不存在AuGeNi合金成分出现偏差的问题。另外,本发明通过设置Pd层和Ge层作为N电极,退火后具有更好的金属表面外观,便于后续PECVD SiN沉积工艺。

另外,根据本发明上述实施例的应用于芯片的N电极还可以具有如下附加的技术特征:

在本发明的一些实施例中,所述Pd层的厚度为40~60nm。

在本发明的一些实施例中,所述Ge层的厚度为100~150nm。

在本发明的一些实施例中,所述金属黏附层为Ti层。

在本发明的一些实施例中,所述金属黏附层的厚度为40~60nm。

在本发明的一些实施例中,所述金属阻挡层为Pt层;和/或,所述金属阻挡层的厚度为40~60nm。

在本发明的一些实施例中,所述金属打线层为Au层;和/或,所述金属打线层的厚度为300~500nm。

在本发明的另一方面,本发明提出了一种制备上述的N电极的方法,包括:

(1)采用蒸镀的方法在GaAs衬底上依次形成Pd层、Ge层、金属黏附层、金属阻挡层和金属打线层;

(2)对所述Pd层、所述Ge层、所述金属黏附层、所述金属阻挡层和所述金属打线层进行退火处理。

本发明实施例所述的制备上述N电极的方法,该方法简单易实施,且该方法通过较低的退火温度就能实现与GaAs衬底具有较低的接触电阻,从而进一步提高了器件的可靠性。同时,分别蒸镀形成Pd金属单质层和Ge金属单质层,在蒸镀工艺中便于实现各金属比例的控制,因此不存在AuGeNi合金成分出现偏差的问题。另外,本发明通过形成Pd层和Ge层作为N电极,退火后具有更好的金属表面外观,便于后续PECVD SiN沉积工艺。

另外,根据本发明上述实施例的方法还可以具有如下附加的技术特征:

在本发明的一些实施例中,所述退火处理的温度为250~300℃,所述退火处理的时间为10~20min。

在本发明的第三个方面,本发明提出了一种VCSEL芯片。根据本发明的实施例,该VCSEL芯片包括以上实施例所述的N电极或采用以上实施例所述方法制得的N电极。由此,进一步提高了VCSEL芯片的可靠性,进一步简化了VCSEL芯片的制备流程,节省了能源和成本。

本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

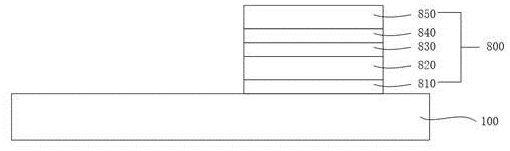

图1为本发明实施例的应用于芯片的N电极的结构示意图;

图2为本发明实施例的VCSEL芯片的结构示意图。

附图标注,100-GaAs衬底,200-NDBR层,300-MQW层,400-氧化层,500-PDBR层,600-P接触层,700-P电极,800-N电极,810-Pd层,820-Ge层,830-金属黏附层,840-金属阻挡层,850-金属打线层,900-SiN钝化层。

具体实施方式

下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个、四个、五个、六个等,除非另有明确具体的限定。

在本发明中,除非另有明确的规定和限定,“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系,除非另有明确的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

在本发明中,除非另有明确的规定和限定,第一特征在第二特征“上”或“下”可以是第一和第二特征直接接触,或第一和第二特征通过中间媒介间接接触。而且,第一特征在第二特征“之上”、“上方”和“上面”可是第一特征在第二特征正上方或斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”可以是第一特征在第二特征正下方或斜下方,或仅仅表示第一特征水平高度小于第二特征。

在本发明的一个方面,本发明提出了一种应用于芯片的N电极。参考图1,根据本发明的实施例,所述N电极800包括:Pd层810,所述Pd层810设置在所述芯片的GaAs衬底100上;Ge层820,所述Ge层820设置在所述Pd层810的远离所述GaAs衬底100的至少部分表面上;金属黏附层830,所述金属黏附层830设置在所述Ge层820的远离所述Pd层810的至少部分表面上;金属阻挡层840,所述金属阻挡层840设置在所述金属黏附层830的远离所述Ge层820的至少部分表面上;金属打线层850,所述金属打线层850设置在所述金属阻挡层840的远离所述金属黏附层830的至少部分表面上。由此,Pd层810和Ge层820通过较低的退火温度就能实现与GaAs衬底100具有较低的接触电阻,从而进一步提高了器件的可靠性。同时,Pd层810为Pd金属单质层,Ge层820为Ge金属单质层,两层可分别蒸镀形成,在蒸镀工艺中便于实现各金属比例的控制,因此不存在AuGeNi合金成分出现偏差的问题。另外,本发明通过设置Pd层810和Ge层820作为N电极,退火后具有更好的金属表面外观,便于后续PECVD SiN沉积工艺。

下面对本发明提出的N电极能够实现上述有益效果的原理进行详细说明:

第一,本发明通过在GaAs衬底100的表面依次设置Pd层810和Ge层820,在GaAs上设置的部分Pd与GaAs界面发生扩散,在界面处形成富Pd的PdxGayAs的化合物,从而在GaAs表面留下Ga空位;当进行退火后,衬底表面部分GaAs分解,Ga扩散到接触层,在GaAs中继续产生Ga的空位,同时Ge会穿过Pd层,占据Ga的空位,使GaAs表面形成重掺的n

需要说明的是,必须在GaAs衬底100的表面依次设置Pd层810和Ge层820,若在GaAs衬底100的表面依次设置Ge层和Pd层,即使退火时间再长,也不能获得良好的欧姆特性的接触。

第二,Pd层810为Pd金属单质层,Ge层820为Ge金属单质层,两层可分别蒸镀形成,在蒸镀工艺中便于实现各金属比例的控制,因此不存在AuGeNi合金中的各金属成分含量出现偏差的问题。因此,与现有技术相比,本发明通过单独设置Pd层810和Ge层820,进一步降低了与N型GaAs衬底100的接触电阻。

第三,本发明通过设置Pd层810和Ge层820作为N电极,退火后具有更好的金属表面外观,便于后续PECVD SiN沉积工艺。现有技术中,AuGeNi合金要形成良好欧姆接触需要较高的退火温度,已超过合金金属共熔温度,导致AuGe合金退火中易起球,造成外观差。而Pd层和Ge层的退火温度较低,无起球现象,故具有良好外观。

根据本发明的一个具体实施例,所述Pd层810的厚度为40~60nm,将Pd层810的厚度限定在上述范围内,退火后,可以形成良好的欧姆接触。具体地,如果Pd层810的厚度过小,会导致Pd扩散进GaAs的量较少,退火后无法获得良好的欧姆接触;如果Pd层810的厚度过大,会导致退火后,由于Ge难以穿过Pd层占据Ga的空位,也无法获得良好的欧姆接触。

根据本发明的再一个具体实施例,所述Ge层820的厚度为100~150nm,将Ge层820的厚度限定在上述范围内,退火后,可以形成良好的欧姆接触。具体地,如果Ge层820的厚度过小,会导致退火后,占据Ga空位的Ge较少,无法获得良好的欧姆接触;如果Ge层820的厚度过大,会导致退火后,未穿过Pd层的Ge厚度过大,由于Ge金属电阻较大,会导致电极金属整体电阻较大。

在本发明的实施例中,金属黏附层830的作用是作为Ge层820和金属阻挡层840的黏附层,增加Ge层820和金属阻挡层840之间的黏附性。具体地,金属黏附层830可以为Ti层,Ti层的粘性较强。进一步地,金属黏附层830的厚度为40~60nm,将金属黏附层830的厚度限定在上述范围内,进一步使金属黏附层兼具对Ge层与Pt层的黏附效果,且不会造成能源与成本浪费。

在本发明的实施例中,金属阻挡层840的作用是作为金属黏附层830和金属打线层850之间的阻挡层,避免金属打线层850(例如Au层)与金属黏附层830(例如Ti层)之间发生金属合金化现象,从而避免了金属打线层850(例如Au层)与金属黏附层830(例如Ti层)因金属合金化现象而导致的韧性降低、易从N电极上剥落等。具体地,金属阻挡层840可以为Pt层,Pt层的性质较稳定,不易发生合金化。进一步地,金属阻挡层840的厚度为40~60nm,将金属阻挡层840的厚度限定在上述范围内,进一步使金属阻挡层兼具阻挡Ti层与Au层的效果,防止Ti层与Au层界面产生金属合金化现象,且避免了造成能源与成本浪费。

在本发明的实施例中,金属打线层850的作用是作为打线层,便于后续打线工艺中金线与电极的黏附。具体地,金属打线层850可以为Au层。进一步地,金属打线层850的厚度为300~500nm,将金属打线层850的厚度限定在上述范围内,进一步使金属打线层兼具与后续工艺金线打线的效果,且避免了造成能源与成本浪费。

在本发明的另一方面,本发明提出了一种制备上述的N电极的方法,包括:

S100:在GaAs衬底上依次形成Pd层、Ge层、金属黏附层、金属阻挡层和金属打线层。

在该步骤中,采用蒸镀的方法在GaAs衬底上依次形成Pd层、Ge层、金属黏附层、金属阻挡层和金属打线层。

S200:退火处理。

在该步骤中,在无氧氛围下,同时对所述Pd层、所述Ge层、所述金属黏附层、所述金属阻挡层和所述金属打线层进行退火处理,经过退火处理后,Pd层和Ge层实现了与N型GaAs衬底之间较低的欧姆接触(能达到10

根据本发明的一个具体实施例,所述退火处理的温度为250~300℃,所述退火处理的时间为10~20min,由此,Pd层和Ge层通过较低的退火温度就能实现与GaAs衬底具有较低的接触电阻,从而解决了现有技术中AuGeNi合金的退火温度较高而导致的对器件可靠性存在不利影响。另外,VCSEL芯片的制备中,在N电极的各层金属沉积完成后,芯片流程会进行一次PECVD SiN沉积工艺,PECVD工艺温度设定250~300℃,工艺时间在10~15min,该PECVD SiN沉积工艺中即可同步实现N电极的退火效果,所以流程中不需要额外的增加退火工序,进一步简化了VCSEL芯片的制备流程,节省了能源和成本。

本发明实施例所述的制备N电极的方法,该方法简单易实施,且该方法通过较低的退火温度就能实现与GaAs衬底具有较低的接触电阻,从而进一步提高了器件的可靠性。同时,分别蒸镀形成Pd金属单质层和Ge金属单质层,在蒸镀工艺中便于实现各金属比例的控制,因此不存在AuGeNi合金成分出现偏差的问题。另外,本发明通过形成Pd层和Ge层作为N电极,退火后具有更好的金属表面外观,便于后续PECVD SiN沉积工艺。

在本发明的第三个方面,本发明提出了一种VCSEL芯片。根据本发明的实施例,该VCSEL芯片包括以上实施例所述的N电极或采用以上实施例所述方法制得的N电极。由此,进一步提高了VCSEL芯片的可靠性,进一步简化了VCSEL芯片的制备流程,节省了能源和成本。

具体地,参考附图2,VCSEL芯片包括GaAs衬底100,其中,在所述GaAs衬底100上按照层状结构从下至上依次为NDBR层200、MQW层300、氧化层400、PDBR层500和P接触层600。

下面以透镜结构的VCSEL芯片为例,结合附图2对VCSEL芯片的制备方法作具体说明,其情况如下:

在所述GaAs衬底100上按照层状结构从下至上依次形成NDBR层200、MQW层300、氧化层400、PDBR层500和P接触层600;

在所述P接触层600上,蒸镀后利用光刻胶剥离技术制备P电极700;

利用ICP刻蚀技术将外延层刻至氧化层,利用氧化炉进行湿法氧化,完成氧化层400的制备;

利用ICP刻蚀技术将外延层刻至导电衬底,蒸镀后再利用光刻胶剥离技术制备N电极800;

利用PECVD技术在VCSEL芯片的表面进行SiN钝化层900的制备,由此完成VCSEL芯片的制备。

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。

- 一种NTC芯片电极浆料及使用该浆料的NTC芯片的制备方法

- 一种集中电流注入的VCSEL芯片及其制备方法

- 一种铅笔绘制双极电极纸芯片甲胎蛋白免疫传感器的制备方法

- 一种具有反射电极的垂直结构LED芯片及其制备方法

- 一种垂直结构LED芯片、反射电极及其制备方法

- 一种VCSEL芯片金属薄膜电极的制备方法

- 一种VCSEL芯片金属薄膜电极的制备方法