具有近存储器地址生成的存储器访问命令

文献发布时间:2023-06-19 18:32:25

技术领域

具有近存储器地址生成的存储器访问命令的公开实施方案一般涉及易失性和非易失性计算机存储器,并且更具体地,涉及用于访问计算机存储器中所存储的数据的计算机实现逻辑。

背景技术

计算机存储器是几乎每个计算机的基础部件,包括个人计算机、平板计算机、智能电话、服务器计算机和其他计算设备诸如打印机和因特网连接设备。计算机存储器通常用于计算机中以存储数据以及对该数据进行操作的处理器可执行指令(机器代码)。

虽然术语“存储器”通常用于指易失性计算机存储器,诸如呈现具有金属氧化物半导体存储单元的集成电路芯片形式的动态随机存取存储器(或仅简称“DRAM”),但是计算机存储器也可以是非易失性的。易失性和非易失性计算机技术的非详尽列表包括DRAM、静态随机存取存储器(或仅简称“SRAM”)、非易失性双列直插式存储器模块(或仅简称“NVDIMM”)、快闪存储器、嵌入式DRAM、便笺式存储器等。

计算机的计算机存储器通常经由计算机的一组导线或导体而连接到计算机的硬件“主机”。硬件主机可涵盖存储器控制器和中央处理单元(或仅简称“CPU”)、图形处理单元(或仅简称GPU)或其他硬件数据处理器。计算机存储器与主机之间的连接通常涵盖:针对命令/地址信息的接口(有时称为“命令/地址总线”)以及针对数据信息的接口(有时称为“数据总线”)。

近来,处理器(例如CPU和GPU)的计算能力和速度增加已经快于连接计算机存储器与主机的数据总线的带宽。结果,当处理器悠闲地等待数据经由数据总线往返于计算机存储器进行传送时,数据总线已经成为计算吞吐量的一个瓶颈。

存储器内处理器(或仅简称“PIM”)解决方案提供了靠近计算机存储器(例如,在相同裸片上)的数据处理能力。利用PIM解决方案,由于数据处理能力靠近计算机存储器,因此可以对从计算机存储器所访问的数据执行计算,而不必通过数据总线将所有原始数据传送至主机。例如,一种可能的PIM解决方案可涉及:将简单的向量计算元件添加到计算机存储器的每个内部存储器模块中,诸如添加到每个DRAM库或子阵列。然后,利用这些附加元件,主机可以在所有内部存储器模块处触发计算,而无需通过数据总线在DRAM接口上传送数据。

通过计算机存储器与主机之间的数据传输,PIM解决方案可节省数据总线的带宽消耗,并且提高计算工作负载的吞吐量,特别是针对日益增长的数据受限计算工作负载类别,诸如深度人工神经网络机器学习工作负载、大规模图形分析工作负载、机器学习工作负载中的稀疏计算以及其他类型的计算密集型工作负载,在缺乏存储器本地PIM单元的情况下,随着计算机存储器与主机之间的数据传输,这些计算密集型工作负载可能达到数据总线的带宽限值。

仅作为一个示例,机器学习中的常见操作是稀疏嵌入查找。此操作可以支配一些工作负载的执行时间。从包含计算机存储器中所存储的数百万个嵌入条目的大型嵌入表中,此类操作可以稀疏地读取包含数百个元素的大型嵌入,并将它们累积在一起。由于数据重用受到限制,此类操作对数据总线带宽非常敏感。

在不使用PIM解决方案的情况下,稀疏嵌入查找操作可能需要主机发出一组存储器加载请求,多个存储器模块(例如,DRAM库)中的每个存储器模块对应一个存储器加载请求。每个存储器加载请求使数据通过数据总线从相应的存储器模块传送至主机。由于存储器模块可共享命令/地址总线和数据总线(例如,相同存储器通道上的DRAM库),因此可能需要将对不同存储器模块的访问串行化,从而导致命令/地址和数据总线都得到充分利用。相反,如果使用PIM解决方案,则可以在存储器本地PIM单元中计算累积量,而无需在数据总线上传送一些数据。

然而,由于PIM解决方案可以减轻某些工作负载的一些或全部数据总线瓶颈,所以命令/地址总线处的瓶颈可能变成新的瓶颈。例如,命令/地址总线处的瓶颈可能随着具有稀疏或不规则存储器访问模式(诸如,机器学习工作负载和其他工作负载中发现的存储器访问模式)的数据受限计算工作负载而出现。由于命令/地址总线由存储器模块共享,所以每个存储器加载命令仍需要通过命令/地址总线来发送。

对命令/地址总线瓶颈的一种可能的解决方案是:通过增加存储器通道的数量或通过增加每个存储器通道的命令/地址线的数量,来增加命令/地址总线的带宽。然而,这增加了单位制造成本并增加了功耗。此外,对于具有常规存储器访问模式的工作负载,额外的命令/地址总线带宽可能并未得到利用。

所公开的实施方案解决了此问题和其他问题。

本节所述的方法是可以实行的方法,但不一定是先前已经设想或实行过的方法。因此,除非另有说明,否则不应假设:本节所述的任何方法仅由于其包含在本节中而假定它们是现有技术,或者是公知的、例行的或常规的。

附图说明

图1是用于具有近存储器地址生成的存储器访问命令的示例性系统的示意图。

图2示出了一示例性系列的存储器访问命令,当存储器模块的存储器位置中所存储的数据在存储器模块上进行了地址对齐后,这些命令可以由存储器控制器经由命令/地址总线来发送。

图3示出了一示例性系列的存储器访问命令,当存储器模块的存储器位置中所存储的数据在存储器模块上尚未进行地址对齐时,这些命令可以由存储器控制器经由命令/地址总线来发送。

图4示出了没有近存储器地址生成能力的示例性存储器模块。

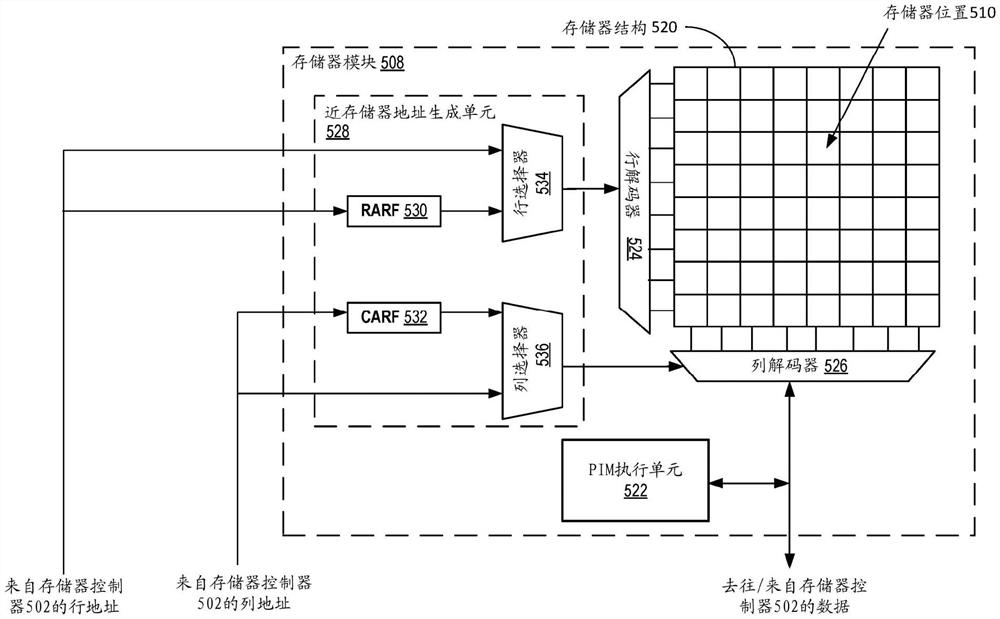

图5示出了包括近存储器地址生成单元的示例性存储器模块,近存储器地址生成单元用于为指定不完整地址信息的存储器访问命令生成近存储器地址。

图6描绘了包括近存储器地址生成单元的示例性存储器模块,近存储器地址生成单元具有地址计算单元,用于为指定不完整地址信息的存储器访问命令生成近存储器地址。

图7示出了用于访问多个存储器模块上所存储的数据的命令系列。

并非各附图中所绘的所有部件都是必需的,并且实施方案可包括附图中未示出的附加部件。在不脱离本公开范围的情况下,可以对部件的布置方式和类型作出改变。在本公开的范围内,可使用附加部件、不同部件或更少部件。

具体实施方式

在以下描述中,出于解释的目的,阐述了许多具体细节以便提供对具有近存储器地址生成的存储器访问命令的实施方案的透彻理解。然而,显而易见的是,可以在没有这些具体细节的情况下实践这些实施方案。在其他情况下,以框图形式示出了公知的结构和设备,以避免不必要地模糊这些实施方案。

本发明公开了用于具有近存储器地址生成的存储器访问命令的系统和方法。此类系统和方法可促进计算机存储器访问而用于支持(例如,有效地支持)计算工作负载,包括但不限于深度机器学习工作负载(例如,使用深度人工神经网络)、大规模图形分析、以及/或者具有稀疏或不规则存储器访问的其他计算工作负载。本主题技术可用于各种系统中,包括但不限于北桥芯片组、现场可编程阵列(或仅简称“FPGA”)设备、微处理器设备、CPU设备、GPU设备、存储器集成电路和/或其他系统,诸如机器学习和/或人工智能加速器设备。

经由存储器控制器与两个或更多个计算机存储器模块之间的连接,配置有命令逻辑的存储器控制器可发送具有不完整地址信息的存储器访问命令。不完整地址信息可以没有地址信息(无地址)。相反,不完整地址信息可具有部分地址信息。存储器控制器经由连接而发送存储器访问命令,用于访问存储器模块的两个或更多个存储器位置处存储的数据。存储器位置对应于两个或更多个近存储器生成地址。

与存储器位置对应的近存储器生成地址可以是不同的,这反映了数据在存储器模块上尚未进行地址对齐。然而,由于近存储器地址生成,存储器控制器可发送具有不完整地址信息的存储器访问命令而用于访问不同地址处存储的数据,这与必须在总线上发送指定完整地址信息的多个存储器访问命令而用于访问不同地址处的数据相反,从而节省可用总线带宽的用量、降低功耗并增加计算吞吐量。

存储器控制器的命令逻辑被配置为经由连接将指定地址的程序地址命令发送至存储器模块。这些预编程地址可靠近存储器来存储,对于不同的存储器模块可以不同,并且可以在具有不完整地址信息的多个存储器访问命令之间进行平衡,从而避免必须通过与每个存储器访问命令的连接来发送完整的地址信息。

具有不完整地址信息的存储器访问命令可指定存储器模块的PIM单元待执行的操作(例如,乘法或加法)。由于近存储器地址生成,发送单个具有不完整地址信息的存储器访问命令可能使PIM单元对不同存储器模块中存储的数据执行操作,即使在数据在存储器模块上尚未进行地址对齐的情况下。

存储器模块中的一个存储器模块具有存储器结构和近存储器地址生成单元。存储器结构涵盖可寻址的存储器位置。近存储器地址生成单元被配置为靠近存储器生成与该存储器结构的存储器位置对应的地址。近存储器地址生成单元被配置为基于在存储器模块处经由该连接而接收到具有不完整地址信息的存储器访问命令,来生成该地址,该不完整地址信息由存储器控制器经由该连接所发送,用于访问与近存储器生成地址对应的存储器模块的存储器位置处存储的数据。

近存储器地址生成单元包括寄存器堆。寄存器堆被配置为存储近存储器地址生成单元将生成的地址。基于在存储器模块处,经由该连接而接收到指定寄存器堆中待存储地址的程序地址命令,将该地址存储于寄存器堆中。

近存储器地址生成单元包括地址计算单元,该地址计算单元被配置为计算近存储器地址生成单元将生成的地址。地址计算单元基于对地址应用预配置步幅来计算待生成的地址。地址计算单元基于从存储器模块的PIM单元所获得的值或基于从存储器结构的存储器位置所获得的值来计算待生成的地址。

存储器控制器包括命令逻辑,该命令逻辑被配置为经由连接而发送具有不完整地址信息的第一存储器访问命令,用于访问一组两个或更多个存储器模块的一组两行或更多行中存储的数据,该一组两行或更多行对应于一组两个或更多个近存储器生成行地址。命令逻辑也被配置为经由连接而发送具有不完整地址信息的第二存储器访问命令,用于访问一组两个或更多个存储器模块中的一组两列或更多列中存储的数据,该一组两列或更多列对应于一组两个或更多个近存储器生成列地址。

存储器模块包括具有多行和多列的存储器结构。存储器模块也包括近存储器地址生成单元,其被配置为基于该模块经由连接而接收到用于访问行中存储的数据的第一存储器访问命令,来生成与多行中的行对应的行地址。近存储器地址生成单元还被配置为基于该模块经由连接而接收到用于访问该行的该列中存储的数据的第二存储器访问命令,来生成与多列中的一列对应的列地址。

当借由计算机存储器的不规则或稀疏数据访问来处理计算工作负载时,各实施方案支持(例如,有效地支持)CPU、GPU和PIM单元。此类工作负载包括在商业、政府、教育和研究领域中日益普及的深度学习推荐模型和大规模图形分析。各实施方案允许此类工作负载更快地访问存储器并功耗更低。

现在将参照附图更详细地描述这些实施方案和其他实施方案。

图1是用于具有近存储器地址生成的存储器访问命令的示例性系统的示意图。该系统包括存储器控制器102,其电连接到由两个或更多个存储器模块108共享的命令/地址总线106,并且存储器模块108也电连接到该命令/地址总线。电连接可以是直接或间接的,其中,间接电连接可包括电通路中的附加结构。

该系统可包括图1未示出的其他部件。例如,该系统可包括图1未示出的其他总线、芯片和电路。

在图1的示例中,描绘了三个存储器模块。然而,该系统可具有少至两个存储器模块或多于两个存储器模块,包括多于三个存储器模块。除了命令逻辑104之外,存储器控制器102还可包括图1未描绘的其他逻辑和结构,诸如请求缓存、响应缓存、存储器映射逻辑和仲裁逻辑。除了通过命令/地址总线106电连接到存储器模块108之外,存储器控制器102还可通过图1未描绘的其他总线诸如数据总线而电连接到存储器模块108。

存储器控制器102可包括用于管理来往于存储器模块108的数据流的硬连线数字电路和/或编程数字电路。存储器控制器102可以是单独的芯片或集成到另一芯片中,诸如置于相同裸片上或作为微处理器诸如CPU或GPU的集成部件。除了命令逻辑104之外,存储器控制器102也可涵盖用于对存储器模块108进行数据读取和写入的逻辑。在存储器模块108为易失性存储器设备的情况下,存储器控制器102可包括用于周期性地刷新存储器模块108的存储器单元中的电荷的逻辑,诸如,其中存储器模块108基于例如半导体DRAM来实现。

通过共享命令/地址总线106,可经由命令/地址总线106来发送存储器控制器102针对一个、两个或更多个或所有存储器模块108所发送的命令。当经由命令/地址总线106,将命令从存储器控制器102发送至存储器模块108中的一个或多个存储器模块时,可以仅沿着命令/地址总线106,或沿着存储器控制器102与一个或多个存储器模块之间的电通路中的一个或多个附加电连接,将命令从存储器控制器102发送至一个或多个存储器模块。

命令/地址总线106可涵盖一组一个或多个电导线或电导体,用于发送表示命令的电信号,包括程序地址命令以及具有本文所公开的不完整地址信息的存储器访问命令。可经由命令/地址总线106,将电信号从存储器控制器102发送至存储器模块108。

存储器102控制器与存储器模块108之间的连接可涵盖用于发送和接收命令/地址信息诸如存储器访问命令的接口。在图1中,此连接标记为命令/地址总线106。存储器控制器102与存储器模块108之间的相同连接或单独连接可涵盖用于发送和接收数据诸如从存储器位置所访问的数据的接口。本文有时将此连接称为“数据总线”。尽管使用了术语“总线”,但是一个或多个连接可涵盖一组导线或导体、或者处于存储器控制器102与存储器模块108之间的其他形式的有线和/或无线电耦接或电连接。此外,如所指示,命令/地址总线106和数据总线可共享存储器控制器102与存储器模块108之间的相同电连接或使用单独的电连接。

命令/地址总线106可以由子总线组成。例如,命令/地址总线106可以由可能的其他子总线中的行地址总线和列地址总线组成。

存储器模块108提供了用于存储数据的可寻址存储器位置。在一些情况下,本文将存储器位置处所存储或访问的数据称为“值”或“数据值”。此类值可以由一个或多个位来表示。在一些情况下,存储器位置是字节可寻址的且存储8位数据值。在一些情况下,存储器位置是字可寻址的且存储多字节数据值(例如,16位、32位、64位或128位数据值)。

当通过存储器控制器102所发送的命令而从存储器模块(例如,108-0)的存储器位置(例如,110)中访问数据值时,可经由存储器模块108与主机之间的数据总线,将数据值从存储器模块发送回主机。另外或可选地,可以将数据值发送至靠近存储器模块的PIM单元以供PIM单元进行计算或累积(例如,乘法、加法等)。

如本文所用,术语“近存储器”涵盖在存储器中,诸如,在与存储器模块(例如,108-0)相同的裸片、芯片或电路中。然而,更广泛地,近存储器涵盖实际上比主机或存储器控制器102更靠近存储器模块的结构,该主机或存储器控制器处于相对于存储器模块的命令总线106的另一端。

存储器模块108-0、108-1、108-2均为DRAM库。然而,每个存储器模块108可对应于存储器层级中另一类型的部件,诸如子阵列、等级或通道。此外,存储器模块不限于易失性存储器设备或DRAM设备,并且可包括非易失性存储器设备或具有可寻址存储器位置的其他类型的存储器设备。

近存储器地址生成单元用于生成近存储器地址。例如,单独的近存储器地址生成单元可位于每个存储器模块108-0、108-1和108-2内。例如,在存储器模块108是处于基本裸片顶部上的多个存储器层堆栈的部件的情况下,近存储器地址生成单元可位于基本裸片中,或者近存储器地址生成单元可位于三维堆栈存储器的存储器各层中或更传统的DRAM的存储器层中。

除了三维堆栈DRAM和传统DRAM之外,近存储器地址生成单元也可位于其他形式的存储器中,诸如非易失性存储器、快闪存储器和嵌入式DRAM。虽然下文所述的实施方案是处于DRAM存储器结构的上下文中,但是近存储器地址生成单元及其功能可实现于其他存储器上下文中,诸如其他形式的新兴存储器技术或后期开发的存储器技术的上下文中,包括非易失性存储器模块诸如NVDIMM、以及其他形式的存储器诸如便笺式存储器等。

与存储器模块108相关联的近存储器地址生成单元使存储器控制器102能够发送具有不完整地址信息(诸如无地址信息或仅部分地址信息)的存储器访问命令。尽管如此,近存储器地址生成单元能够生成近存储器地址,以提供完整地址信息,该完整地址信息或者是完整的,或者是与存储器访问命令中指定的部分地址信息相结合的。如此,计算工作负载诸如机器学习和大规模图形分析以及其他产生不规则存储器访问的计算工作负载得到支持,同时命令/地址总线106带宽消耗降低,功耗更低。

例如,由于近存储器地址生成单元与存储器模块108相关联,可经由命令/地址总线106,将具有不完整地址信息的存储器访问命令从存储器控制器102发送至存储器模块108中的两个或更多个存储器模块,用于即使存储器位置尚未地址对齐,也访问存储器模块108中的不同存储器模块中的存储器位置。例如,存储器模块108-0的存储器位置110在图1中标明为具有地址“0:2”。此注释仅用于说明的目的。冒号‘:’前的编号对存储器模块108中连接到命令106的存储器模块进行寻址(例如,标识)(在此示例中为“0”)。“冒号后的编号”对所寻址的存储器模块内的存储器位置进行寻址(在此示例中为“2”)。在一些情形下,寻址由地址所寻址的存储器模块内的具体存储器位置的这部分地址在本文中称为“模块相对”地址。在此示例中,冒号后的“2”将是地址“0:2”的模块相对地址。

再次,应强调的是,在本公开中,图1的地址注释仅用于说明的目的。实际地址可以是具有多个分量的多位地址,诸如对存储器模块进行寻址的一定数量的位、对所寻址的存储器模块的行地址进行寻址的一定数量的位、以及对所寻址的存储器模块的列地址进行寻址的一定数量的位、以及位所表示的其他信息。其他多位地址表示也是可能的,并且无需具体的地址表示。

一些计算工作负载表现出规则的存储器访问模式,其中存储器访问在存储器模块108上进行了地址对齐。例如,存储器模块108-0的地址“0:2”处的存储器位置110与存储器模块108-1的地址“1:2”处的存储器位置进行地址对齐,存储器模块108-1的地址“1:2”处的存储器位置与存储器模块108-2的地址“2:2”处的存储器位置进行地址对齐,因为所有三个存储器位置都具有相同的模块相对地址(在此示例中为“2”)。

在待从两个或更多个存储器模块访问的数据进行了地址对齐的情形下,可发送具有完整地址信息的单个存储器访问命令,以访问多个地址对齐的存储器位置。例如,存储器控制器102可发送(例如,广播)将“2”指定为模块相对地址的单个存储器访问命令,并且访问存储器位置“0:2”、“1:2”和“2:2”处存储的数据。例如,单个存储器访问命令可以由存储器控制器102在命令/地址总线106上广播到指定“2”作为模块相对地址的所有存储器模块108,该模块相对地址明确地标识了待在每个存储器模块108处访问的存储器位置。

然而,如果待于两个或更多个存储器模块108中访问的数据尚未地址对齐,则可能需要由存储器控制器102来发送多个存储器访问命令。例如,如果待访问数据存储在存储器位置“0:2”和“1:3”,则指定不同地址的两个存储器访问命令可能需要由存储器控制器102经由命令/地址总线106来发送。

然而,由于近存储器地址生成单元与存储器模块108相关联,可以由存储器控制器102,经由命令/地址总线106来发送具有不完整地址信息的单个存储器访问命令,用于访问存储器模块108中的两个或更多个存储器模块上的不同未对齐存储器位置处存储的数据。例如,该命令可访问存储器位置“0:2”、“1:3”和“2:0”处存储的数据,其中一些或全部模块相对地址可以由与存储器模块108相关联的近存储器地址生成单元来生成。例如,基于存储器模块108-0经由命令总线106,从存储器控制器102接收命令,与存储器模块108-0相关联的第一近存储器地址生成单元可生成模块相对地址“2”。基于存储器模块108-1经由命令总线106,从存储器控制器102接收命令,与存储器模块108-1相关联的第二近存储器地址生成单元可生成模块相对地址“3”。基于存储器模块108-2经由命令总线106,从存储器控制器102接收命令,与存储器模块108-2相关联的第三近存储器地址生成单元可生成模块相对地址“0”。

如本文所用,具有“不完整”地址信息的存储器访问命令涵盖由存储器控制器102经由命令/地址总线106发送至两个或更多个存储器模块108的命令,其中靠近存储器生成一些或全部模块相对地址。如上所述,模块相对地址可涵盖完整地址的一部分,该完整地址标识了待通过命令所访问的完整地址所寻址的存储器模块的存储器位置。相反,具有“完整”地址信息的存储器访问命令可涵盖由存储器控制器102经由命令/地址总线106发送至两个或更多个存储器模块108的命令,其中整个模块相对地址可由该命令来指定,并且模块相对地址部分的任何部分均不可靠近存储器生成。

具有不完整地址信息的存储器访问命令可能不指定模块相对地址的任何部分。在此情形下,可靠近存储器生成整个模块相对地址。例如,具有不完整地址信息的存储器访问命令可不指定行地址也不指定列地址。在此情形下,可以由近存储器地址生成单元,靠近存储器生成行地址和列地址。注意,由于近存储器地址生成单元,对于正被访问的不同存储器模块,诸如数据在存储器模块上尚未进行地址对齐时的情形,可靠近存储器生成不同的行地址和列地址。并且在数据于待访问存储器模块之间尚未进行地址对齐的情形下,由于近存储器地址生成单元,存储器控制器102仅需要经由命令/地址总线106来发送单个存储器访问命令,并且无需针对每个不同的模块相对地址而发送单独的存储器访问命令,由此节省了命令/地址总线106的带宽和功耗。

具有不完整地址信息的存储器访问命令可以仅指定部分地址信息,诸如仅一些但非所有的模块相对地址。例如,具有不完整地址信息的存储器访问命令仅可指定正被访问的存储器模块所共用的行地址或列地址,但不可既指定行地址也指定列地址,或另外指定完整地址,或指定所有模块相对地址。在此情形下,模块相对地址的丢失部分可靠近存储器生成。

例如,具有不完整地址信息的存储器访问命令可指定针对正被访问的存储器模块的行地址命令,但不可指定列地址。在此情形下,列地址可以由近存储器地址生成单元靠近存储器生成。注意,由于近存储器地址生成单元,对于正被访问的不同存储器模块,诸如数据在存储器模块上尚未进行地址对齐时的情形,可靠近存储器生成不同的列地址。并且在数据于待访问存储器模块之间尚未进行地址对齐的情形下,由于近存储器地址生成单元,存储器控制器102仅需要经由命令/地址总线106来发送单个存储器访问命令,并且无需针对每个不同的列地址而发送单独的存储器访问命令,由此节省了命令/地址总线106的带宽和功耗。

作为另一示例,具有不完整地址信息的存储器访问命令可指定针对正被访问的存储器模块的列地址命令,但不可指定行地址。在此情形下,行地址可以由近存储器地址生成单元靠近存储器生成。注意,由于近存储器地址生成单元,对于正被访问的不同存储器模块,诸如数据在存储器模块上尚未进行地址对齐时的情形,可靠近存储器生成不同的行地址。并且在数据于待访问存储器模块之间尚未进行地址对齐的情形下,由于近存储器地址生成单元,存储器控制器102仅需要经由命令/地址总线106来发送单个存储器访问命令,并且无需针对每个不同的行地址而发送单独的存储器访问命令,由此节省了命令/地址总线106的带宽和功耗。

针对正被访问的两个或更多个存储器模块108中的一些而非全部存储器模块,具有不完整地址信息的存储器访问命令指定完整地址。在此情形下,针对命令未提供完整地址的存储器模块,近存储器地址生成单元可靠近存储器生成地址。

具有不完整地址信息的存储器访问命令指定伪地址,诸如与现有存储器接口规范或标准兼容的伪地址。在此情形下,针对命令正在访问的所有存储器模块,近存储器地址生成单元可靠近存储器生成地址。此类命令可视为在功能上等效于不指定任何地址信息的存储器访问命令。

具有近存储器地址生成的不完整地址信息的存储器访问命令可以克服命令/地址总线106针对不规则和稀疏计算工作负载的带宽限制,包括机器学习和大规模图形分析工作负载,这些负载表明了存储器访问的不规则性,诸如访问存储器模块108中且尚未进行地址对齐的存储器位置处的数据。

具有近存储器地址生成的不完整地址信息的存储器访问命令可支持(例如,有效地支持)PIM解决方案。例如,在将要把相同PIM操作(例如,乘法或加法)应用于两个或更多个存储器模块108上所存储的数据的情况下,指定PIM操作的单个存储器访问命令可以由存储器控制器102,经由命令/地址总线106来发送,以访问数据并在两个或更多个存储器模块的每个存储器模块处完成操作,即使在存储了数据的一些或全部存储器位置于两个或更多个存储器模块之间尚未进行地址对齐的情况下。与存储器控制器102必须经由命令/地址总线106来发送多个存储器访问命令以访问数据并在两个或更多个存储器模块中的每个存储器模块处完成PIM操作相反,单个存储器访问命令可以由存储器控制器102,经由命令/地址总线106来发送。如此,通过具有并行应用于两个或更多个存储器模块108的PIM操作的多次存储器访问,可减轻针对某些计算工作负载的命令/地址总线106的带宽瓶颈。此外,在命令中没有指定地址信息或仅指定部分地址信息的情况下,与存储器控制器102经由命令/地址总线106来发送指定完整地址信息的存储器地址命令时相比,存储器控制器102经由命令/地址总线106来发送命令时可节省功耗,这是因为经由命令/地址总线106所发送的位更少。

近存储器PIM解决方案可支持(例如,有效地支持)不规则和稀疏的存储器访问,诸如某些计算工作负载中发现的存储器访问,包括但不限于基于推荐的人工神经网络计算、大规模图形分析、机器学习中的稀疏计算等。PIM解决方案将计算逻辑靠近存储器放置,以处理轻量级、数据密集型计算,从而降低主机的数据总线带宽需求并且释放主机以集中于计算密集型计算诸如矩阵数学。

然而,如所提及,PIM解决方案可能受限于存储器模块所共享的共享命令(地址)总线,诸如存储器模块108所共享的共享命令/地址总线106。例如,共享命令/地址总线106可以是但不限于:DRAM存储器(例如,同步动态随机存取存储器(SDRAM)、图形双数据速率同步动态随机存取存储器(GDDR)、高带宽存储器(HBM)等)通道内的各库之间的共享命令/地址总线。在此示例中,这些库由图1的存储器模块108来表示。

许多因素会限制PIM解决方案的有效性。其一,共享命令/地址总线106的带宽可被设计用于非PIM解决方案具体实施和更规则的计算工作负载,其主要涵盖地址对齐的存储器访问。因此,尽管PIM解决方案可减轻数据总线上的瓶颈,但其可能将瓶颈引入共享命令/地址总线106上,尤其是对于涵盖了在存储器模块108上尚未进行地址对齐的更多存储器访问的不规则且稀疏的计算工作负载。

可能限制PIM解决方案有效性的另一因素可以是一些计算工作负载的稀疏和不规则的存储器访问。对于其中数据在存储器模块108上进行了地址对齐的常规工作负载,单个广播PIM命令可以由存储器控制器102,经由命令/地址总线106来发送,以访问存储器模块108上的多个地址对齐的存储器位置。图2示出了一示例性系列的存储器访问命令,当存储器位置中所存储的数据在存储器模块108上进行了地址对齐后,这些命令可以由存储器控制器102,经由命令/地址总线106来发送。

在图2的示例中,存储器控制器102发送三个存储器访问命令。三个存储器访问命令均是用于由存储器模块108中的每个存储器模块来接收的广播命令。三个命令均指示每个存储器模块对该命令所指定的模块相对地址处所存储的数据执行操作“OP-1”(例如,加载、乘法或加法)。由于数据在存储器模块108上进行了地址对齐,所以可使用广播命令。

例如,假设操作“OP-1”是PIM操作诸如乘法或加法。第一命令212指示每个存储器模块处的PIM单元使用操作数“X-1”对存储器模块的模块相对地址“0”处的存储器位置处存储的数据执行操作“OP-1”。例如,假设PIM操作“OP-1”为乘法并且操作数“X-1”是5,则第一命令212可以使存储器模块108-0的存储器位置“0:0”处存储的数据乘以5,使存储器模块108-1的存储器位置“1:0”处存储的数据乘以5,并且使存储器模块108-2的存储器位置“2:0”处存储的数据乘以5。注意,由于待相乘的数据存储在每个存储器模块108处的相同模块相对地址(“0”)处,因此单个广播命令可以由存储器控制器102,经由命令/地址总线106来发送,以并行化存储器模块108上的PIM操作。类似地,对于图2的第二广播命令,除了模块相对地址为“1”且不同的操作数为“X-2”之外,在第一广播命令之后发送,并且对于第三广播命令,除了模块相对地址为“2”且不同的操作数为“X-3”之外,在第二广播命令之后发送。因此,在此示例中,由于待乘以不同操作数“X-1”、“X-2”和“X-3”的数据在存储器模块108上进行地址对齐,所以仅三个广播命令需要由存储器控制器102,经由命令/地址总线106来发送。存储器地址214表示使用前述注释的广播存储器地址,其中星号‘*’在冒号‘:’之前表示共享了命令/地址总线106的所有存储器模块108,并且冒号之后的“1”表示模块相对地址。

虽然当数据在存储器模块108上进行了地址对齐后,使用广播存储器访问命令来限制共享命令/地址总线106的使用是可能的,但是当数据尚未进行地址对齐时,此类使用可能是不可能的。图3示出了一示例性系列的存储器访问命令,当存储器位置中所存储的数据在存储器模块108上尚未进行地址对齐时,这些命令可以由存储器控制器102,经由命令/地址总线106来发送。图3的一系列存储器访问命令完成了与图2的一系列存储器访问命令类似的计算。然而,由于在图3的示例中,数据尚未进行地址对齐,因此九个存储器访问命令可以由存储器控制器102,经由共享命令/地址总线106来发送,这与图2的示例中仅发送三个相反。具体来说,在图3的示例中,可针对每个不同存储器位置发送单独的存储器访问命令。具体来说,图3的命令系列的前三个命令完成了与图2的第一广播命令类似的计算,图3的命令系列的后三个命令完成了与图2的第二广播命令类似的计算,并且图3的命令系列的最后三个命令完成了与图2的第三广播命令类似的计算,但是具有不同的且非地址对齐的存储器访问。然而,由于在图3的示例中,将在存储器模块108的存储器位置处进行操作的数据尚未地址对齐,所以更多的存储器访问命令可以由存储器控制器102,经由命令/地址总线106来发送,以完成与图2示例中所发送的且对地址对齐数据进行操作的更少命令相同的计算。

存储器访问命令316表示图3的一系列命令中的其他存储器访问命令。与该系列中的其他存储器访问命令类似,且与图3的广播存储器访问命令212相反,存储器访问命令316对一个存储器模块“0”中的具体存储器位置“0”进行寻址。因此,存储器地址318表示在图3的系列中的存储器访问命令所指定的其他存储器地址。具体来说,与该系列中的其他命令所指定的其他存储器地址类似,且与广播存储器地址214相反,存储器地址318对一个存储器模块“1”的具体存储器位置“2”进行寻址。

因此,虽然针对具有大量地址对齐式存储器访问的常规计算工作负载,PIM解决方案可能达不到命令/地址总线106的带宽限制,但是对于具有许多并非地址对齐式存储器访问的稀疏或不规则计算工作负载,可以达到此类限制,因为存储器控制器106可经由命令/地址总线106发送更多数量的存储器访问命令来完成相同的计算。

PIM解决方案受近存储器地址生成的支持,其允许靠近存储器生成地址,使得即使在数据访问尚未地址对齐的情况下,也可使用广播或多播存储器访问命令来实现跨多个存储器模块108的并行存储器访问。

图4是没有近存储器地址生成能力的示例性存储器模块的示意图。存储器模块408可包括提供了多个存储器位置的存储器结构420,其中存储器位置410是一个示例。存储器模块408可经由命令/地址总线而电连接到存储器控制器402。例如,存储器模块408可以是经由命令/地址总线106而连接到存储器控制器102的图1中的存储器模块108之一。因此,存储器控制器402可以是例如图1中的存储器控制器102。

在此示例中,存储器结构420具有栅格或表格配置,其中存储器位置按行和列来布置。然而,存储器结构420可实现为存储器位置阵列。可选地,存储器结构420可以是三维结构,诸如彼此堆栈起来的网格式或表格式存储器结构。存储器结构420不限于任何具体布置的存储器位置,并且实际上可使用具有可寻址存储器位置的任何存储器结构。

存储器模块408也包括PIM执行单元422,用于对来自存储器结构420的存储器单元中的数据访问执行近存储器计算。例如,PIM执行单元422可涵盖一个或多个乘加单元、用于矩阵向量乘法操作的一个或多个缩减器、或用于对从存储器结构420中访问的数据进行操作的其他子单元。

在操作中,存储器控制器402可经由命令/地址总线106来发送存储器访问命令以供存储器模块处接收。存储器访问命令可指定地址。指定地址可标识存储器模块408的存储器结构420的存储器位置(例如,410)。例如,指定地址可具有输入行解码器424中的行地址分量以及输入列地址解码器426中的列地址分量。行地址与列地址的组合指定待访问的存储器位置(例如,410)。在加载(或读取)操作时,将存储器位置处的数据发送至PIM执行单元422以及/或者发送回主机(例如,存储器控制器402)以基于其进行计算。存储器结构420的每个存储器位置可存储一个或多个字节的数据。

存储器模块408可包括为了简单起见而未在图4中示出的其他部件,诸如行缓存和输入/输出驱动器。

图5是包括近存储器地址生成单元528的示例性存储器模块508的示意图,近存储器地址生成单元用于为指定不完整地址信息的存储器访问命令生成近存储器地址。与图4的存储器模块408类似,存储器模块508可包括提供了多个存储器位置的存储器结构520,其中存储器位置510是一个示例。存储器模块508可经由命令/地址总线而电连接到存储器控制器502。例如,存储器模块508可以是经由命令/地址总线106而连接到存储器控制器102的图1中的存储器模块108之一。因此,存储器控制器502可以是例如图1中的存储器控制器102。存储器模块508可包括PIM执行单元522、行解码器524和列解码器526,也类似于图4中的存储器模块408。

然而,与图4中的存储器模块408不同,存储器模块508可包括近存储器地址生成单元528,用于为指定不完整地址信息的存储器访问命令生成近存储器地址。在近存储器地址生成单元528之内,是行地址寄存器堆(或仅简称“RARF”)530和列地址寄存器堆(或仅简称“CARF”)532。RARF 530可存储一个或多个行地址,用于当被选择由行选择器534来生成后,输入行解码器524中。类似地,CARF 532可存储一个或多个列地址,用于当被选择由列选择器536生成时,输入列解码器526中。可选地,可能有益的是,将近存储器地址生成单元并入与存储器模块508分离(但实际上仍邻近)的集成电路中,因为这将实现常规存储器模块的使用,从而产生潜在有益的成本。

可针对存储器控制器502经由命令/地址总线所发送的存储器访问命令来控制行选择器534和列选择器536。具体来说,行选择器534和列选择器536允许存储器控制器502发送具有不完整地址信息的存储器访问命令,针对该不完整地址信息,分别由RARF 530和/或CARF 532来生成行地址和/或列地址。行选择器534和列选择器536也允许存储器控制器502发送存储器访问命令,针对该命令,地址信息不由近存储器地址生成单元582靠近存储器生成。

例如,存储器控制器502可发送指定地址的存储器访问命令,该地址既包括行地址也包括列地址。在此情形下,行选择器534可被配置为接受存储器访问命令中所指定的行地址作为输入,并且不接受由RARF 530针对该命令所生成的行地址作为输入。类似地,列解码器526可被配置为接受存储器访问命令中所指定的列地址作为输入,并且不接受由CARF532针对该命令所生成的列地址作为输入。可选地,在此示例的上下文中,可能正如DRAM、相变存储器、电阻性存储器或其他将存储器位置组织成行和列的存储器结构的情形一样,存储器控制器502可发送指定行地址的存储器访问命令,随后发送指定列地址的另一存储器访问命令。

作为另一示例,存储器控制器502可发送具有不完整地址信息的存储器访问命令,该不完整地址信息没有指定行地址或列地址。在此情形下,行选择器534可被配置为接受由RARF 530针对该命令所生成的行地址作为输入,并且列选择器536可被配置为接受由CARF532针对该命令所生成的列地址作为输入。

作为又一示例,存储器控制器502可发送不完整地址信息没有指定行地址的第一存储器访问命令,随后发送不完整地址信息没有指定列地址的第二存储器访问命令。在此情形下,行选择器534可被配置为接受由RARF 530针对第一命令所生成的行地址作为输入,并且列选择器536可被配置为接受由CARF 532针对第二命令所生成的列地址作为输入。

作为又一示例,存储器控制器502可发送没有指定行地址的具有不完整地址信息的第一存储器访问命令,随后发送指定列地址的第二存储器访问命令。在此情形下,行选择器534可被配置为接受由RARF 530针对第一命令所生成的行地址作为输入,并且列选择器536可被配置为接受第二命令中所指定的列地址作为输入,且不接受由CARF 532针对第二命令所生成的列地址作为输入。

作为又一示例,存储器控制器502可发送指定行地址的第一存储器访问命令,随后发送不完整地址信息没有指定列地址的第二存储器访问命令。在此情形下,行选择器534可被配置为接受第一命令中所指定的行地址作为输入且不接受由RARF 530针对第一命令所生成的行地址作为输入,并且列选择器536可被配置为接受由CARF 532针对第二命令所生成的列地址作为输入。

作为又一示例,存储器控制器502可发送指定行地址或列地址中的一项但不指定另一项的具有不完整地址信息的存储器访问命令。在此情形下,行选择器534或列选择器536中的一者可被配置为接受分别由RARF 530或CARF 532针对该命令所生成的行地址或列地址作为输入,并且行选择器534或列选择器536中的另一者可被配置为分别接受存储器访问命令中所指定的行地址或列地址作为输入。

行地址和/或列地址分别由存储器控制器502经由命令/地址总线所发送的一个或多个程序地址命令,在RARF 530和/或CARF 532中进行预编程。然后,针对具有存储器控制器502所发送的不完整地址信息的一个或多个后续存储器访问命令,预编程地址可以由近存储器地址生成单元528靠近存储器生成。

例如,经由命令/地址总线,存储器控制器502可以向存储器模块508发送指定地址的程序地址命令,该地址既包括行地址也包括列地址。行地址可存储在RARF 530中,并且列地址可存储在CARF 532中。然后,具有不完整地址信息的一个或多个后续存储器访问命令可以由存储器控制器502,经由命令/地址总线发送至存储器模块508。针对具有不完整地址信息的这些后续存储器访问命令中的每个命令,预编程行地址和预编程列地址可以由RARF530和CARF 532靠近存储器生成。

作为另一示例,经由命令/地址总线,存储器控制器502可以向存储器模块508发送指定行地址或列地址但没有既指定行地址也指定列地址的程序地址命令。如果指定行地址,则可以将其存储在RARF 530中。另一方面,如果指定列地址,则可以将其存储在CARF532中。然后,具有不完整地址信息的一个或多个后续存储器访问命令可以由存储器控制器502,经由命令/地址总线发送至存储器模块508。针对具有不完整地址信息的这些后续存储器访问命令中的每个命令,预编程行地址或预编程列地址可分别由RARF 530或CARF 532靠近存储器生成。后续存储器访问命令可指定进行了预编程且靠近存储器生成的行地址或列地址中的另一者。

RARF 530和/或CARF 532包含能够存储多个预编程地址的多个存储位置。每个此类存储位置可以与索引(例如,0、1、2等)相关联。预编程地址可通过其索引而引用于具有不完整地址信息的存储器访问命令中。

例如,程序地址命令可以由存储器控制器502来发送,以对RARF 530的索引1处的行地址进行预编程,并对CARF 532的索引1处的列地址进行预编程。然后,存储器控制器502所发送的后续存储器访问命令可指定索引1,并且可以针对该命令,靠近存储器生成分别存储在RARF 530和CARF 532中的索引1处的预编程行地址和列地址。

存储器访问命令可指定不同的索引。例如,存储器访问命令可指定针对RARF 530的索引以及针对CARF 532的不同索引。在此情形下,可针对该命令,靠近存储器生成RARF530指定索引处的预编程行地址,并且可针对该命令,靠近存储器生成不同的CARF 532指定索引处的预编程列地址。

存储器访问命令可仅指定针对RARF 530的索引或仅指定针对CARF 532的索引。在此情形下,可针对该命令,靠近存储器生成该命令所指定的RARF 530或CARF 532索引处的预编程行地址或预编程列地址,并且可通过该命令来指定行地址和列地址中的另一者。

如所指示,一旦RARF 530和/或CARF 532进行了预编程或以其他方式存储了地址,具有不完整地址信息的后续存储器访问命令可以由存储器控制器502,经由命令/地址总线来发送,而不必指定每个此类后续存储器访问命令中存储的地址。结果,后续存储器访问命令不会消耗它们在存储器访问命令中指定所存储地址的情况下将消耗的命令/地址总线带宽,因为可与每个此类命令一起传输的位更少。

不同存储器模块(例如,108-0、108-1、108-2)用其各自RARF和/或CARF中的每项中的不同行地址和/或列地址进行预编程或以其他方式来存储该这些不同行/列地址。这允许具有不完整地址信息的单个后续广播存储器访问命令由存储器控制器502,经由命令/地址总线来发送,以通过利用相应RARF和/或CARF中存储的近存储器生成行地址和/或列地址来访问数据尚未地址对齐的不同存储器模块中的每个模块处(例如,存储在不同的行地址和/或列地址处)的数据。

存储器控制器502所发送的程序地址命令对RARF 530和CARF 532中的行地址和/或列地址的预编程执行于命令/地址总线的空闲周期期间。然后,针对存储器控制器502所发送的多个后续存储器访问命令,预编程行地址和/或列地址由RARF 530和/或CARF 532靠近存储器重复生成。换句话说,由于RARF 530和/或CARF 532所提供的近存储器地址生成能力,经由命令/地址总线来发送程序地址命令所消耗的命令/地址总线带宽可分摊于多个后续存储器访问命令之间。

近存储器地址生成单元包括地址计算单元,用以向存储器模块提供近存储器地址计算功能。图6是包括近存储器地址生成单元628的示例性存储器模块608的示意图,近存储器地址生成单元用于为指定不完整地址信息的存储器访问命令生成近存储器地址。与图5的存储器模块508类似,存储器模块608可包括提供了多个存储器位置的存储器结构620,其中存储器位置610是一个示例。存储器模块608可经由命令/地址总线而电连接到存储器控制器602。例如,存储器模块608可以是经由命令/地址总线106而连接到存储器控制器102的图1中的存储器模块108之一。因此,存储器控制器602可以是例如图1中的存储器控制器102。存储器模块608可包括PIM执行单元622、行解码器624、列解码器626、RARF 630、CARF632、行选择器634和列选择器646,也类似于图5中的存储器模块508。

然而,与图5中的存储器模块508不同,存储器模块608包括电连接到RARF 630、CARF 632和PIM单元622的地址计算单元638。

地址计算单元638被配置为使用可配置的步幅来分别递增或递减RARF 630和CARF632中存储的行地址和/或列地址。步幅可预配置于地址计算单元638内。另外或可选地,步幅可通过具有不完整地址信息的存储器访问命令而预编程于地址计算单元638中,该不完整地址信息从存储器控制器602,经由命令/地址总线来发送,其中步幅通过该命令来指定。

例如,针对具有在存储器模块608处所接收的不完整地址信息的存储器访问命令,在访问了存储器结构620中的一个存储器位置之后,地址计算单元638可递增、递减或乘以存储在CARF 632中的列地址。同样地,另外或可选地,针对存储器访问命令,在访问了存储器结构520中的一个存储器位置之后,地址计算单元638可递增、递减或乘以存储在RARF630中的行地址。具有存储器模块608所接收的不完整地址信息的下一存储器访问命令可以由RARF 630和/或CARF 632生成递增、递减或倍增的地址。可针对多个存储器访问命令继续此过程,从而避免需要通过发送多个程序地址命令来消耗命令/地址总线的带宽。相反,第二地址和后续地址可以由地址计算单元628使用初始程序地址命令所指定的单个起始地址来计算,并且由地址计算单元628使用步幅进行一连串简单计算。除了按步幅递增之外,地址计算单元628还可支持许多种地址计算,包括按步幅递减,按步幅相乘等等。

地址计算单元628可访问或被提供与存储器结构620相关联的PIM执行单元622所计算的值或从存储器结构620中访问的值以用作地址。地址计算单元628然后可使用此类地址来计算待编程到RARF 630和CARF 632中的行地址和列地址。此类使用的示例可包括:从存储器结构620中读取地址偏移值;使用PIM执行单元622将该地址偏移值添加到数据结构的预定基地址中;以及使用地址计算单元628来生成所得的待编程到RARF 630和CARF 632中的行地址和列地址。

可以由地址计算单元628而非PIM单元622来执行:将从存储器结构620中读取的偏移添加到RARF 630或CARF 632中存储的基地址。

多个存储器模块中的地址计算单元允许具有不完整地址的单个存储器访问命令由存储器控制器或主机,经由命令/地址总线来发送,以应用于每个存储器模块中的不同地址,因为与每个存储器模块相关联的偏移以及可能的基地址可不同,这是由于它们单独存储在其相应RARF/CARF和/或相应存储器结构中。地址计算单元进一步减少了对命令/地址总线的带宽需求,这是因为偏移从与每个存储器模块相关联的存储器结构中来读取。因此,无需通过命令/地址总线来传输偏移。注意,从存储器结构中读取偏移也可经由发送至多个存储器模块的广播或多播存储器访问命令来执行,从而进一步减少命令/地址总线带宽需求量。

图7示出了一示例性系列的程序地址命令740-1、740-2和740-3以及存储器访问命令742-1、742-2和742-3,用于访问在存储器模块108之间尚未进行地址对齐且存储在存储器位置处的数据。在此示例中,存在三个存储器访问命令742-1、742-2和742-3,用于访问存储器模块108中尚未进行地址对齐的不同存储器位置。通过第一存储器访问命令742-1待使用的程序地址命令740-1、740-2和740-3,用存储器模块108对用于近存储器地址生成的起始地址进行预编程。然后,针对第二存储器访问命令742-2,将起始地址递增固定步幅(例如,1)。然后,针对第三存储器访问命令742-3,将这些地址再次增加固定步幅。这样,利用存储器模块108的近存储器地址生成能力,可通过存储器控制器102经由命令/地址总线106所发送的仅六个命令来实现计算,这与上述图3中所需的九个命令相反。

详细地,程序地址命令740-1由存储器控制器102,经由通往存储器模块108-0的命令/地址总线106而发送至存储器模块108-0,以将模块108-0的模块相对起始地址设置为“0”。

然后,程序地址命令740-2由存储器控制器102,经由通往存储器模块108-1的命令/地址总线106而发送至存储器模块108-1,以将模块108-1的模块相对起始地址设置为“1”。

然后,程序地址命令740-2由存储器控制器102,经由通往存储器模块108-2的命令/地址总线106而发送至存储器模块108-2,以将模块108-2的模块相对起始地址设置为“2”。

然后,经由命令/地址总线106,存储器控制器102将具有不完整地址信息(例如,无地址)的存储器访问命令742-1广播到存储器模块108-0、108-1和108-2中的每个模块。命令742-1指定操作OP-1和操作数X-1。例如,操作OP-1可以是PIM命令,诸如乘法或加法。虽然操作OP-1可以是PIM命令,但是操作OP-1也可以是简单的存储器加载命令或其他命令。例如,假设操作OP-1是乘法并且操作数X-1是数字5,则基于程序地址命令740所预编程的模块相对起始地址,命令742-1将模块108-0的存储器位置“0:0”处存储的数据乘以5,将模块108-1的存储器位置“1:1”处存储的数据乘以5,并且将存储器模块108-2的存储器位置“2:2”处存储的数据乘以5。在每次乘法之后,存储器模块108的模块相对起始地址可递增固定的步幅(例如,1),使得存储器模块108-0、108-1和108-2的模块相对起始地址现在分别为“1”、“2”和“3”。

然后,经由命令/地址总线106,存储器控制器102将具有不完整地址信息(例如,无地址)的存储器访问命令742-2广播到存储器模块108-0、108-1和108-2中的每个模块。命令742-2指定操作OP-1和不同的操作数X-2。例如,假设操作OP-1是乘法并且操作数X-2是数字8,则基于当前模块相对起始地址,命令742-2将模块108-0的存储器位置“0:1”处存储的数据乘以8,将模块108-1的存储器位置“1:2”处存储的数据乘以8,并且将存储器模块108-2的存储器位置“2:3”处存储的数据乘以8。在每次乘法之后,存储器模块108的模块相对起始地址可递增固定的步幅(例如,1),使得存储器模块108-0、108-1和108-2的模块相对起始地址现在分别为“2”、“3”和“0”。

然后,经由命令/地址总线106,存储器控制器102将具有不完整地址信息(例如,无地址)的存储器访问命令742-3广播到存储器模块108-0、108-1和108-2中的每个模块。命令742-3指定操作OP-1和不同的操作数X-3。例如,假设操作OP-1是乘法并且操作数X-3是数字0,则基于当前模块相对起始地址,命令742-3将模块108-0的存储器位置“0:2”处存储的数据乘以0,将模块108-1的存储器位置“1:3”处存储的数据乘以0,并且将存储器模块108-2的存储器位置“2:0”处存储的数据乘以0。

作为示例,存储器控制器102和存储器模块108可支持以下命令来支持近存储器地址生成:

memory_access_command operation,[mask]

program_[row,col]_address_commandmemory_module_id,module_relative_address

上述第一命令表示具有不完整地址信息的示例性广播或多播存储器访问命令格式,不完整地址信息用于发送至共享了命令/地址总线的两个或更多个存储器模块,诸如HBM存储器的通道内的DRAM库。如果是广播命令,则该命令可用于共享了命令/地址总线的所有存储器模块。如果是多播命令,则该命令指定位掩码作为选择以下项的子集的参数:所有存储器模块中共享了该命令所指向的命令/地址总线的两个或更多个存储器模块。可选地,该命令可具有掩码,该掩码在所有存储器模块的子集处抑制了该命令。

广播或多播存储器访问命令也可指定操作类型作为参数。该操作可以是例如存储器加载。然而,在存储器模块具有PIM能力的情况下,可指定PIM操作诸如乘法或加法用于近存储器处理。值得注意的是,与常规的存储器访问命令不同,上述存储器访问命令可以在不指定任何地址信息或仅指定不完整地址信息的情况下发送。并且与常规的存储器访问命令不同,存储器模块的近存储器地址生成单元可针对上述存储器访问命令而靠近存储器生成丢失地址或丢失地址部分。

第二命令是用于经由共享命令/地址总线而发送至存储器模块的示例性程序地址命令格式。该命令接受该命令所针对的存储器模块的标识符作为参数。该命令也接受地址参数,地址参数可以是行地址、列地址、行地址与列地址、或可依据程序地址命令类型而变化的其他模块相对地址。例如,可以有不同类型的程序地址命令用于分别用行地址和列地址分别对RARF和CARF进行编程。

虽然本文提出的程序地址命令分别对每个存储器模块进行编程,但是可选地,具有相关联掩码的广播程序地址命令或多播程序地址命令可以对具有相同模块相对地址的多个存储器模块进行编程。并且如所提及,程序地址命令的其他变型可包括:分别对行地址和列地址或其他模块相对地址进行编程。

某些计算机存储器技术(诸如混合存储器立方体(或仅简称“HMC”)和HBM存储器可以将许多存储器层堆栈在基本裸片顶部上。此类基本裸片可潜在地拥有近存储器计算能力,诸如分别为图5和图6的近存储器地址生成单元528和628。

近存储器地址生成单元528和628可靠近三维(3-D)堆栈存储器的存储器层中的存储器阵列/组或常规DRAM放置。

各实施方案也可应用于除DRAM以外的其他形式的存储器,诸如非易失性存储器、快闪存储器和嵌入式DRAM。

虽然一些实施方案描绘了用以将待使用的单个起始地址与所建议的存储器访问命令中的任何命令相关联的状态和逻辑,但针对多个PIM操作复制所建议的状态和逻辑可以使多个起始地址由近存储器地址生成单元或不同PIM操作来跟踪,诸如跟踪每个存储器模块中的不同地址以供乘法操作和加法操作。

存储器控制器102可以与存储器模块108一起采用确定性双倍数据速率(或仅简称为“DDR”)。根据一些实施方案,可通过在存储器结构108之间适当地进行同步来支持DDR。例如,需要DRAM行开启(激活)的存储器访问命令可花费比DRAM行缓存命中率更长的时间。为了允许具有不完整地址信息的广播或多播存储器访问命令访问不同存储器模块之间的不同地址,可扩充存储器控制器102以同步不同存储器模块之间的行开启。

本文提到的“实施方案”意味着具体的特征、结构或特性结合本发明的至少一个实施方案进行了描述,并且可包括在本发明的至少一个实施方案中。在说明书中不同地方出现的短语“在实施方案中”和“根据实施方案”不一定都指相同的实施方案,也并非与其他实施方案相互排斥的单独或替代实施方案。

尽管各种附图中的一些附图按具体顺序示出了多个逻辑级,但是可以对不依赖于顺序的级进行重新排序,并且可以对其他级进行组合或分解。虽然特别提及了一些重新排序或其他分组,但是本文提出的排序和分组并非替代方案的详尽列表。

在前述具体实施方式和所附权利要求中,尽管在一些情况下,术语第一、第二等在本文中用于描述各种元件,但这些元件不应受到这些术语的限制。这些术语仅用于区分一个元件与另一元件。例如,第一计算设备可称为第二计算设备,并且类似地,第二计算设备可称为第一计算设备。第一计算设备和第二计算设备都是计算设备,但它们并非相同的计算设备。

如在前述具体实施方式和所附权利要求中所用,单数形式“一个/种”和“该/所述”也旨在包括复数形式,除非上下文另外明确指出。如在前述具体实施方式和所附权利要求中所用,术语“和/或”是指并涵盖一个或多个相关联的所列项目的任何和所有可能的组合。

如在前述具体实施方式和所附权利要求中所用,术语“基于”、“根据”、“包括”、“包含”和/或“含有”指定了规定特征、整数、步骤、操作、元件和/或部件的存在,但并不排除一个或多个其他特征、整数、步骤、操作、元件、部件和/或其群组的存在或添加。

如前述具体实施方式和所附权利要求中所用,术语“如果”任选地解释为意指“当…时”或“在…之后”或“响应于确定”或“响应于检测”或“根据确定”,这取决于上下文。类似地,短语“如果确定了”或“如果检测到[规定条件或事件]”任选地解释为意指“在确定…后”或“响应于确定”或“在检测到[规定条件或事件]后”或“响应于检测到[规定条件或事件]”或“根据检测到[规定条件或事件]的确定”,这取决于上下文。

在前述说明书中,已经参考许多具体细节描述了本发明的实施方案,这些具体细节可以随具体实施不同而变化。因此,应将该说明书和附图视为说明性的而非限制性的。

- 协调存储器命令的方法和高带宽存储器系统

- 具有嵌埋位线的存储器阵列及形成存储器阵列的方法

- 具有多个细丝的RRAM存储器单元、存储器电路及其形成方法

- 存储器地址生成装置以及具有它的处理器、存储器地址生成方法

- 命令窗口生成器和具有命令窗口生成器的存储器装置