一种模数转换单元的控制装置及控制方法

文献发布时间:2023-06-19 19:37:02

技术领域

本发明涉及模数转换单元控制领域,特别涉及一种模数转换单元的控制装置及控制方法。

背景技术

模数转换单元是一种将模拟量转换为数字量的特殊电路。模数转换单元控制器是一种对模数转换单元的采样率、采样间隔、采样方式进行控制,接收模数转换单元转换后数字量,并产生中断的特殊电路。

系统将模数转换单元控制器接入总线,中央处理单元(即CPU)通过系统总线对模数转换单元控制器的寄存器进行配置。其后模数转换单元控制器开始工作,完成对模数转换单元的采样调度,并将模数转换单元返回的数字量写入结果寄存器。最后中央处理单元通过中断方式对结果寄存器进行读取,并进行相关处理。

现有技术通常在模数转换单元控制器中设计一组接口,中央处理单元通过该接口对模数转换单元控制器进行配置并读回数据。某些场景下,需要不断更改控制器的配置并对采集到的大量数据进行处理。此时,一组接口将不能满足更改配置、读取数据两种操作同时进行,从而降低了访问效率和采样效率。

发明内容

为解决上述技术问题,本发明提供了一种模数转换单元的控制装置及控制方法,以达到既能保留现有技术的操作途径,又通过增加接口提高访问效率和采样效率,并且能够实现连续采集,提升转换效率的目的。

为达到上述目的,本发明的技术方案如下:

一种模数转换单元的控制装置,包括接口转换单元、物理寄存器和影子寄存器,所述物理寄存器包括控制寄存器、结果寄存器和状态寄存器,所述接口转换单元上设置接口A和接口B,CPU通过接口A访问物理寄存器,DMA通过接口A访问结果寄存器或者通过接口B访问影子寄存器;所述接口转换单元用于完成协议转换,将接口A上的请求转换为对物理寄存器的读写操作,将接口B上的请求转换为对影子寄存器的读操作;所述控制寄存器用于产生控制信号,对模数转换单元的采样过程进行控制,模数转换单元采样完成后,将转换后的返回值同时写入结果寄存器和影子寄存器,且写入的数据相同;状态寄存器用于接收模数转换单元返回的转换完成标志,并产生中断。

进一步的技术方案中,所述控制寄存器和模数转换单元之间还依次连接有组包单元和采集队列,所述组包单元用于将采集配置打包,以集合的形式输出到采集队列;所述采集队列用于缓存打包的采集配置,与模数转换单元和接口转换单元进行通信。

一种模数转换单元的控制方法,采用如上所述的一种模数转换单元的控制装置,包括两种处理过程,处理过程一是采用接口A进行模数转换单元的写操作,通过接口B进行模数转换单元的读操作;处理过程二是只采用接口A进行模数转换单元的读和写操作。

进一步的技术方案中,所述处理过程一包括如下步骤:

步骤1,CPU通过接口A发出写总线请求,同时DMA通过接口B发出读总线请求;

步骤2,接口转换单元将接口A的写总线请求转换成物理寄存器的写信号,同时将接口B的读总线请求转换成对影子寄存器的读信号;

步骤3,物理寄存器下的控制寄存器完成配置后向模数转换单元发出控制信号;

步骤4,模数转换单元在控制信号的调度下,完成采样和数据转换;

步骤5,模数转换单元将数据同时返回结果寄存器和影子寄存器;

步骤6,状态寄存器收到模数转换单元返回的转换完成标志后产生中断,DMA将获取到的转换值写入存储,清除中断,返回步骤1。

进一步的技术方案中,所述处理过程二包括如下步骤:

步骤1,CPU通过接口A发出写总线请求;

步骤2,接口转换单元将接口A的写总线请求转换成物理寄存器的写信号;

步骤3,控制寄存器完成配置后向模数转换单元发出控制信号;

步骤4,模数转换单元在控制信号的调度下,完成采样和数据转换;

步骤5,模数转换单元将数据返回结果寄存器;

步骤6,状态寄存器收到模数转换单元返回的转换完成标志后产生中断;

步骤7,DMA通过接口A发出读结果寄存器的请求;

步骤8,接口转换单元将接口A的读请求转换成对物理寄存器中结果寄存器的读信号;

步骤9,DMA将获取到的转换值写入存储,清除中断,返回步骤1。

更进一步的技术方案中,步骤3中,当采集队列的可用深度减少到0时,将发出表示忙碌的信号到接口转换单元,暂停接口转换单元对接口A请求的响应,此时CPU无法再次通过接口A进行新的采集配置;采集队列缓存的采集配置依次发送给模数转换单元,当采集队列的可用深度达到设定的阈值时,表示忙碌的信号将无效,接口转换单元恢复对接口A的响应,CPU可再次进行新的采集配置。

优选地,所述设定的阈值为采集队列总深度的一半。

通过上述技术方案,本发明提供的一种模数转换单元的控制装置及控制方法具有如下有益效果:

1、本发明的控制装置可以只使用接口A进行读写操作,处理流程和现有技术的处理流程一致,这保证了本设计兼容现有技术的操作途径。

2、本发明的控制装置由于包含两个接口,可以使用接口A接收写总线请求,接口B接收读总线请求,这保证了CPU的写总线请求和DMA的读总线请求可并行工作;能以较少增加硬件资源的代价,提高访问效率和采样效率。

3、本发明的控制装置内部设置了组包单元和采集队列,通过采集队列的忙碌信号反馈机制将提升采样效率和访问效率。

4、本发明将设定的阈值为采集队列总深度的一半,这样为CPU留出了缓存余量,将提升转换的效率。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍。

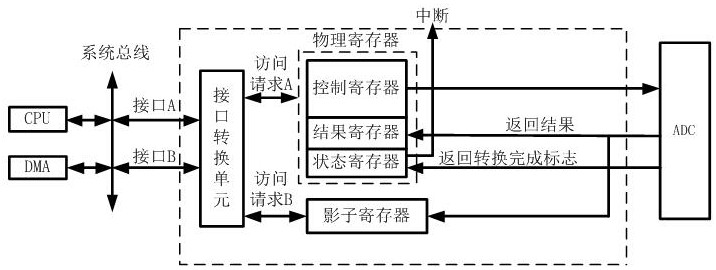

图1为本发明实施例1所公开的一种模数转换单元的控制装置示意图。

图2为本发明实施例2所公开的一种模数转换单元的控制装置示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。

实施例1

本发明提供了一种模数转换单元的控制装置,如图1所示,包括接口转换单元、物理寄存器和影子寄存器。

接口转换单元上设置接口A和接口B,接口A与接口B用于连接系统总线和接口转换单元。其中,接口A只能访问物理寄存器,接口B只能访问影子寄存器。

CPU(中央处理单元)通过接口A访问物理寄存器,DMA(直接存储访问单元)通过接口A访问结果寄存器或者通过接口B访问影子寄存器。

接口转换单元用于完成协议转换,将接口A上的请求转换为对物理寄存器的读写操作,将接口B上的请求转换为对影子寄存器的读操作。

物理寄存器包括控制寄存器、结果寄存器和状态寄存器。其中,控制寄存器接受接口A上的写请求,完成采集配置;控制寄存器用于产生控制信号,对模数转换单元的采样过程进行控制;结果寄存器接受接口A上的读请求返回转换结果到接口转换单元;状态寄存器用于接收模数转换单元返回的转换完成标志,并产生中断。

模数转换单元采样完成后,将转换后的返回值同时写入结果寄存器和影子寄存器,且保证写入的数据相同。此时,通过接口A可以获取结果寄存器内的转换值,也可通过接口B获取影子寄存器内的转换值。如果使用接口B持续获取转换值,则通过接口A可不断地更改配置,完成不同形式的采样。

一种模数转换单元的控制方法,采用如实施例1的一种模数转换单元的控制装置,包括两种处理过程,处理过程一是采用接口A进行模数转换单元的写操作,通过接口B进行模数转换单元的读操作;处理过程二是只采用接口A进行模数转换单元的读和写操作。

处理过程一步骤如下:

步骤1,CPU通过接口A发出写总线请求,同时DMA通过接口B发出读总线请求;

步骤2,接口转换单元将接口A的写总线请求转换成物理寄存器的写信号,同时将接口B的读总线请求转换成对影子寄存器的读信号;

步骤3,物理寄存器下的控制寄存器完成配置后向模数转换单元发出控制信号;

步骤4,模数转换单元在控制信号的调度下,完成采样和数据转换;

步骤5,模数转换单元将数据同时返回结果寄存器和影子寄存器;

步骤6,状态寄存器收到模数转换单元返回的转换完成标志后产生中断,DMA将获取到的转换值写入存储,清除中断,返回步骤1。

处理过程二步骤如下:

步骤1,CPU通过接口A发出写总线请求;

步骤2,接口转换单元将接口A的写总线请求转换成物理寄存器的写信号;

步骤3,控制寄存器完成配置后向模数转换单元发出控制信号;

步骤4,模数转换单元在控制信号的调度下,完成采样和数据转换;

步骤5,模数转换单元将数据返回结果寄存器;

步骤6,状态寄存器收到模数转换单元返回的转换完成标志后产生中断;

步骤7,DMA通过接口A发出读结果寄存器的请求;

步骤8,接口转换单元将接口A的读请求转换成对物理寄存器中结果寄存器的读信号;

步骤9,DMA将获取到的转换值写入存储,清除中断,返回步骤1。

实施例2

为了实现通过接口A不断更改配置,接口B持续获取转换值的应用场景,需对整体的流程进行调度,才能达到连续采集的效果。如图2所示,本实施例2中,控制寄存器和模数转换单元之间还依次连接有组包单元和采集队列,此时组包单元和采集队列将发挥作用。

控制寄存器的采集配置将发送给组包单元,组包单元将采集配置打包,以集合的形式输出到采集队列。这将简化组包单元和采集队列接口的复杂性。

采集队列用于缓存打包的采集配置,与模数转换单元和接口转换单元进行通信。

根据实际将采集队列的深度设置为8-16,每收到一组采集配置采集队列的可用深度减少1,每发出一组采集配置采集队列的可用深度增加1。当采集队列可用深度减少到0,发出表示忙碌的控制信号到接口转换单元,暂停接口转换单元对接口A请求的响应。由于CPU无法通过总线收到接口A的完成响应,此时CPU无法再次通过接口A进行新的采集配置。这也保证了采集队列不会因为再次收到新数据而丢失已有数据。

此时,缓存的采集配置依次发送给模数转换单元。为减少系统的暂停时间,当采集队列的可用深度为设定阈值时(设定的阈值一般为采集队列总深度的一半),表示忙碌的控制信号将无效,接口转换单元恢复对接口A的响应,CPU可再次进行新的采集配置。

如果采集队列的可用深度为1就将表示忙碌的控制信号置为无效,CPU可能再次发送新的采集配置,导致采集队列的深度减少为0,将再次引起CPU的停顿。而可用深度为4时无效表示忙碌的控制信号,为CPU留出了缓存余量,将提升转换的效率。

因此,上述双接口的结构可以提升访问效率和采样效率。另外,由于逻辑简单,上述结构不会增加系统的复杂度。

一种模数转换单元的控制方法,采用如上的一种模数转换单元控制装置,同样包括两种处理过程,处理过程一是采用接口A进行模数转换单元的写操作,通过接口B进行模数转换单元的读操作;处理过程二是只采用接口A进行模数转换单元的读和写操作。

处理过程一步骤如下:

步骤1,CPU通过接口A发出写总线请求,同时DMA通过接口B发出读总线请求;

步骤2,接口转换单元将接口A的写总线请求转换成物理寄存器的写信号,同时将接口B的读总线请求转换成对影子寄存器的读信号;

步骤3,物理寄存器下的控制寄存器完成配置后通过组包单元和采集队列向模数转换单元发出控制信号;

当采集队列的可用深度减少到0时,将发出表示忙碌的信号到接口转换单元,暂停接口转换单元对接口A请求的响应,此时CPU无法再次通过接口A进行新的采集配置;

采集队列缓存的采集配置依次发送给模数转换单元,当采集队列的可用深度达到设定的阈值时,表示忙碌的信号将无效,接口转换单元恢复对接口A的响应,CPU可再次进行新的采集配置;

步骤4,模数转换单元在控制信号的调度下,完成采样和数据转换;

步骤5,模数转换单元将数据同时返回结果寄存器和影子寄存器;

步骤6,状态寄存器收到模数转换单元返回的转换完成标志后产生中断,DMA将获取到的转换值写入存储,清除中断,返回步骤1。

处理过程二步骤如下:

步骤1,CPU通过接口A发出写总线请求;

步骤2,接口转换单元将接口A的写总线请求转换成物理寄存器的写信号;

步骤3,控制寄存器完成配置后通过组包单元和采集队列向模数转换单元发出控制信号;

当采集队列的可用深度减少到0时,将发出表示忙碌的信号到接口转换单元,暂停接口转换单元对接口A请求的响应,此时CPU无法再次通过接口A进行新的采集配置;

采集队列缓存的采集配置依次发送给模数转换单元,当采集队列的可用深度达到设定的阈值时,表示忙碌的信号将无效,接口转换单元恢复对接口A的响应,CPU可再次进行新的采集配置;

步骤4,模数转换单元在控制信号的调度下,完成采样和数据转换;

步骤5,模数转换单元将数据返回结果寄存器;

步骤6,状态寄存器收到模数转换单元返回的转换完成标志后产生中断;

步骤7,DMA通过接口A发出读结果寄存器的请求;

步骤8,接口转换单元将接口A的读请求转换成对物理寄存器中结果寄存器的读信号;

步骤9,DMA将获取到的转换值写入存储,清除中断,返回步骤1。

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

- 一种信号控制装置及方法、显示控制装置及方法、显示装置

- 一种功率单元、功率单元控制系统及其控制方法

- 一种扫描单元、冗余触发器的输出控制方法及装置

- 一种直流配电系统储能单元荷电状态均衡控制方法及装置

- 一种用于储能单元充冷的控制方法及充冷装置

- 一种模数转换电路控制方法、装置、设备及模数转换电路

- 用于操控驱动装置的控制单元、具有驱动装置和控制单元的马达单元以及用于制造马达单元的方法