一种异质衬底薄膜转移对准方法

文献发布时间:2023-06-19 13:45:04

技术领域

本发明属于半导体工艺技术领域,特别涉及了一种薄膜转移对准方法。

背景技术

不同材料和不同结构的器件具有各自独特的性能优势,将这些材料通过键合等技术手段集成到同一衬底上后,能够融合发挥不同材料器件的性能优势,获得更好的综合性能。为了实现更高密度的集成和更高精度的互连,其中一种技术手段是将GaAs、InP、GaN、SiC、LiNbO

针对这一问题,需要开发一种异质衬底薄膜转移对准方法,来解决异质衬底集成不同半导体材料器件的高精度对准问题。

发明内容

为了解决上述背景技术提到的技术问题,本发明提出了一种异质衬底薄膜转移对准方法,解决转移集成到其他衬底的异质材料薄膜上的结构与目标衬底上原有器件结构的对准问题。

为了实现上述技术目的,本发明的技术方案为:

一种异质衬底薄膜转移对准方法,包括以下步骤:

(1)在目标衬底正面完成器件电路的制备和对准标记A阵列的制备;

(2)在目标衬底背面,通过双面套刻完成对准标记B阵列的制备,其中对准标记B与对准标记A相互匹配;

(3)将待转移薄膜材料从原始衬底剥离转移到目标衬底正面;

(4)在转移至目标衬底上的薄膜材料正面,利用目标衬底背面的对准标记B,通过双面套刻,定位出目标衬底正面的对准标记A位置,并刻蚀掉该位置的薄膜材料,暴露出对准标记A阵列;

(5)利用对准标记A阵列,通过标准微电子工艺进行半导体器件流片以及与目标衬底器件结构的异质互连。

基于上述技术方案的优选方案,所述目标衬底的材质包括但不限于InP、GaAs、GaN、Si、SiC或金刚石。

基于上述技术方案的优选方案,其特征在于,所述目标衬底采用标准晶圆或者长度不超过5cm的小片。

基于上述技术方案的优选方案,在目标衬底正面制备的器件电路包括Si CMOS、SiPIN、Si BJT、InP HBT、GaAs HBT、GaN HEMT、SiC MOS、Ga

基于上述技术方案的优选方案,在目标衬底正面制备的器件电路的最小重复单元尺寸范围为100μm到20000μm。

基于上述技术方案的优选方案,对准标记A的形状为条形、十字形或米字形,尺寸范围为50μm×50μm至1000μm×1000μm,对准标记A阵列的间距在目标衬底正面制备的器件电路的最小重复单元的尺寸相同。

基于上述技术方案的优选方案,对准标记B的形状为条形、十字形或米字形,尺寸范围为50μm×50μm至1000μm×1000μm,对准标记B阵列的间距与对准标记A阵列的间距一致。

基于上述技术方案的优选方案,所述待转移薄膜材料包括但不限于Si、InP、GaAs、GaN、SiC、Ga

基于上述技术方案的优选方案,转移后的薄膜材料的厚度范围为50nm至20μm。

基于上述技术方案的优选方案,将待转移薄膜材料从原始衬底剥离转移到目标衬底正面的方式包括先剥离再键合的方式以及先键合再剥离的方式。

采用上述技术方案带来的有益效果:

本发明通过两次背面套刻和标记转移,解决了异质衬底集成薄膜材料的便捷有效的对准问题,通过两次背面套刻,将转移的薄膜材料和目标衬底器件纳入到同一对准参照系中,为后续基于标准微电子工艺的异质集成技术奠定基础,有助于进一步提升异质集成精度和集成密度。

附图说明

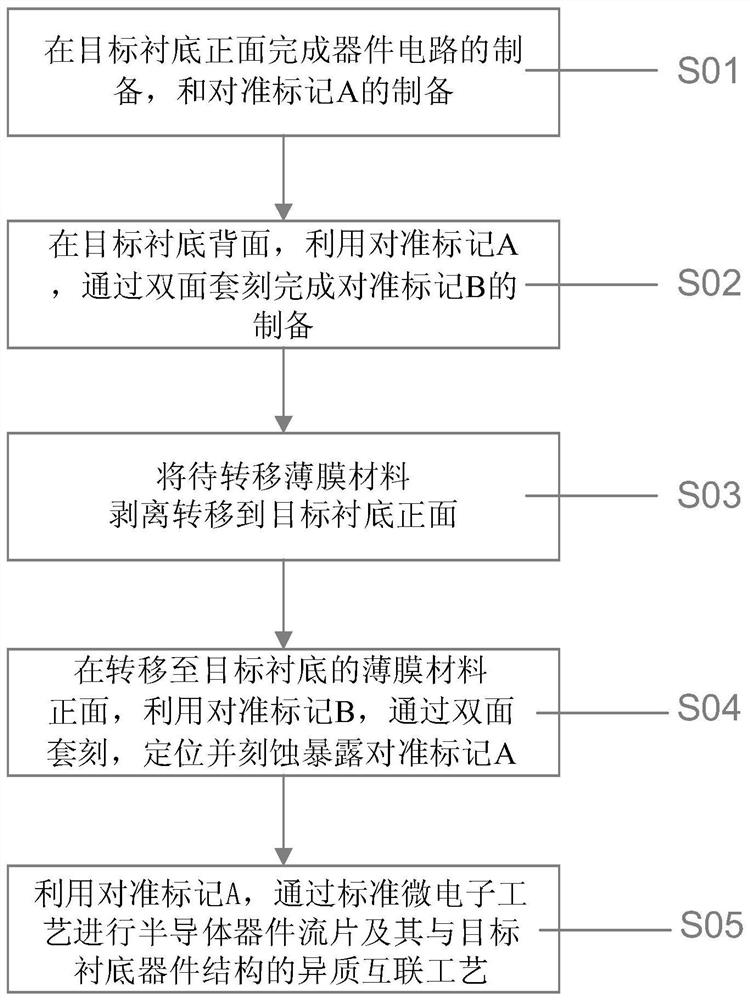

图1是本发明方法的流程图;

图2是目标衬底晶圆、待转移材料晶圆俯视示意图;

图3是在目标衬底晶圆上完成器件电路结构制备的示意图;

图4是对准标记A和对准标记B示意图;

图5是转移后的集成结构剖面示意图;

图6是利用对准标记B定位并刻蚀暴露出对准标记A的剖面示意图;

图7是利用对准标记B定位并刻蚀暴露出对准标记A的俯视示意图。

具体实施方式

以下将结合附图,对本发明的技术方案进行详细说明。

本发明设计了一种异质衬底薄膜转移对准方法,如图1所示,步骤如下:

步骤S01,在目标衬底正面完成器件电路的制备和对准标记A阵列的制备;

步骤S02,在目标衬底背面,通过双面套刻完成对准标记B阵列的制备,其中对准标记B与对准标记A相互匹配;

步骤S03,将待转移薄膜材料从原始衬底剥离转移到目标衬底正面;

步骤S04,在转移至目标衬底上的薄膜材料正面,利用目标衬底背面的对准标记B,通过双面套刻,定位出目标衬底正面的对准标记A位置,并刻蚀掉该位置的薄膜材料,暴露出对准标记A阵列;

步骤S05,利用对准标记A阵列,通过标准微电子工艺进行半导体器件流片以及与目标衬底器件结构的异质互连。

优选地,在如图2左图所示的目标衬底201上完成器件电路的制备,目标衬底201的材料类型包括但不限于InP、GaAs、GaN、Si、SiC、Diamond等半导体材料中的一种,本实施例中为SiC材料。

优选地,如图2左图所示的目标衬底201大小可以为2英寸、3英寸、4英寸、5英寸和8英寸等标准晶圆,也可以为长度不超过5cm的小片,本实施例中为4英寸晶圆。

优选地,在如图2左图所示的目标衬底201上完成的器件电路结构包括但不限于SiCMOS、Si PIN、Si BJT、InP HBT、GaAs HBT、GaN HEMT、SiC MOS、Ga

优选地,所述目标衬底201上的器件电路的最小重复单元301尺寸范围为100μm到20000μm。本实施例中为1000μm×1000μm,完成器件电路制备后的目标衬底如图3所示。

优选地,所述对准标记A的形状为条形、十字形、米字形等特殊形状,如图4的左图所示,对准标记A的尺寸大小范围为50μm×50μm到200μm×200μm之间,本实施例中为100μm×100μm。对准标记A阵列的间隔距离与目标衬底上器件电路的最小重复单元301的尺寸一致,距离大小为100μm到20000μm,本实施例中为x方向10000μm,y方向8000μm。

如图5所示,在上述步骤S02中,通过双面套刻,在目标衬底的背面制备出与正面对准标记A相匹配的对准标记B。优选地,所述对准标记B与对准标记A相互套刻,其形状为条形、十字形、米字形等特殊形状,如图4右图所示,对准标记B的尺寸大小范围为50μm×50μm到1000μm×1000μm之间,本实施例中为500μm×200μm。对准标记B阵列的间隔距离与目标衬底上器件电路的最小重复单元的尺寸以及对准标记A的间距一致,尺寸范围为100μm到20000μm,本实施例中为x方向10000μm,y方向8000μm。

优选地,所述的待转移薄膜材料202如图2右图所示,包括但不限于Si、InP、GaAs、GaN、SiC、Ga

优选地,转移后的薄膜材料202的厚度为50nm到20μm之间;

优选地,所述待转移薄膜材料202从原始衬底剥离转移到目标衬底201正面的方法包括但不限于先剥离再键合、先键合再剥离等方式,本实施例中为先将待转移薄膜材料衬底正面朝上与临时载片贴合,然后对待转移薄膜衬底背面进行减薄减薄至一定厚度,接着通过干法刻蚀至刻蚀停止层,然后去除停止层直至薄膜材料,然后将临时载片支撑的薄膜材料202与目标衬底永久键合,永久键合后与临时载片分离,转移后的集成结构剖面示意图如图5所示。

如图6和图7所示,在上述步骤S04中,通过接触式光刻机,利用对准标记B,在转移至目标衬底上的半导体材料薄膜正面,通过双面光刻套刻,定位出相应目标衬底正面的对准标记A的位置。然后通过刻蚀或者腐蚀等方法去除窗口601中的半导体外延层材料和停止层材料,从而暴露出对准标记A。其中图7的上半部分展示的是在目标衬底201上曝光窗口的示意图,而图7下半部分展示的是光刻曝光图形的放大细节。本实施例中,通过磷酸系溶液腐蚀去除InP HBT材料,通过盐酸系材料腐蚀去除InGaAs停止层。

优选地,曝光窗口601的长宽不小于对准标记A和对准标记B的尺寸,本实施例中曝光窗口601的尺寸为1000μm×1000μm。

在上述步骤S05中,优选地,通过步进式光刻机来识别对准标记A,并进行套刻,然后通过标准微电子工艺,在转移后的薄膜材料正面进行器件流片及其与目标衬底上器件结构的异质互连。

实施例仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明保护范围之内。