一种基于FPGA的SM4加密异构加速系统

文献发布时间:2023-06-19 19:33:46

技术领域

本发明涉及一种基于FPGA的SM4加密异构加速系统,属于计算机硬件加速技术领域。

背景技术

随着计算机网络的发展,越来越多的事务依赖于计算机进行处理,大量数据信息通过网络进行传递,数据安全的重要性愈发凸显。密码学是保障信息安全的重要支撑,通过对信息进行加密,明文数据被转换为不可理解的密文数据,使得攻击者即使能够获取数据也不能理解其含义。SM4是由我国自主研发的一种对称加密算法,具有效率高、易实现等优点。

SM4加密是典型的计算密集型任务,使用CPU处理加密任务,速度较低,并会消耗大量的CPU和内存资源,使CPU强大的逻辑处理能力不能得到充分利用。因此,将加密任务卸载到硬件加速器上,有效的解决方法。而FPGA具有定制化程度高、并行程度高、功耗低等特点,适合于在该场景下使用。

发明内容

本发明的目的是针对现有技术存在的不足,为了解决传统的CPU执行SM4时,加密任务速度慢、CPU资源得不到合理利用等技术问题,提出一种基于FPGA的SM4加密异构加速系统。

为了解决上述技术问题,本发明采用以下技术手段实现。

一种基于FPGA的SM4加密异构加速系统,包括SM4加密模块、HOST-FPGA通讯模块和OpenSSL拓展模块。

其中,SM4加密模块基于FPGA实现,包括加密模块和密钥扩展模块。

SM4加密模块操作包括异或、位移、S盒变换。进一步地,异或和位移使用组合逻辑实现,S盒变换基于LUT实现。进一步地,加密模块和密钥扩展模块均采用三十二级流水线架构,实现每个周期输出一个分组数据加密结果,以获得更高吞吐率。

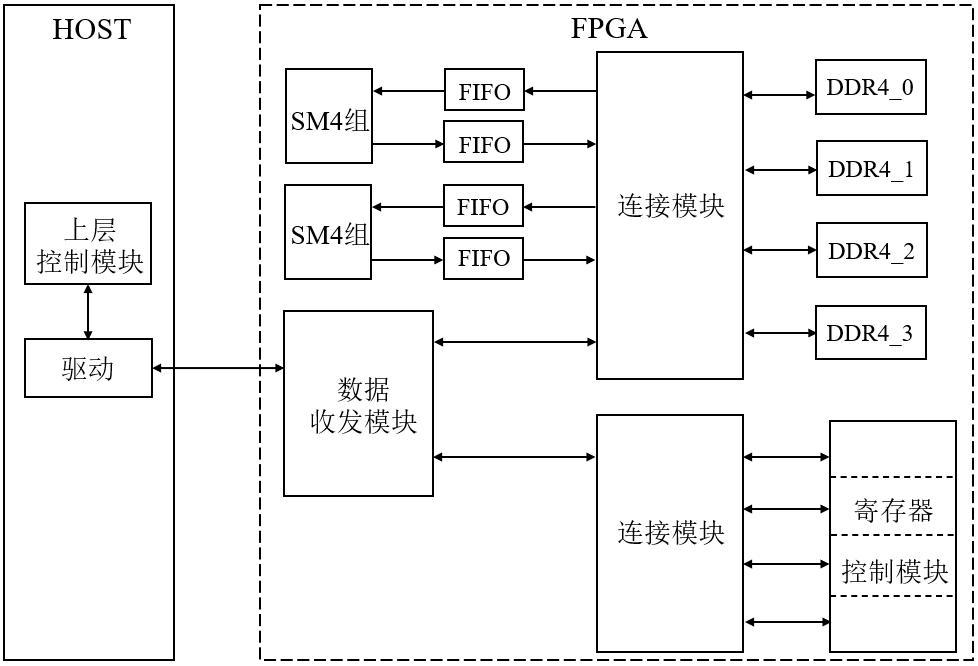

HOST-FPGA通讯模块基于PCIe实现,包括主机端和FPGA端。其中,主机端通过XDMA驱动和上层控制模块,实现数据收发;FPGA端通过数据收发模块、连接模块、DDR4模块、控制模块和FIFO缓存模块,实现数据的接收、处理和发送。

具体地,主机端发送的明文数据经过FPGA端的数据收发模块、连接模块被写入到DDR4模块中,FPGA从DDR4模块中取出数据并暂存入明文FIFO,SM4加密模块从明文FIFO中取数进行加密,加密结果暂存入密文FIFO,FPGA将密文FIFO中的数据写回DDR4模块,以供主机取回。

进一步地,上层控制模块采用多线程和多通道相结合的方式进行数据收发。在发送线程中,主机端轮流向2块DDR4发送明文数据;接收线程有2个,分别使用c2h0通道和c2h1通道从2块DDR4中读取加密结果。主机发数据、FPGA处理、主机取数据,形成三级流水线。

进一步地,DDR4模块采用2组4块DDR4,为实现数据收发和处理的三级流水线提供物理条件,最大限度降低等待延迟。其中,同一时刻同一块DDR4只能由一个设备接口对其进行读或写。为避免同时申请读写同一块DDR4,实现明文发送和密文接收的解耦,明文和密文在物理上要分开存放,2块DDR4为一组,1块存放明文数据,1块存放密文数据。FPGA在进行加密操作时,要同时读写2块DDR4,此时主机无法基于这2块DDR4进行数据的收发,因此,当其中一组在进行SM4加密时,另一组进行主机与FPGA之间的数据传输。

进一步地,控制模块采用地址指针来控制数据收发和读写。具体地,每组DDR4采用4个指针来指示当前数据状态,其中,写指针指向主机待写明文地址,读指针指向FPGA待取明文地址,写回指针指向FPGA待写密文地址,读回指针指向主机待取密文地址。读指针和写指针指示是否有空间写待加密明文,是否有明文待取出加密。写回指针和读回指针指示是否有空间写回密文,是否有密文待取出。

OpenSSL拓展模块基于OpenSSL透明地调用FPGA,实现SM4加密。

进一步地,OpenSSL拓展实现SM4硬件加密引擎;基于引擎机制,使得OpenSSL能够透明调用硬件加密方法,SM4引擎加载方式包括动态和静态两种。

有益效果

1.本发明实现基于FPGA的SM4硬件加密算法,具有功耗低、速度快、易于开发等优点。三十二级流水线架构使得单个SM4核数据吞吐率高达56.39Gbps,多引擎进一步提升了整体加密速度。

2.本发明所述的HOST-FPGA通讯框架采用地址映射模式,适用范围广。本发明组合使用多线程、多通道、多DDR4,充分利用PCIe带宽资源,实现数据收发过程的解耦,在避免资源竞争和提高并行度间取得平衡,吞吐率高达92Gbps。

3.本发明对上层提供简洁易用的调用接口,支持通过OpenSSL透明地调用FPGA进行SM4加密,方便本发明的使用和推广。

附图说明

图1为本发明的总体架构图;

图2为本发明中数据收发和处理三级流水线示意图;

图3为本发明中FPGA端数据流转过程示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

如图1-图3所示,一种基于FPGA的SM4加密异构加速系统,包括SM4加密模块、HOST-FPGA通讯模块和OpenSSL拓展模块。

所述SM4加密模块包括加密模块和密钥扩展模块,采用三十二级流水线架构,实现每个周期输出一个分组数据加密结果。

所述HOST-FPGA通讯模块包括主机端和FPGA端两部分,主机端通过驱动和上层控制模块实现数据收发,FPGA端通过数据收发模块、连接模块、DDR4模块、控制模块以及FIFO缓存模块实现数据的接收、处理和发送;所述上层控制模块采用多线程和多通道相结合的方式进行数据收发;所述DDR4模块采用两组四块DDR4,为实现数据收发和处理的三级流水线提供物理条件;所述控制模块采用地址指针控制数据收发和读写;所述OpenSSL拓展实现基于OpenSSL透明地调用FPGA进行SM4加密。

作为本发明的一种实施方式,所述SM4加密算法基于FPGA实现,由加密模块和密钥扩展模块构成,操作包括异或、位移、S盒变换;所述异或和位移使用组合逻辑实现,所述S盒变换基于LUT实现;所述加密模块和密钥扩展模块都采用三十二级流水线架构以获得更高吞吐率;一个128bit的明文数据经过32个周期完成加密,在不断流的情况下每个周期输出一个128bit加密结果。

作为本发明的一种实施方式,所述HOST-FPGA通讯模块基于PCIe3.0×16实现,包括主机端和FPGA端;主机端发送的明文数据经过FPGA端的数据收发模块、连接模块被写入到DDR4中,FPGA从DDR4中取出数据暂存入明文FIFO,SM4模块从明文FIFO中取数进行加密,加密结果暂存入密文FIFO,FPGA将密文FIFO中数据写回DDR4以供主机取回。

作为本发明的一种实施方式,所述主机端上层控制模块采用多通道和多线程相结合的方式进行数据收发;发送线程中,主机轮流向两块DDR4发送明文数据;接收线程有两个,分别使用c2h0通道和c2h1通道从两块DDR4中读取加密结果;主机发数据、FPGA处理、主机取数据形成三级流水线。

作为本发明的一种实施方式,所述DDR4模块采用两组四块DDR4,为实现数据收发和处理的三级流水线提供物理条件,最大限度降低等待延迟;同一时刻同一块DDR4只能由一个设备接口对其进行读或写,为避免同时申请读写同一块DDR4,实现明文发送和密文接收的解耦,明文和密文在物理上分开存放,两块DDR4为一组,一块存放明文数据,一块存放密文数据;FPGA在进行加密操作时,需要同时读写两块DDR4,此时主机无法基于这两块DDR4进行数据的收发,因此当其中一组在进行SM4加密时,另一组进行主机与FPGA之间的数据传输。

作为本发明的一种实施方式,所述控制模块采用地址指针控制数据收发和读写,每组DDR4采用四个指针来指示当前数据状态;写指针指向主机待写明文地址,读指针指向FPGA待取明文地址,写回指针指向FPGA待写密文地址,读回指针指向主机待取密文地址;所述读指针和写指针指示是否有空间写待加密明文,是否有明文待取出加密;所述写回指针和读回指针指示是否有空间写回密文,是否有密文待取出。

作为本发明的一种实施方式,所述OpenSSL拓展实现SM4硬件加密引擎;基于引擎机制,使得OpenSSL能够透明调用本发明的硬件加密方法。SM4引擎加载方式,包括动态和静态两种。

进一步地,本发明系统的处理方法如下,包括以下步骤:

步骤1:在主机端安装Xilinx提供的XDMA(DMA/Bridge Subsystem for PCIExpress)驱动,并使用setpci命令将MaxReadReq设为当下支持的最大值1024B。

步骤2:主机创建一个发送线程和两个接收线程。

步骤2.1:发送线程中,主机轮流向DDR4_0和DDR4_2发送数据;发送前,发送线程比较DDR4_0或DDR4_2的读写指针,判断是否有空间存放新数据,发送后更新相应写指针。

步骤2.2:接收线程有两个,一个线程通过c2h0通道读取DDR4_1中数据,一个线程通过c2h1通道读取DDR4_3中数据,不同通道保证了数据之间的相互独立;接收线程通过比较读回和写回指针判断是否有新加密结果可以读取,读取后更新读回指针。

步骤2.3:如图2所示,主机发数据、FPGA处理、主机取数据形成三级流水线。

步骤3:主机端通过驱动以SGDMA方式实现数据的收发。

步骤4:FPGA端,主机发送的明文数据首先经过数据收发模块,数据收发模块基于XDMA IP实现,DMA接口选择AXI地址映射模式,时钟频率为250MHz,数据宽度为512bit;XDMA通过AXI4接口将主机发送的数据传输到连接模块;连接模块基于AXI Interconnect IP实现,它根据地址将数据转发到DDR4_0或DDR4_2;当主机读取密文数据时,数据从DDR4_1或DDR4_3中取出,经过连接模块传送到数据收发模块,最后以SGDMA模式发送到主机端;此过程中,连接模块还负责实现仲裁、跨时钟域等功能。

步骤5:如图3所示,FPGA端有两组SM4加密引擎;每组由控制模块、DDR4模块、FIFO缓存模块、SM4模块组成;具体的,每组引擎包括两个DDR4、四个寄存器、两个FIFO以及四个SM4核。

步骤5.1:控制模块根据写、读、写回、读回指针实现逻辑控制,指针基于32位寄存器实现,寄存器中保存DDR4地址。

步骤5.2:当读写指针不相等时,创建读请求,采用突发读方式读取出DDR4中的数据并暂存到明文FIFO中,读结束后更新读指针。

步骤5.3:当明文FIFO不为空时,取出512bit数据,即四个明文数据,分别发送到四个SM4核中进行加密。

步骤5.4:单个SM4核由加密模块和密钥扩展模块组成,两个模块的输入时钟信号为300MHz;加密模块的输入信号还包括轮密钥、128bit明文以及明文有效信号,输出为128bit密文和密文有效信号;密钥扩展模块的输入信号有128bit密钥和密钥有效信号,输出为扩展后的轮密钥;加密模块和密钥扩展模块都采用三十二级流水线架构,加密模块在不断流的情况下每个周期输出一个加密结果,密钥扩展模块的每级流水每个周期完成一个32bit轮密钥的生成;密钥扩展模块需要比加密模块提前一个周期启动,以实现明文有效后无需等待轮密钥,轮密钥产生后就立刻被使用;在300MHz时钟频率下,单个SM4核的吞吐率为35.76Gbps,根据WNS可计算出其最高吞吐率为56.39Gbps。

步骤5.5:加密结果被暂存在密文FIFO中,当密文FIFO中的数据量达到一次突发写的上限或一段时间内无数据被写入时,创建写请求,以突发写方式将密文写回DDR4,写结束后更新写回指针。

步骤6:主机创建并加载SM4硬件加密引擎后,通过OpenSSL透明地调用硬件进行SM4加密。

步骤6.1:首先完成算法结构体定义,在evp_cipher_st结构体中完成nid标识、分组长度、密钥长度、初始化函数、加解密函数等相关设置。

步骤6.2:动态加载模式下,使用IMPLEMENT_DYNAMIC_BIND_FN完成引擎注册,然后将代码编译为动态链接库,通过-engine命令实现调用。

步骤6.3:静态加载模式下,使用ENGINE_add实现注册,通过ENGINE_by_id获取引擎指针以此实现SM4硬件加密算法的调用。

在本说明书的描述中,参考术语“一个实施例”、“示例”、“具体示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

以上显示和描述了本发明的基本原理、主要特征和本发明的优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是说明本发明的原理,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明范围内。