一种新型高速DDR发送电路

文献发布时间:2023-06-19 10:44:55

技术领域

本发明涉及电路设计领域,具体涉及一种新型高速DDR发送电路。

背景技术

DDR输出接口驱动电路通常由cmos管作为输出驱动电阻,或cmos管加电阻组合而成一个输出驱动电阻,受限于电气规范中电压的规定,现有DDR4、DDR5等接口发送电路通常仍然使用速度较慢的高压器件来做主驱动电路及前驱动电路,如DDR4电源电压规定为1.2V,主驱动单元及前驱动电路必须选用耐受1.2V以上的高压cmos管(IO device),随着工艺的提升,其低压的核心器件(core device)速度越来越快,但耐受电压越来越低,难以进一步提高工作速度。

发明内容

针对上述技术问题,本发明提供了一种新型高速DDR发送电路。

一种新型高速DDR发送电路,包括两个PMOS管PM1、PM2以及两个与PMOS管并联的NMOS管NM1、NM2;其中PM1的源极接高电压VDDQ,漏极与PM2的源极相连,PM2的漏极则与一电阻相连,电阻的另一端与输出垫片相连;PM1的栅极和控制线netp相连,netp通过反向器INV1与数据输入DIN相连,INV1与netp之间设有电容C;INV1的工作电压为低电压VDD,电容C和netp能为PM1的栅极提供一个电压VDDL(VDDL=VDDQ-VDD),以对PM1进行保护;

NM1的源极接地,漏极与NM2的源极相连,NM2的漏极同样与所述电阻相连;NM1的栅极通过反向器INV2与数据输入DIN相连。

优选的,PM2、NM2作为调节阻抗的静态开关,工作状态下为常开。

优选的,netp包括并联设置的两个节点net1和net2;net1和net2的一端分别与电容C1和电容C2连接,另一端分别通过CLKN与输出垫片相连,且两个CLKN与输出垫片之间连接有一个接地的稳压电容C3;电容C1和net1之间通过CLK接高电压VDDQ,电容C1的另一端分别通过CLK接低电压VDD,通过CLKN接地;电容C2和net2之间通过CLK接地,电容C2的另一端分别通过CLK接低电压VDD,通过CLKN接高电压VDDQ。

优选的,电容C的旁路设有两个并联设置的高压器件传输门,高压信号EL0H控制其中一个传输门把电压VDDL传至netp,高压信号EL1H控制另一个传输门把电压VDDQ传至netp,使INV1能通过电容C驱动netp在VDDQ和VDDL之间快速翻转。

优选的,所述高压信号EL0H来自于DIN与DIN_E异或后和DIN_EB的相与后再和OEB相或,再经过电平转换为高后的信号。

优选的,所述高压信号EL1H来自于DIN与DIN_E异或后和DIN_E的相与,再经过电平转换为高后的信号。

本发明的有益效果是:采用速度较快的低压器件做主驱动电路及前驱动电路,同时利用时钟信号和开关电容在不额外大幅增加功耗的情况下制造一个电压来保证低压器件的安全性,有效提高了电路的工作速度。

附图说明

下面结合附图对本发明作进一步的说明。

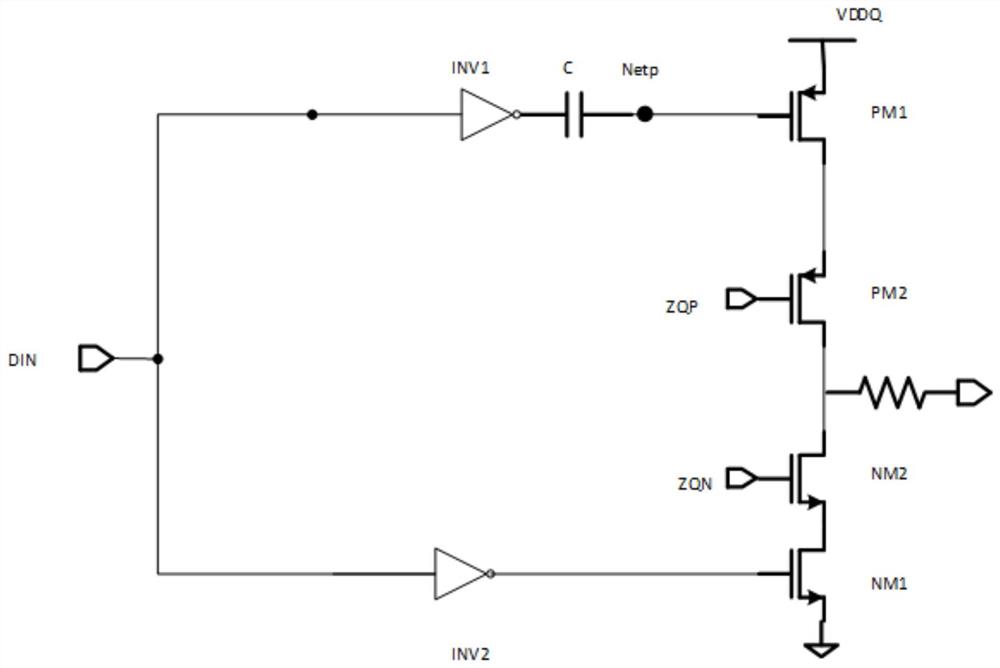

图1为本发明实施例的整体电路图;

图2为本发明实施例中netp的电路图;

图3为本发明实施例中电容C的旁路电路图。

具体实施方式

下面将对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例,基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

本发明提供了一种新型高速DDR发送电路,其整体电路结构如图1所示,主要包括两个PMOS管PM1、PM2以及两个与PMOS管并联的NMOS管NM1、NM2,其中,PM2、NM2作为调节阻抗的静态开关,工作状态下为常开,不再影响工作速度;PM1、NM1为增加的低压器件,在数据控制下高速开关。

PM1的源极接高电压VDDQ,漏极与PM2的源极相连,PM2的漏极则与电阻相连,电阻的另一端与输出垫片相连。PM1的栅极和控制线netp相连,netp通过反向器INV1与数据输入DIN相连,INV1与netp之间设有电容C。INV1的工作电压为低电压VDD,电容C和netp能为PM1的栅极提供一个电压VDDL(VDDL=VDDQ-VDD),以对PM1进行保护。例如DDR4时VDDQ为1.2V,而在14nm工艺下,此PM1栅极到源极的耐受电压差(Vgs)为0.8V,因此前级驱动电路需要为PM1的栅极产生信号幅度为1.2V到0.4V(1.2V-0.8V)的信号。

当电容C左端的INV1输出为VDD时,右端netp的初始电压为VDDQ。下一数据INV1输出为0时,在电容C的电容电荷保持不变的约束下,则netp的电压突变为VDDQ-VDD。反之INV1输出为0时,netp的初始电压为VDDQ-VDD,下一数据INV1输出为VDD时,netp的电压突变为VDDQ。

NM1的源极接地,漏极与NM2的源极相连,NM2的漏极同样与电阻相连。NM1的栅极则通过反向器INV2与数据输入DIN相连。

如图2所示,netp包括并联设置的两个节点net1和net2。net1和net2的左端分别与电容C1和电容C2连接,右端则分别通过CLKN与输出垫片相连,且两个CLKN与输出垫片之间连接有一个接地的稳压电容C3。电容C1和net1之间通过CLK接高电压VDDQ,电容C1的左端分别通过CLK接低电压VDD,通过CLKN接地。电容C2和net2之间通过CLK接地,电容C2的左端分别通过CLK接低电压VDD,通过CLKN接高电压VDDQ。其中,CLKN为CLK的反相信号,当CLK或CLKN为高电平时开关导通,反之开关断开。

当CLK为高电平时,CLKN为低,此时电容C1的右端接通VDDQ,左端接通VDD,C1的电荷为(VDDQ-VDD)*C1;当CLK变为低电平时,CLKN为高,此时电容C1的左端接地(0V),C1在没有电源充电的情况下,电荷量仍然保持为(VDDQ-VDD)*C1,即右端net1的电压变为VDDQ-VDD。在稳压电容C3对电容C1的电荷分享作用下,输出的VDDL电压可从VDDQ逐步降低,并在几个CLK周期后稳定在VDDQ-VDD。

同理,当CLK为高电平时,CLKN为低,此时电容C2的右端接地,左端接通VDD,C2的电荷为VDD*C2;当CLK变为低电平时,CLKN为高,此时电容C2的左端接通VDDQ,C2在没有电源充电的情况下,电荷量仍然保持为VDD*C2,即右端net2的电压变为VDDQ-VDD。在稳压电容C3对电容C2的电荷分享作用下,输出的VDDL电压可从0V逐步升高,并在几个CLK周期后稳定在VDDQ-VDD。

因此,C1支路与C2支路并联可以使VDDL在第一个时钟周期即可达到0.5*VDDQ,避免VDDL产生过高电压的同时,还能大幅提高其稳定速度。

如图3所示,电容C的旁路设有两个并联设置的高压器件传输门,高压信号EL0H控制其中一个传输门把电压VDDL传至netp,高压信号EL1H控制另一个传输门把电压VDDQ传至netp,使INV1能通过电容C驱动netp在VDDQ和VDDL之间快速翻转。

高压信号EL1H来自于DIN与DIN_E(DIN前一笔数据)异或后和DIN_E的相与,再经过电平转换为高后的信号。即:当连续两笔数据为1时,EL1H随着第一笔1变为高电平,进而打开其控制的高压器件传输门,netp电压变为VDDQ。若第三笔数据(DIN_L)没有继续保持1(即DIN_E,DIN,DIN_L为110),则EL1H随着第一笔1的结束而结束,进而关闭其对应的传输门。

同理,高压信号EL0H来自于DIN与DIN_E异或后和DIN_EB(DIN_E的反相信号)的相与后再和OEB(OE的反相信号)相或,再经过电平转换为高后的信号。即:当连续两笔数据为0或OE为0时,EL0H随着第一笔0变为高电平,进而打开其控制的高压器件传输门,netp电压变为VDDL。若第三笔数据(EIN_L)没有继续保持0(即DIN_E,DIN,DIN_L为001),则EL0H随着第一笔0的结束而结束,进而关闭其对应的传输门。

EL1H、EL0H所利用的电平转换器通常速度较慢,因此采用上述逻辑可使其早于INV1对电容C右端充电。表现为INV1发送的数据为110时,电容C右端恰好在第一笔1的后半期开始充电至VDDQ,第二笔1的前半期结束充电。001时同理充电至VDDL。当发送的数据为0101时,INV1通过电容C驱动netp在VDDQ和VDDL之间快速翻转。各部分电路结合起作用,即可实现数据快速翻转和及时充电防止电平漂移的功能。

本发明通过采用速度较快的低压器件做主驱动电路及前驱动电路,同时利用时钟信号和开关电容在不额外大幅增加功耗的情况下制造一个电压来保证低压器件的安全性,有效提高了电路的工作速度。

对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。

- 一种新型高速DDR发送电路

- 一种DDR发送电路