芯片封装结构的制备方法及芯片封装结构

文献发布时间:2024-01-17 01:26:37

技术领域

本申请涉及芯片技术领域,特别涉及一种芯片封装结构的制备方法及芯片封装结构。

背景技术

在芯片技术领域中,晶圆级封装(Wafer Level Packaging,WLP)中硅面直接与绝缘材料接触,主要还是避免硅与芯片导电垫片相连的金属线路接触造成短路或者漏电,这样设计出的芯片本身的散热能力有限,芯片工作时产生的热量难以散发出去。因此,如何提供一种具有良好散热功能的芯片封装结构的制备方法及芯片封装结构是目前亟待解决的技术问题。

发明内容

本申请提供一种具有良好散热功能的芯片封装结构的制备方法及芯片封装结构,以解决现有技术中芯片工作时产生的热量难以散发的技术问题。

为解决上述问题,本申请提供一种芯片封装结构的制备方法,包括:

提供一芯片基体,所述芯片基体包括基材,所述基材具有相对设置的第一表面和第二表面,所述第一表面设置有芯片主体;

在所述第二表面沉积第一金属层,对所述第一金属层进行蚀刻形成散热主体,所述散热主体正对所述芯片主体;

在所述第二表面和所述散热主体远离所述基材的一侧设置绝缘层,对所述绝缘层对应所述散热主体的位置进行光刻处理形成开孔,所述散热主体暴露于所述开孔;以及

在所述绝缘层远离所述基材的一侧设置第二金属层,对所述第二金属层进行蚀刻形成电连接部和散热部,所述散热部通过所述开孔与所述散热主体导热连接,所述电连接部与所述芯片主体电连接。

其中,所述第一表面还设置有电连接主体,所述芯片主体和所述电连接主体电连接,所述在所述第二表面设置第一金属层,对所述第一金属层进行蚀刻形成散热主体的步骤之后,还包括:

在电连接主体区域进行穿透硅通孔(Through Silicon Via,TSV)处理并形成贯穿所述基材的贯穿孔,所述电连接主体暴露于所述贯穿孔。

其中,所述绝缘层覆盖所述散热主体、所述第二表面和所述贯穿孔的侧壁,所述绝缘层暴露所述电连接主体朝向所述贯穿孔的表面。

其中,所述第二金属层的所述电连接部覆盖所述贯穿孔内的所述绝缘层后与所述电连接主体电连接。

其中,所述第一表面还设置有电连接主体,所述芯片主体和所述电连接主体电连接,所述在所述第二表面和所述散热主体远离所述基材的一侧设置绝缘层,在所述散热主体对应位置处对所述绝缘层进行光刻处理形成开孔,所述散热主体暴露于所述开孔的步骤之后,还包括:

在所述电连接主体位置处设置贯穿所述绝缘层和所述基材的贯穿孔,所述电连接主体暴露于所述贯穿孔。

其中,所述第二金属层的所述电连接部覆盖所述绝缘层和所述基材朝向所述贯穿孔的侧壁并与所述电连接主体电连接。

其中,所述第二金属层的所述电连接部填充所述贯穿孔并与所述电连接主体电连接。

其中,所述芯片封装结构的制备方法还包括:在所述第二金属层远离所述基材的一侧设置保护层,对所述保护层进行蚀刻形成导热连接孔和导电连接孔,所述导热连接孔与所述散热部相对应,所述导电连接孔与所述电连接部相对应。

其中,所述芯片封装结构的制备方法还包括:设置导热连接体和导电连接体,所述导热连接体通过所述导热连接孔与所述散热部导热连接,所述导电连接体与所述电连接部电连接。

本申请还提供一种芯片封装结构,所述芯片封装结构由如前所述制备方法制备。

本申请实施例的有益效果是:本申请所提供的芯片封装结构的制备方法包括:提供一芯片基体,所述芯片基体包括基材,所述基材具有相对设置的第一表面和第二表面,所述第一表面设置有芯片主体;在所述第二表面沉积第一金属层,对所述第一金属层进行蚀刻形成散热主体,所述散热主体正对所述芯片主体;在所述第二表面和所述散热主体远离所述基材的一侧设置绝缘层,对所述绝缘层对应所述散热主体的位置进行光刻处理形成开孔,所述散热主体暴露于所述开孔;以及在所述绝缘层远离所述基材的一侧设置第二金属层,对所述第二金属层进行蚀刻形成电连接部和散热部,所述散热部通过所述开孔与所述散热主体导热连接,所述电连接部与所述芯片主体电连接。因此,通过在所述基材和所述绝缘层之间增设具有所述散热主体的所述第一金属层,在所述第二金属层中设置所述散热部,通过所述散热主体和所述散热部之间导热连接,从而将所述芯片主体产生的热量经过所述基材、所述散热主体和所述散热部向外散发,进而解决了现有技术中芯片工作时产生的热量难以散发的技术问题,提供了一种具有良好散热功能的芯片封装结构的制备方法及芯片封装结构。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图,其中:

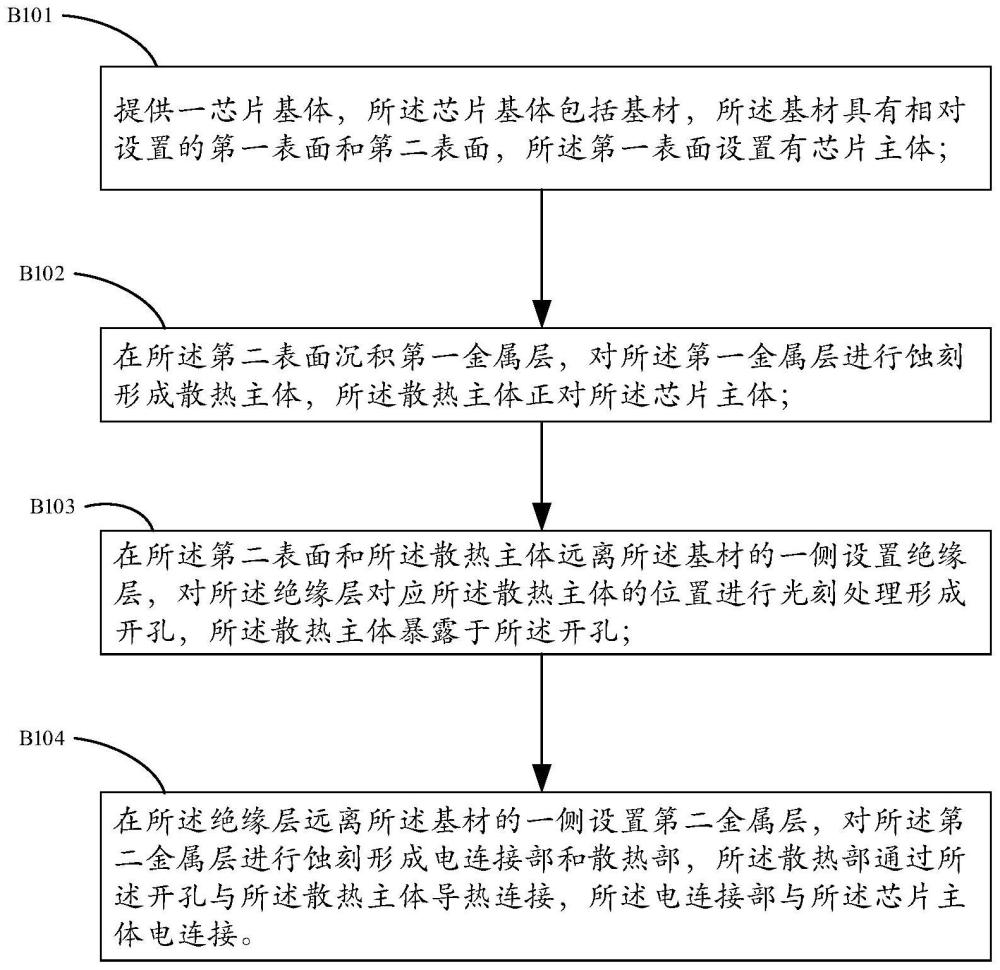

图1是本申请所提供的芯片封装结构的制备方法的第一种实施方式的流程示意图;

图2是本申请所提供的芯片封装结构的制备方法的第一种实施方式的结构示意图;

图3是本申请所提供的芯片封装结构的制备方法的第二种实施方式的流程示意图;

图4是本申请所提供的芯片封装结构的制备方法的第二种实施方式的结构示意图;

图5是本申请所提供的芯片封装结构的制备方法的第三种实施方式的结构示意图;

图6是本申请所提供的芯片封装结构的制备方法的第四种实施方式的流程示意图;

图7是本申请所提供的芯片封装结构的制备方法的第四种实施方式的结构示意图;

图8是本申请所提供的芯片封装结构的制备方法的第五种实施方式的结构示意图;

图9是本申请所提供的芯片封装结构的第一种实施方式的结构示意图;

图10是本申请所提供的芯片封装结构的第二种实施方式的结构示意图;

图11是本申请所提供的芯片封装结构的第三种实施方式的结构示意图;

图12是本申请所提供的芯片封装结构的第四种实施方式的结构示意图;

图13是本申请所提供的芯片封装结构的第五种实施方式的结构示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。可以理解的是,此处所描述的具体实施例仅用于解释本申请,而非对本申请的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本申请相关的部分而非全部结构。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

请参阅图1,图1是本申请所提供的芯片封装结构的制备方法的第一种实施方式的流程示意图。本申请提供一种芯片封装结构的制备方法。制备方法包括以下步骤:

B101,提供一芯片基体10,芯片基体10包括基材11,基材11具有相对设置的第一表面11a和第二表面11b,第一表面11a设置有芯片主体12。

请参阅图2,图2是本申请所提供的芯片封装结构的制备方法的第一种实施方式的结构示意图。芯片基体10包括若干芯片组件单元10a。在每一芯片组件单元10a中,第一表面11a设置有芯片主体12和电连接主体13。

在一些实施例中,芯片基体10可以硅基片。芯片主体12可以为运算处理类芯片,也可以为传感器类芯片,还可以为存储介质类芯片。在本申请中,对芯片主体12为LCoS芯片。电连接主体13可以为铜、金、或由其他具有导电性的材质制成。

在一些实施例中,基材11的第一表面11a具有第一区域和第二区域。第一区域用于设置芯片主体12。第二区域用于设置电连接主体13。第一区域和第二区域可以为第一表面11a的部分区域内的凹陷部。芯片主体12和电连接主体13可以设置于凹陷部内。芯片主体12和电连接主体13朝向凹陷部的表面与凹陷部接触,芯片主体12和电连接主体13背离凹陷部的表面与第一表面11a平齐。

B102、在第二表面11b沉积第一金属层20,对第一金属层20进行蚀刻形成散热主体21。

散热主体21与芯片组件单元10a相对应。在一些实施例中,散热主体21在第一表面11a的投影与电连接主体13在第一表面11a的投影错开设置,以利于后续制程中的开设贯穿基材11的通孔,同时避免后续制程中导线线路距离过近容易引起的短路问题。

第一金属层20为具有良好导热性能的金属。在一些实施例中,第一金属层20可以为钼、铜、金、铝等金属中的一种形成的金属层。在其他实施例中,第一金属层20还可以为钼、铜、金、铝等金属中的至少两种形成的合金层,也可以为钼、铜、铝等金属形成的至少两种金属层的复合层。

在一些实施例中,可以通过沉积形成第一金属层20,然后,再通过对第一金属层20进行蚀刻形成散热主体21。

B103、在第二表面11b和散热主体21远离基材11的一侧设置绝缘层30,对绝缘层30对应的散热主体21的位置进行光刻处理形成开孔30a,散热主体21暴露于开孔30a。

绝缘层30可以由氧化硅、氮化硅、氮氧化硅、环氧树脂等材料制成。

在一些实施例中,可以通过沉积形成绝缘层30,然后,再通过对绝缘层30进行蚀刻形成开孔30a,从而暴露散热主体21。

B104、在绝缘层30远离基材11的一侧设置第二金属层40,对第二金属层40进行蚀刻形成电连接部41和散热部42,散热部42通过开孔30a与散热主体21导热连接,电连接部41与芯片主体12电连接。

第二金属层40设置于绝缘层30远离基材11的一侧,第二金属层40经过蚀刻形成电连接部41和散热部42。散热部42通过开孔30a与散热主体21导热连接。在本实施方式中,散热部42形成于开孔30a上。所述电连接部41与所述芯片主体12电连接。

需要说明的是,所述电连接主体12电连接于所述芯片主体13和所述电连接部41之间。电连接部41与电连接主体13的电连接方式包括但不限于外接线路电连接,例如,金线连接,或者对30绝缘层和基材11进行穿孔电连接。

第二金属层40为具有良好导电和导热性能的金属。在一些实施例中,第二金属层40可以为钼、铜、金、铝等金属中的一种形成的金属层。在其他实施例中,第二金属层40还可以为钼、铜、金、铝等金属中的至少两种形成的合金层,也可以为钼、铜、铝等金属形成的至少两种金属层的复合层。

在一些实施例中,可以通过沉积形成第二金属层40,然后,再通过对第二金属层40进行蚀刻形成电连接部41和散热部42。

在一些实施例中,在形成第二金属层40和进行蚀刻形成电连接部41和散热部42之间,还可以包括对第二金属层40的表面进行化学机械抛光(Chemical MechanicalPolishing,CMP)处理。

请参阅图3和4,图3是本申请所提供的芯片封装结构的制备方法的第二种实施方式的流程示意图,图4是本申请所提供的芯片封装结构的制备方法的第二种实施方式的结构示意图。第二实施例与第一实施例的不同之处在于:在步骤B101之后,制备方法还包括:步骤B201,在第一表面11a设置载板14。载板14用于承载芯片基体10。载板14覆盖第一表面11a、芯片主体12和电连接主体13。

具体的,载板14可以为玻璃载板14,为芯片基体10提供承载力。芯片基体10可拆卸地设置于载板14上。

在步骤B101、步骤B102和步骤B201其中任一步骤中,对第二表面11b进行研磨处理,以使得将基材11研磨到合适的厚度。

在对第二表面11b进行研磨处理后,还可以包括对第二表面11b进行腐蚀处理,以用于提高第二表面11b的粗糙度,从而增加后续步骤中的第一金属层20与第二表面11b的结合力。

在步骤B102之后,制备方法还可以包括:步骤B202,在基材11对应电连接主体13的区域进行穿透硅通孔(Through Silicon Via,TSV)处理形成贯穿基材11的贯穿孔11c,电连接主体13暴露于贯穿孔11c。

在步骤B103中,绝缘层30覆盖散热主体21、第二表面11b和贯穿孔11c的侧壁,绝缘层30暴露电连接主体13朝向贯穿孔11c的表面。

具体的,可以通过沉积形成覆盖散热主体21、第二表面11b和贯穿孔11c的侧壁的绝缘层30,再通过对绝缘层30蚀刻形成开孔30a以暴露电连接主体13朝向贯穿孔11c的表面。蚀刻的方式可以采用化学蚀刻工艺、光刻工艺、等离子轰击蚀刻等。

在步骤B104中,第二金属层40的电连接部41覆盖贯穿孔11c内的绝缘层30后与电连接主体13电连接。

在本实施例中,在设置完散热主体21后,先在基材11上形成贯穿孔11c,再设置绝缘层30和第二金属层40。

第二实施例与第一实施例的不同之处还在于:在步骤B104之后,制备方法还可以包括:步骤B203,在第二金属层40远离基材11的一侧设置保护层50,对保护层50进行蚀刻形成导热连接孔50a和导电连接孔50b,导热连接孔50a的位置与散热部42相对应,导电连接孔50b的位置与电连接部41相对应。

在一些实施例中,可以先通过沉积形成保护层50,然后,再通过对保护层50进行蚀刻形成导热连接孔50a和导电连接孔50b。

第二实施例与第一实施例的不同之处还在于:在步骤B203之后,制备方法还可以包括:B204,设置导热连接体61和导电连接体61,导热连接体61通过导热连接孔50a与散热部42导热连接,导电连接体61与电连接部41电连接。

具体的,导热连接体61和导电连接体61为相同材料或不同材料。在一些实施例中,导热连接体和导电连接体选自锡球和导电胶中的一种或两种。例如,导热连接体61和导电连接体61可以均为锡球,也可以均为导电胶,或者,还可以导热连接体61为锡球,导电连接体61为导电胶。

第二实施例与第一实施例的不同之处还在于:在步骤B204之后,制备方法还可以包括:

B205,去除载板14,在基材11的第一表面11a设置切割膜70,切割膜70覆盖第一表面11a、芯片主体12和电连接主体13;

B206、以芯片组件单元10a为单位切割芯片基体10;

B207、去除切割膜70。

在一些实施例中,切割膜70可以紫外切割膜。用于切割芯片基体10的切割设备71可以为划片机或激光切割机等。

请参阅图5,图5是本申请所提供的芯片封装结构的制备方法的第三种实施方式的结构示意图。图5所示的制备方法与图4所示的制备方法的不同之处在于:从步骤104到步骤207,第二金属层40的电连接部41填充贯穿孔11c并与电连接主体13电连接。具体的,第二金属层40的电连接部41可以完全填充贯穿孔11c并与电连接主体13电连接,或者,第二金属层40的电连接部41也可以部分填充贯穿孔11c并与电连接主体13电连接。

请参阅图6和7,图6是本申请所提供的芯片封装结构的制备方法的第四种实施方式的流程示意图,图7是本申请所提供的芯片封装结构的制备方法的第四种实施方式的结构示意图。第四实施例和第二实施例的不同之处在于:不包括步骤B201,而是在步骤B103之后,还包括:B208、在电连接主体13位置处设置贯穿绝缘层30和基材11的贯穿孔11c,电连接主体13暴露于贯穿孔11c。

具体的,可以通过蚀刻在绝缘层30和基材11上形成贯穿孔11c。蚀刻绝缘层30和基材11的蚀刻方法可以相同也可以不同。

在步骤B104中,第二金属层40的电连接部41覆盖贯穿孔11c内的绝缘层30并与电连接主体13电连接。

在本实施例中,在设置完散热主体21后,先形成绝缘层30,再在基材11和绝缘层30上形成贯穿孔11c,然后,再设置第二金属层40。

请参阅图8,图8是本申请所提供的芯片封装结构的制备方法的第五种实施方式的结构示意图。图8所示的制备方法与图7所示的制备方法的不同之处在于:从步骤104到步骤107,第二金属层40的电连接部41填充贯穿孔11c并与电连接主体13电连接。具体的,第二金属层40的电连接部41可以完全填充贯穿孔11c并与电连接主体13电连接,或者,第二金属层40的电连接部41也可以部分填充贯穿孔11c并与电连接主体13电连接。

需要说明的是,在本申请中所利用的沉积技术,包括但不限于溅射技术、沉积技术等。

请参阅图9,图9是本申请所提供的芯片封装结构的第一种实施方式的结构示意图。本申请还提供一种芯片封装结构100。芯片封装结构100包括芯片基体10、第一金属层20、绝缘层30和第二金属层40。

芯片基体10包括基材11。基材11具有相对设置的第一表面11a和第二表面11b。第一表面11a设置有芯片主体12和电连接主体13。芯片主体12和电连接主体13电连接。

具体的,基材11可以硅基片。芯片主体12和电连接主体13均设置于基材11的第一表面11a。芯片主体12可以为运算处理类芯片,也可以为传感器类芯片,还可以为存储介质类芯片。在本申请中,芯片主体12为LCoS芯片。电连接主体13可以为铜、金、或由其他具有导电性的材质制成。

在一些实施例中,基材11的第一表面11a具有第一区域和第二区域。第一区域用于设置芯片主体12。第二区域用于设置电连接主体13。第一区域和第二区域可以为第一表面11a的部分区域内的凹陷部。芯片主体12和电连接主体13可以设置于凹陷部内。芯片主体12和电连接主体13朝向凹陷部的表面与凹陷部接触,芯片主体12和电连接主体13背离凹陷部的表面与第一表面11a平齐。

第一金属层20设置于芯片基体10的第二表面11b。第一金属层20具有散热主体21。散热主体21在第一表面11a的投影与电连接主体13在第一表面11a的投影错开设置。

具体的,第一金属层20为具有良好导热性能的金属。在一些实施例中,第一金属层20可以为钼、铜、金、铝等金属中的一种形成的金属层。在其他实施例中,第一金属层20还可以为钼、铜、金、铝等金属中的至少两种形成的合金层,也可以为钼、铜、铝等金属形成的至少两种金属层的复合层。

绝缘层30设置于第一金属层20远离基材11的一侧。绝缘层30具有开孔30a。散热主体21暴露于开孔30a。

绝缘层30可以由氧化硅、氮化硅、氮氧化硅、环氧树脂等材料制成。

第二金属层40设置于绝缘层30远离基材11的一侧。第二金属层40包括电连接部41和散热部42。散热部42通过开孔30a与散热主体21导热连接。在本实施方式中,散热部42形成于开孔30a上。电连接部41与电连接主体13电连接。

需要说明的是,电连接部41与电连接主体13的电连接方式包括但不限于外接线路电连接,例如,金线连接,或者对30绝缘层和基材11进行穿孔电连接。

具体的,第二金属层40为具有良好导电和导热性能的金属。在一些实施例中,第二金属层40可以为钼、铜、金、铝等金属中的一种形成的金属层。在其他实施例中,第二金属层40还可以为钼、铜、金、铝等金属中的至少两种形成的合金层,也可以为钼、铜、铝等金属形成的至少两种金属层的复合层。

请参阅图10,图10是本申请所提供的芯片封装结构的第二种实施方式的结构示意图。在本实施例中,基材11上具有贯穿孔11c。贯穿孔11c贯穿基材11的第一表面11a和第二表面11b、并暴露电连接主体13。绝缘层30覆盖第一金属层20、第二表面11b和贯穿孔11c的侧壁,绝缘层30暴露电连接主体13朝向贯穿孔11c的表面。

请参阅图11,图11是本申请所提供的芯片封装结构的第三种实施方式的结构示意图。在本实施例中,第二金属层40的电连接部41填充贯穿孔11c并与电连接主体13电连接。具体的,第二金属层40的电连接部41可以完全填充贯穿孔11c并与电连接主体13电连接,或者,第二金属层40的电连接部41也可以部分填充贯穿孔11c并与电连接主体13电连接。

请参阅图12,图12是本申请所提供的芯片封装结构的第四种实施方式的结构示意图。在本实施例中,基材11和绝缘层30上具有贯穿孔11c。贯穿孔11c贯穿基材11和绝缘层30、并暴露电连接主体13。第二金属层40的电连接部41覆盖贯穿孔11c内的绝缘层30并与电连接主体13电连接。

请参阅图13,图13是本申请所提供的芯片封装结构的第五种实施方式的结构示意图。在本实施例中,第二金属层40的电连接部41填充贯穿孔11c并与电连接主体13电连接。具体的,第二金属层40的电连接部41可以完全填充贯穿孔11c并与电连接主体13电连接,或者,第二金属层40的电连接部41也可以部分填充贯穿孔11c并与电连接主体13电连接。

另外,芯片封装结构100还包括保护层50。保护层50设置于第二金属层40远离基材11的一侧。保护层50具有导热连接孔50a和导电连接孔50b。导热连接孔50a的位置与散热部42相对应。导电连接孔50b的位置与电连接部41相对应。

芯片封装结构100还包括导热连接体61。导热连接体61通过导热连接孔50a与散热部42导热连接。芯片封装结构100还包括导电连接体61,导电连接体61与电连接部41电连接。

具体的,导热连接体61和导电连接体61为相同材料或不同材料。在一些实施例中,导热连接体和导电连接体选自锡球和导电胶中的一种或两种。例如,导热连接体61和导电连接体61可以均为锡球,也可以均为导电胶,或者,还可以导热连接体61为锡球,导电连接体61为导电胶。

本申请提供了一种芯片封装结构的制备方法及芯片封装结构,芯片封装结构的制备方法包括:提供一芯片基体,芯片基体包括基材,基材具有相对设置的第一表面和第二表面,第一表面设置有芯片主体;在基材的第二表面设置第一金属层,对第一金属层进行蚀刻形成若干散热主体;在第二表面和散热主体远离基材的一侧设置绝缘层,绝缘层具有开孔,散热主体暴露于开孔;以及在绝缘层远离基材的一侧设置第二金属层,对第二金属层进行蚀刻形成电连接部和散热部,散热部通过开孔与散热主体导热连接,电连接部与芯片主体电连接。因此,通过在基材和绝缘层之间增设具有散热主体的第一金属层,在第二金属层中设置散热部,通过散热主体和散热部之间导热连接,从而将芯片主体产生的热量经过基材、散热主体和散热部向外散发,进而解决了现有技术中芯片工作时产生的热量难以散发的技术问题,提供了一种具有良好散热功能的芯片封装结构的制备方法及芯片封装结构。

以上仅为本申请的实施方式,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所做的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。