PCIE插卡式无人机干扰信号发生器、干扰方法及相关设备

文献发布时间:2023-06-19 11:49:09

技术领域

本申请涉及无人机技术领域,尤其涉及一种PCIE插卡式无人机干扰信号发生器、干扰方法及相关设备。

背景技术

目前无人机的种类和数量越来越多,“黑飞”事件屡禁不止,严重的危害了人民群众的生命财产安全,扰乱了社会治安。对无人机的反制已经成为政府相关部门,甚至重要私人场所必须部署的安防措施。现阶段无人机干扰设备主要采用的是遥控信号压制的办法进行干扰,通过发送大功率的固定频率干扰信号或扫频干扰信号,将无人机的遥控信号压制住,使其无法和地面遥控器进行正常通信,从而达到无人机迫降或驱离的目的。这种干扰信号一般由压控振荡器生成,干扰设备通过调整控制电压生成期望的干扰信号。

现有的无人机干扰设备产生的无人机干扰信号存在着信号频带窄,响应速度慢,频率单一的缺点。这种干扰信号针对市场上早期推出的无人机有比较好的反制效果,随着无人机的更新换代加快,防干扰无人机开始出现,之前的干扰信号已经无法有效的起到反制作用。这种防干扰无人机采用跳频遥控信号进行通信,这种抗干扰遥控信号具有频带宽,可达100Mhz或150Mhz,跳频速度快等特点,常规的干扰设备生成的干扰信号没有办法在这么宽的频带内做到完全压制,快速响应,所以干扰效果非常小。

发明内容

有鉴于此,本申请实施例提供一种PCIE插卡式无人机干扰信号发生器、干扰方法及相关设备,至少部分解决现有技术中存在的问题。

第一方面,本申请提供了一种PCIE插卡式无人机干扰信号发生器,所述发生器包括:

PCIE接口数字电路组件,所述PCIE接口数字电路组件用于接收PCIE数据并通过内部PCIE逻辑转换电路生成波形数据;

数模转换组件,所述数模转换组件的输入端与所述PCIE接口数字电路组件的输出端连接,用于接收所述PCIE接口数字电路组件生成的波形数据并产生干扰基带信号;

宽频调制组件,所述宽频调制组件的输入端与所述数模转换组件的输出端连接,用于将所述干扰基带信号调频生成干扰信号。

根据本申请实施例的一种具体实现方式,所述PCIE接口数字电路组件为FPGA组件或DSP组件。

根据本申请实施例的一种具体实现方式,所述PCIE接口数字电路组件的输入端与PCIE总线连接,所述PCIE总线接口为pcieX4,带宽为20Gbps。

根据本申请实施例的一种具体实现方式,所述数模转换组件为200M带宽。

根据本申请实施例的一种具体实现方式,所述干扰信号为60Mhz-6Ghz频带的任一波形信号。

根据本申请实施例的一种具体实现方式,所述所需的波形数据包括定频信号、扫频信号和梳妆波信号中的一种或几种。

根据本申请实施例的一种具体实现方式,所述干扰器还包括无人机干扰信号发射组件,用于将宽频调制组件产生的干扰信号进行发射。

根据本申请实施例的一种具体实现方式,所述无人机干扰信号发射组件为平面天线或喇叭天线。

第二方面,本申请实施例提供了一种电子设备,所述电子设备包括前述第一方面任一实施例所述的PCIE插卡式无人机干扰信号发生器。

第三方面,本申请实施例提供了一种PCIE插卡式无人机干扰信号发生器的干扰方法,所述方法包括:

所述PCIE插卡式无人机干扰信号发生器接收PCIE数据并通过内部PCIE逻辑转换电路生成波形数据;

PCIE插卡式无人机干扰信号发生器根据所述内部PCIE逻辑转换电路生成的波形数据产生干扰基带信号;

PCIE插卡式无人机干扰信号发生器将所述干扰基带信号进行调频生成干扰信号对无人机进行干扰。

有益效果

本申请集成了大容量的FPGA组件,200M带宽的数模转换组件以及宽频调制组件,可以通过PCIE总线实时接收上位机发送的干扰波形数据,生成60Mhz-6Ghz的任意波形的干扰信号,或者通过FPGA组件内部逻辑生成常规干扰信号,如定频信号,扫频信号,梳妆波信号,有效的干扰各种无人机,有效解决现有市面上的无人机干扰器无法有效干扰新型无人机跳频遥控信号的问题。

附图说明

为了更清楚地说明本申请实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

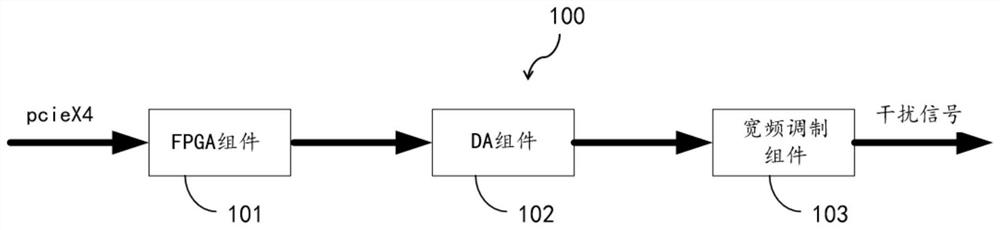

图1为本申请实施例提供的PCIE插卡式无人机干扰信号发生器的结构图;

图2为本申请实施例提供的无人机干扰方法的流程图;

图3为本申请实施例提供的电子设备的结构图。

具体实施方式

下面结合附图对本申请实施例进行详细描述。

以下通过特定的具体实例说明本申请的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本申请的其他优点与功效。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。本申请还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本申请的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

要说明的是,下文描述在所附权利要求书的范围内的实施例的各种方面。应显而易见,本文中所描述的方面可体现于广泛多种形式中,且本文中所描述的任何特定结构及/或功能仅为说明性的。基于本申请,所属领域的技术人员应了解,本文中所描述的一个方面可与任何其它方面独立地实施,且可以各种方式组合这些方面中的两者或两者以上。举例来说,可使用本文中所阐述的任何数目个方面来实施设备及/或实践方法。另外,可使用除了本文中所阐述的方面中的一或多者之外的其它结构及/或功能性实施此设备及/或实践此方法。

还需要说明的是,以下实施例中所提供的图示仅以示意方式说明本申请的基本构想,图式中仅显示与本申请中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

另外,在以下描述中,提供具体细节是为了便于透彻理解实例。然而,所属领域的技术人员将理解,可在没有这些特定细节的情况下实践所述方面。

第一方面,本申请实施例提供的PCIE插卡式无人机干扰信号发生器,所述信号发生器包括PCIE接口数字电路组件,数模转换组件(DA组件)和宽频调制组件,其结构参照图1。

PCIE接口数字电路组件,所述PCIE接口数字电路组件用于接收PCIE数据并通过内部PCIE逻辑转换电路生成波形数据。

数模转换组件,所述数模转换组件的输入端与所述PCIE接口数字电路组件的输出端连接,用于接收所述PCIE接口数字电路组件生成的波形数据并产生干扰基带信号。

宽频调制组件,所述宽频调制组件的输入端与所述数模转换组件的输出端连接,用于将所述干扰基带信号调频生成干扰信号。

本申请实施例提供的PCIE插卡式无人机干扰信号发生器中所采用的数字电路组件可以不做限定,其可以是FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)组件或DSP(Digital Signal Processing,信号数字化处理)组件等。在以下的描述中,以FPGA组件为例进行描述,但是应当理解,还可以是采用其他合适PCIE插卡式无人机干扰信号发生器的数字电路组件。

FPGA的基本结构包括可编程输入输出单元,可配置逻辑模块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核和底层内嵌功能单元。由于FPGA具有布线资源丰富,具有可重复编程和集成度高,投资较低的特点,因此,在本实施例中,采用FPGA组件,将信号发生器设计为PCIE插卡式架构。。

在本实施列中,所述FPGA组件通过PCIE总线(peripheral componentinterconnect express,一种高速串行计算机扩展总线标准)接收上位机发送的信号,所述上位机为可以直接发出操控命令的计算机,但是其具体型号和类型不受限制,只要它可以实现向所述PCIE插卡式无人机干扰信号发生器发送控制命令即可。所述PCIE总线接口包括pcieX1、pcieX4、pcieX8、pcieX12、pcieX16和pcieX32,优选的,所述PCIE总线选用pcieX4接口,带宽可达到20Gbps,以满足数模转换组件的输入带宽要求。

所述FPGA组件接收上位机发送的信号可以为控制命令,由于FPGA是可编程的逻辑列阵,所以可通过所述FPGA组件内部的逻辑生成常规波形的逻辑电路,例如,生成定频信号,扫频信号,梳妆波信号等固定信号需要的波形数据,所述波形数据为数字量信号。

应当理解的是,虽然以上描述了波形数据为定频信号,扫频信号,梳妆波信号,但这仅仅是为了解释本申请而提供的一种示例,并不构成对本申请的限制,其他波形的数据信号也在本申请的保护范围内。

所述FPGA组件接收的所述信号也可以为干扰波形数据,经过FPGA的转化生成数模转换组件所需的波形数据,所述波形数据为数字量信号。

所述数模转换组件是将数字量转换为模拟量的电路,用于将FPGA组件生成的数字量信号转换成模拟量信号,所述数模转换组件包括数模转换器,所述数模转换器由基准电压、数码寄存器、n位模拟开关、解码网络和求和电路组成,其工作原理为:当n位数字量输入时,所述数码寄存器用于存放在数字寄存器的数字量的各位数码,由输入数字量控制所述n位模拟开关实现开关,在所述解码网络中产生权电流,并由所述求和电路将所述权电流相加产生与输入成正比的模拟电压,最终将模拟量输出。

在本实施例中,所述数模转换组件为200M带宽,由于PCIE总线为pcieX4接口,带宽达到20Gbps,所以远远满足200M带宽的数模转换组件的输入带宽要求,保障数据传输的高效性、稳定性和可实现性。所述数模转换组件可以实时的接收FPGA数据从而产生200M带宽的干扰基带信号。

在本实施例中,并不对所述数模转换组件的类别进行限制,其可以由任何类别的数模转换器构成,只要它具有将所述FPGA产生的波形数据转换成所述干扰基带信号的能力即可。

所述宽频调制组件的输入端与所述数模转换组件的输出端连接,用于将所述干扰基带信号调频生成干扰信号,具体的,所述干扰信号为200M带宽的60Mhz-6Ghz频带的任一波形信号。

根据本申请实施例的一种具体实现方式,本申请的信号发生器可设计成其输入端与网口连接的形式。

在一个实施例中,PCIE插卡式无人机干扰信号发生器还可以包括无人机干扰信号发射组件,用于将宽频调制组件产生的干扰信号进行发射。例如可以是天线,具体的是,平面天线或喇叭天线,天线的工作频带覆盖60Mhz-6Ghz频带。

本申请采用大容量FPGA组件,200M带宽数模转换组件和宽频调制组件组合电路,可以生成200M带宽,任意波形60Mhz-6Ghz的干扰信号。而常规的无人机干扰器采用压控震荡器生成干扰信号,这种信号频带窄,响应速度慢,频率单一。

因此,本申请提供的实施例针对新型无人机采用跳频遥控信号进行通信而使现有干扰设备生成的干扰信号没有办法有效干扰的问题,发明了一种PCIE插卡式无人机干扰信号发生器,其可以产生的200M大带宽梳妆波,可以有效压制新型防干扰无人机的跳频遥控信号,或者通过实时接收上位机发送的定频干扰信号以豪秒级的速度发出同频率的遥控干扰信号,实现精准干扰无人机的目的。

与上面的实施例相对应,参见图2,本申请实施例还提供了一种无人机干扰方法,应用于前述的PCIE插卡式无人机干扰信号发生器,包括:

步骤S101,PCIE插卡式无人机干扰信号发生器接收PCIE数据并通过内部PCIE逻辑转换电路生成波形数据;

步骤S102,PCIE插卡式无人机干扰信号发生器根据所述内部PCIE逻辑转换电路生成的波形数据产生干扰基带信号;

步骤S103,PCIE插卡式无人机干扰信号发生器将所述干扰基带信号进行调频生成干扰信号对无人机进行干扰。

图2所示流程图可以对应的执行上述方法实施例中的内容,本实施例未详细描述的部分,参照上述PCIE插卡式无人机干扰信号发生器的实施例中记载的内容,在此不再赘述。

参见图3,本公开实施例还提供了一种电子设备30,电子设备30包括PCIE插卡式无人机干扰信号发生器100,电子设备30还包括:

至少一个处理器;以及,

与该至少一个处理器通信连接的存储器;其中,

该存储器存储有可被该至少一个处理器执行的指令,该指令被该至少一个处理器执行,以使该至少一个处理器能够执行前述方法实施例中的PCIE插卡式无人机干扰信号发生器的干扰方法。

本公开实施例还提供了一种非暂态计算机可读存储介质,该非暂态计算机可读存储介质存储计算机指令,该计算机指令用于使该计算机执行前述方法实施例中的无人机干扰方法。

本公开实施例还提供了一种计算机程序产品,该计算机程序产品包括存储在非暂态计算机可读存储介质上的计算程序,该计算机程序包括程序指令,当该程序指令被计算机执行时,使该计算机执行前述方法实施例中的信号处理方法。

下面参考图3,其示出了适于用来实现本公开实施例的电子设备30的结构示意图。本公开实施例中的电子设备可以包括但不限于诸如移动电话、笔记本电脑、数字广播接收器、PDA(个人数字助理)、PAD(平板电脑)、PMP(便携式多媒体播放器)、车载终端(例如车载导航终端)等等的移动终端以及诸如数字TV、台式计算机等等的固定终端。图3示出的电子设备仅仅是一个示例,不应对本公开实施例的功能和使用范围带来任何限制。

如图3所示,电子设备30可以包括处理装置(例如中央处理器、图形处理器等)301,其可以根据存储在只读存储器(ROM)302中的程序或者从存储装置308加载到随机访问存储器(RAM)303中的程序而执行各种适当的动作和处理。在RAM 303中,还存储有电子设备30操作所需的各种程序和数据。处理装置301、ROM 302以及RAM 303通过总线304彼此相连。输入/输出(I/O)接口303也连接至总线304。

通常,以下装置可以连接至I/O接口305:包括例如触摸屏、触摸板、键盘、鼠标、图像传感器、麦克风、加速度计、陀螺仪等的输入装置306;包括例如液晶显示器(LCD)、扬声器、振动器等的输出装置307;包括例如磁带、硬盘等的存储装置308;以及通信装置309。通信装置309可以允许电子设备30与其他设备进行无线或有线通信以交换数据。虽然图中示出了具有各种装置的电子设备30,但是应理解的是,并不要求实施或具备所有示出的装置。可以替代地实施或具备更多或更少的装置。

特别地,根据本公开的实施例,上文参考流程图描述的过程可以被实现为计算机软件程序。例如,本公开的实施例包括一种计算机程序产品,其包括承载在计算机可读介质上的计算机程序,该计算机程序包含用于执行流程图所示的方法的程序代码。在这样的实施例中,该计算机程序可以通过通信装置309从网络上被下载和安装,或者从存储装置308被安装,或者从ROM 302被安装。在该计算机程序被处理装置301执行时,执行本公开实施例的方法中限定的上述功能。

需要说明的是,本公开上述的计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质或者是上述两者的任意组合。计算机可读存储介质例如可以是——但不限于——电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。计算机可读存储介质的更具体的例子可以包括但不限于:具有一个或多个导线的电连接、便携式计算机磁盘、硬盘、随机访问存储器(RAM)、只读存储器(ROM)、可擦式可编程只读存储器(EPROM或闪存)、光纤、便携式紧凑磁盘只读存储器(CD-ROM)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本公开中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。而在本公开中,计算机可读信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。计算机可读信号介质还可以是计算机可读存储介质以外的任何计算机可读介质,该计算机可读信号介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于:电线、光缆、RF(射频)等等,或者上述的任意合适的组合。

上述计算机可读介质可以是上述电子设备中所包含的;也可以是单独存在,而未装配入该电子设备中。

上述计算机可读介质承载有一个或者多个程序,当上述一个或者多个程序被该电子设备执行时,使得该电子设备:控制所述双工单元对所述发射单元的发射通道及所述接收单元的接收通道进行切换,对所述接收单元隔离所述发射单元产生的射频信号;在所述接收单元的第一开关模块接收的接收信号大于预设阈值的情况下,控制所述第一开关模块的第二输出端与所述第二开关模块的第二输入端导通。

可以以一种或多种程序设计语言或其组合来编写用于执行本公开的操作的计算机程序代码,上述程序设计语言包括面向对象的程序设计语言—诸如Java、Smalltalk、C++,还包括常规的过程式程序设计语言—诸如“C”语言或类似的程序设计语言。程序代码可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或服务器上执行。在涉及远程计算机的情形中,远程计算机可以通过任意种类的网络——包括局域网(LAN)或广域网(WAN)—连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。

附图中的流程图和框图,图示了按照本公开各种实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段、或代码的一部分,该模块、程序段、或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个接连地表示的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或操作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。

描述于本公开实施例中所涉及到的单元可以通过软件的方式实现,也可以通过硬件的方式来实现。其中,单元的名称在某种情况下并不构成对该单元本身的限定,例如,第一获取单元还可以被描述为“获取至少两个网际协议地址的单元”。

应当理解,本公开的各部分可以用硬件、软件、固件或它们的组合来实现。

以上所述,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以权利要求的保护范围为准。

- PCIE插卡式无人机干扰信号发生器、干扰方法及相关设备

- 干扰信号消除模型的训练方法和干扰信号消除方法及设备