复合衬底、复合薄膜及其制备方法,及射频声表面波器件

文献发布时间:2023-06-19 10:38:35

技术领域

本申请涉及半导体技术领域,尤其涉及一种复合衬底、复合薄膜及其制备方法,及射频声表面波器件。

背景技术

目前,硅材料的加工工艺非常成熟,也是产业化应用较多的半导体材料,因此,硅材料已经广泛应用于电子元器件中。由于硅材料本身是中心对称的晶体结构,导致硅没有线性压电效应,因此,硅材料无法直接用于制备高性能射频声表面波器件。

射频声表面波器件的性能取决于复合压电衬底良好的压电性能。复合压电衬底的主要结构包括压电层、低声速绝缘层、高声速陷阱层以及半导体衬底层。其中,压电层为功能层,实现电和声的相互转换,其材料通常为钽酸锂、铌酸锂、石英等;低声速绝缘层一般为非晶绝缘层,其材料通常为二氧化硅;高声速陷阱层主要有两个作用,一是与上层低声速绝缘层产生足够的声速差,构成声波反射界面,限制声波能量的泄露,二是提供大量载流子陷阱,吸收绝缘体半导体界面效应产生的载流子,并限制载流子移动,从而提高界面电阻率,减少因为界面电导导致的射频损耗,高声速陷阱层的材料一般选用多晶硅;半导体衬底层作为支撑层,其材料通常为硅。

目前,高声速陷阱层多为无定形多晶硅层,载流子陷阱密度可能不充足导致声速差受限,为了获得高的声速差,需要生长有较大杨氏模量的多晶硅层,这种多晶硅层在生长时需要比较高的温度。但是,由于热膨胀系数的差异,在半导体衬底层上高温生长的多晶硅层在恢复到常温时具有较大的应力,特别是高温和低温交替的环境下,这个应力通常会达到几十MPa甚至几百MPa,较大的应力作用于高声速陷阱层界面时,容易导致高声速陷阱层界面的化学键断裂而产生层间间隙,甚至是高声速陷阱层直接从半导体衬底层上脱落下来。

发明内容

本申请提供一种复合衬底、复合薄膜及其制备方法,及射频声表面波器件,以解决现有技术中载流子陷阱密度可能不充足导致声速差受限和高声速陷阱层界面的化学键断裂而产生层间间隙,甚至是高声速陷阱层直接从半导体衬底层上脱落下来的问题。

本申请的第一方面,提供一种复合衬底,所述复合衬底从下至上依次包括衬底层和多晶层;所述多晶层包括晶粒渐变层和晶粒均匀层;

其中,所述晶粒渐变层中的晶粒呈柱状结构,所述柱状结构的晶粒由所述衬底层向所述晶粒均匀层方向逐渐变大。

优选的,所述晶粒渐变层中柱状结构晶粒垂直于所述衬底层方向的高度和平行于所述衬底层方向的宽度的比值大于2,且平行于所述衬底层的方向的宽度小于200nm。

优选的,所述晶粒渐变层的厚度范围为10nm-500nm。

优选的,所述多晶层为多晶硅或多晶锗。

本申请的第二方面,提供一种复合薄膜,包括如第一方面任一项所述的复合衬底、隔离层以及功能薄膜层;其中,所述隔离层做平坦化处理,且与所述功能薄膜层键合。

优选的,所述隔离层为二氧化硅、氧化钛、氧化锗、氮化硅以及氮氧化硅中的一种。

优选的,所述功能薄膜层为铌酸锂晶体、钽酸锂晶体、磷酸钛氧铷晶体、磷酸钛氧钾晶体、硅晶体、锗晶体或砷化镓晶体。

本申请的第三方面,提供一种射频声表面波器件,包括如第二方面任一项所述的复合薄膜。

本申请的第四方面,提供一种复合薄膜的制备方法,包括:

对衬底层进行清洗,获得具有洁净表面的衬底层;

将具有洁净表面的衬底层置于沉积炉中,加热至第一温度,所述第一温度低于柱状结构晶体的生长温度;

在沉积炉中通入气体并继续提高温度至第二温度,获得多晶层;

在所述多晶层上生长隔离层,对所述隔离层进行平坦化处理;

在所述隔离层上制备功能薄膜层,得到复合薄膜。

优选的,所述气体为SiH

优选的,所述第一温度的范围为500℃-600℃,所述第二温度的范围为610℃-640℃。

优选的,利用离子注入法结合键合分离法,或者,利用键合法结合研磨抛光法,在所述隔离层上制备所述功能薄膜层。

本申请提供一种复合衬底、复合薄膜及其制备方法,及射频声表面波器件,其中,所述复合衬底从下至上依次包括衬底层和多晶层;所述多晶层包括晶粒渐变层和晶粒均匀层;其中,所述晶粒渐变层中的晶粒呈柱状结构,所述柱状结构的晶粒由所述衬底层向所述晶粒均匀层方向逐渐变大。采用本申请提供的方案,在衬底层上生长晶粒渐变层,衬底层向晶粒均匀层方向逐渐变大的柱状晶粒的密度充足,获得更大的声速差的同时能够分散晶粒均匀层高温冷却后产生较大的应力,避免较大的应力作用于衬底层和晶粒均匀层而导致衬底层和晶粒均匀层之间化学键断裂产生的层间间隙,晶粒均匀层靠近衬底层的表面上有大量小的柱状晶粒,因此具有密集的载流子陷阱,增强限制载流子移动的效果,从而提高界面电阻率,减少射频声表面波器件的射频损耗,提高射频声表面波器件的性能。

附图说明

为了更清楚地说明本申请的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

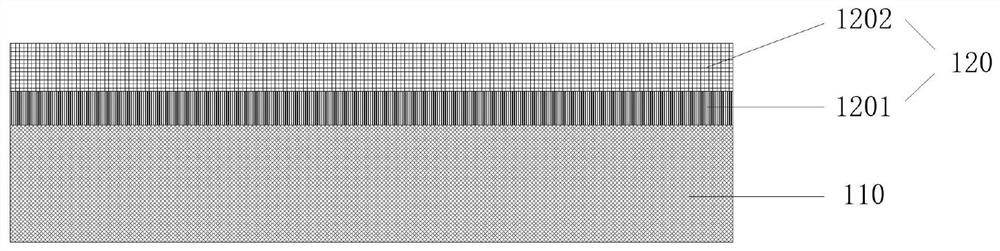

图1为本申请提供的一种复合衬底的结构示意图;

图2为本申请提供的一种复合衬底中晶粒渐变层的结构示意图;

图3为本申请提供的一种复合薄膜的结构示意图;

图4为本申请提供的一种复合薄膜制备方法的流程示意图。

其中,110-衬底层;120-多晶层,1201-晶粒渐变层,1202-晶粒均匀层;130-隔离层;140-功能薄膜层。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

如本申请背景技术所述,现有技术中,复合压电衬底的主要结构包括压电层、低声速绝缘层、高声速陷阱层以及半导体衬底层。其中高声速陷阱层主要有两个作用,一是与上层低声速绝缘层产生足够的声速差,构成声波反射界面,限制声波能量的泄露,二是提供大量载流子陷阱,吸收绝缘体半导体界面效应产生的载流子,并限制载流子移动,从而提高界面电阻率,减少因为界面电导导致的射频损耗。而目前高声速陷阱层多为无定形多晶硅层,载流子陷阱密度可能不充足导致声速差受限,为了获得高的声速差,需要生长有较大杨氏模量的多晶硅层,这种多晶硅层在生长时需要比较高的温度。但是,由于热膨胀系数的差异,在半导体衬底层上高温生长的多晶硅层在恢复到常温时具有较大的应力,特别是高温和低温交替的环境下,这个应力通常会达到几十MPa甚至几百MPa,较大的应力作用于高声速陷阱层界面时,容易导致高声速陷阱层界面的化学键断裂而产生层间间隙,甚至是高声速陷阱层直接从半导体衬底层上脱落下来。

因此,为了解决上述问题,本申请实施例部分提供了一种复合衬底,参见图1和图2,图1为本申请提供的一种复合衬底的结构示意图,图2为本申请提供的一种复合衬底中晶粒渐变层的结构示意图,复合衬底从下至上依次包括衬底层110和多晶层120;多晶层120包括晶粒渐变层1201和晶粒均匀层1202。

其中,晶粒渐变层1201中的晶粒呈柱状结构,柱状结构的晶粒由衬底层110向晶粒均匀层1202方向逐渐变大。

柱状结构的晶粒可以获得高的声速,柱状结构的晶粒平行于衬底层110的方向的截面为不规则的形状,柱状结构晶粒的截面最大宽度由衬底层110向晶粒均匀层1202方向逐渐变大,截面最大宽度小于200nm,且柱状结构的晶粒垂直于衬底层110方向的高度和平行于衬底层110方向的宽度的比值大于2,能够保证充足的陷阱密度,吸收载流子并限制载流子的移动,减少射频损耗。

晶粒均匀层1202的应力主要与晶粒的形状和截面最大宽度有关,其中晶粒的截面最大宽度越大,晶粒均匀层1202的应力也越大,晶粒均匀层1202的应力传递至晶粒渐变层1201上,避免晶粒均匀层1202的应力直接传递至衬底层110导致晶粒均匀层1202与衬底层110之间的化学键断裂。

本申请实施例提供一种复合衬底,复合衬底从下至上依次包括衬底层110和多晶层120;多晶层120包括晶粒渐变层1201和晶粒均匀层1202;其中,晶粒渐变层1201中的晶粒呈柱状结构,柱状结构的晶粒由衬底层110向晶粒均匀层1202方向逐渐变大。采用本申请实施例提供的方案,在衬底层110上生长晶粒渐变层1201,衬底层110向晶粒均匀层1202方向逐渐变大的柱状晶粒的密度充足,获得更大的声速差的同时能够分散晶粒均匀层1202高温冷却后产生较大的应力,避免较大的应力作用于衬底层110和晶粒均匀层1202而导致衬底层110和晶粒均匀层1202之间化学键断裂产生的层间间隙,晶粒均匀层1202靠近衬底层110的表面上有大量小的柱状晶粒,因此具有密集的载流子陷阱,增强限制载流子移动的效果,提高界面电阻率,减少射频声表面波器件的射频损耗,提高射频声表面波器件的性能。

在一具体实施例中,晶粒渐变层1201的厚度范围为10nm-500nm。

在预设的厚度范围内,晶粒渐变层1201的厚度越厚,越能承受晶粒均匀层1202较大的应力,避免较大的应力作用于衬底层110和晶粒均匀层1202而导致衬底层110和晶粒均匀层1202之间化学键断裂产生的层间间隙。

在一具体实施例中,多晶层120为多晶硅或多晶锗。

衬底层110可以为硅、石英、铌酸锂、钽酸锂、蓝宝石以及碳化硅,多晶层120为多晶硅或多晶锗有利于和衬底层110结合,衬底层110的材质可以根据需要选择,本实施例不做具体限定。

参见图3,图3为本申请提供的一种复合薄膜的结构示意图,基于本申请前述实施例所提供的复合衬底,本申请实施例还提供了一种复合薄膜,复合薄膜包括上述实施例中任一项的复合衬底、隔离层130以及功能薄膜层140;其中,隔离层130做平坦化处理,且与功能薄膜层140键合。

将本申请实施例提供的复合衬底应用于复合薄膜中,该复合薄膜具备衬底层110和晶粒均匀层1202通过晶粒渐变层1201结合,以使晶粒均匀层1202不易脱落的优点,可广泛应用。

隔离层130可以为二氧化硅、氧化钛、氧化锗、氮化硅以及氮氧化硅中的一种,其作用是与功能薄膜层140键合。本申请实施例中,可以根据实际想要实现的功能,对应选用功能薄膜层140的材料,功能薄膜层140为铌酸锂晶体、钽酸锂晶体、磷酸钛氧铷晶体、磷酸钛氧钾晶体、硅晶体、锗晶体或砷化镓晶体。

基于上述公开的复合薄膜,本申请实施例还公开了一种射频声表面波器件,射频声表面波器件包括如前述的复合薄膜。

本申请实施例部分还提供一种复合薄膜的制备方法,具体的,如图4所示,制备方法包括以下步骤:

步骤S11,对衬底层110进行清洗,获得具有洁净表面的衬底层110。

可选的,本步骤中衬底层110采用RCA湿式化学清洗法去除衬底层110上颗粒沾污和部分金属杂质,衬底层110的材质可以为硅、铌酸锂、钽酸锂、石英、蓝宝石、碳化硅等,衬底层110的材质可以根据需要选择,本步骤不做具体限定。

步骤S12,将具有洁净表面的衬底层置于沉积炉中,加热至第一温度,第一温度低于柱状结构晶体的生长温度。

可选的,本步骤中,第一温度的范围大于等于500℃,小于等于600℃。在沉积炉的第一温度下,多晶硅的晶粒不均匀,晶粒逐渐变大,形成晶粒渐变层1201。

步骤S13,在沉积炉中通入气体并继续提高温度至第二温度,获得多晶层120。

可选的,本步骤中,在沉积炉中通入SiH4或SiH4、H2的混合气体,第二温度的范围大于等于610℃,小于等于640℃,每分钟温度升高的范围大于等于0.5℃,小于等于10℃,晶粒渐变层1201中的晶粒平行于衬底层110的方向的截面不再变化,当温度升高至第二温度后,多晶硅晶粒达到晶粒均匀层1202的晶粒大小要求,第二温度范围下生长的多晶硅层为晶粒均匀层1202,晶粒均匀层1202中的晶粒均匀,晶粒均匀层1202和晶粒渐变层1201组成多晶层120。

步骤S14,在多晶层120上生长隔离层130,对隔离层130进行平坦化处理。

本步骤中,隔离层130可以为二氧化硅、氧化钛、氧化锗以及氮氧化硅;隔离层130的沉积方法是PECVD、溅射、蒸发、电镀等;采用CMP对隔离层130进行抛光。

步骤S15,在隔离层130上制备功能薄膜层140,得到复合薄膜。

本步骤中,功能薄膜层140的制备方法可以选择利用离子注入法结合键合分离法,或者,利用键合法结合研磨抛光法,本申请不做具体限定。

当选择利用离子注入法结合键合分离法时,其方案包括:对功能薄膜进行离子注入,形成具有薄膜层、分离层和余料层三层结构的功能薄膜晶圆;采用等离子体键合的方式制备形成键合体;将键合体在高温下保温;其中,保温温度为100℃~600℃,保温时间1min~48h,直至余料层从键合体上分离下来形成铌酸锂单晶薄膜;将铌酸锂单晶薄膜抛光至50nm-3000nm,得到具有纳米级厚度的铌酸锂单晶薄膜。

其中,所注入的离子为通过热处理能够生成气体的离子,例如:氢离子或者氦离子,注入氢离子时,注入剂量可以为3×1016ions/cm2-8×1016ions/cm2,注入的能量可以为120KeV-400KeV;注入氦离子时,注入剂量可以为1×1016ions/cm2-1×1017ions/cm2,注入的能量可以为50KeV-1000KeV。通过调整离子注入深度来调整薄膜层的厚度,具体地,离子注入的深度越大,所制备的薄膜层的厚度越大;相反,离子注入的深度越小,所制备的薄膜层的厚度越小。

键合体保温的目的是提升键合体的键合力,使其大于10MPa,并且能够恢复离子注入对薄膜层的损伤,使所获得的铌酸锂薄膜层接近铌酸锂晶圆的性质。在热处理过程中,分离层内形成有气泡,例如,氢离子形成氢气,氦离子形成氦气等,随着热处理进展,分离层内的气泡连成一片,最后分离层裂开,将余质层与薄膜层分离,从而使余质层由键合体上剥离下来。

当选择利用键合法结合研磨抛光法时,具体方案包括:对铌酸锂晶圆工艺面进行清洗,采用等离子体键合的方法将清洗后的铌酸锂晶圆的工艺面与二氧化硅层进行键合,形成键合体;将键合体放入加热设备内在高温下进行保温,在真空环境下或在氮气及惰性气体中至少一种气体形成的保护气氛下进行;其中,保温温度为100℃~600℃,保温时间1min~48h,此环节可以提升键合体的键合力,使其大于10MPa;采用机械研磨的方式减薄至1μm-102μm,然后抛光至400nm-100μm,得到具有微米级厚度的铌酸锂单晶薄膜。

在离子注入之后,进行键合之前,通常需要对两个相接触的键合面进行清洗,以增强键合效果。

半导体衬底的表面上一般晶体缺陷较多,并且还有自然氧化层的产生,在此半导体衬底上生长膜层时,晶体缺陷导致半导体衬底与膜层的界面的载流子较为集中,增加射频损耗。另外,在单晶衬底上生长同质多晶层时,如果直接生长多晶层,容易产生晶格耦合现象,即沿着单晶衬底中单晶的晶向生长具有晶格趋向性的多晶层甚至是单晶层,导致载流子陷阱密度严重下降。

本申请提供的复合薄膜的制备方法,使多晶层120靠近衬底层110的界面处具有小的柱状晶粒,可以拥有更密集的载流子陷阱,提高载流子的限制效果和抑制晶格耦合现象。

本申请实施例提供的复合薄膜可应用于射频声表面波器件中,该射频声表面波器件的射频损耗低可广泛应用。本申请实施例提供的复合薄膜还具有良好的光电性能,可以运用到光电调制器方向。

本申请实施例中,结构部分的实施例与制备方法部分的实施例可以相互参见,此处不再赘述。

为了使本申请的方案更清楚,本申请实施例进一步公开了具体示例。

实施例1(离子注入法结合键合分离法)

1)准备单晶硅衬底,并采用RCA湿式化学清洗法清洗。

2)将步骤1)中清洗后的单晶硅衬底放置低压气相沉积炉中,加热至580℃。

3)通入SiH

4)在晶粒均匀层上生长二氧化硅,对生长后的二氧化硅进行研磨抛光,形成隔离层。

5)准备与单晶硅衬底相同尺寸的铌酸锂晶圆,采用离子注入的方法,将氦离子(He+)注入铌酸锂晶片中,氦离子的注入能量为200KeV,剂量为4×10

6)采用等离子体键合的方法将离子注入后的铌酸锂晶圆的薄膜层与硅晶圆衬底的二氧化硅层(隔离层)进行键合,形成键合体;然后将键合体放入加热设备内在高温下进行保温,直至余料层从键合体上分离下来形成铌酸锂单晶薄膜。保温工艺在真空环境下或在氮气及惰性气体中至少一种气体形成的保护气氛下进行,保温温度为400℃,保温时间3h。

7)之后对铌酸锂单晶薄膜进行抛光减薄至400nm,得到具有纳米级厚度的铌酸锂单晶薄膜。

可见,实施例1是采用离子注入结合键合分离的方法,其中晶粒渐变层和晶粒均匀层形成多晶层;隔离层为二氧化硅,功能薄膜层为铌酸锂,功能薄膜层是离子注入后,再与隔离层键合分离制得。

实施例2(键合法结合研磨抛光法)

1)准备单晶硅衬底,并采用RCA湿式化学清洗法清洗。

2)将步骤1)中清洗后的单晶硅衬底放置低压气相沉积炉中,加热至500℃。

3)通入SiH

4)在晶粒均匀层上生长二氧化硅,对生长后的二氧化硅进行研磨抛光,形成隔离层。

5)准备与单晶硅衬底相同尺寸的铌酸锂晶圆,对工艺面进行清洗,采用等离子体键合的方法将清洗后的铌酸锂晶圆的工艺面与步骤4)制备的二氧化硅层(隔离层)进行键合,形成键合体;然后将键合体放入加热设备内在高温下进行保温,保温工艺在真空环境下或在氮气及惰性气体中至少一种气体形成的保护气氛下进行,保温温度为400℃,保温时间3h,此环节可以提升键合力大于10MPa。

6)之后对铌酸锂单晶薄膜采用机械研磨的方式减薄至22μm,然后抛光至20μm,得到具有微米级厚度的铌酸锂单晶薄膜。

可见,实施例2是采用直接键合结合研磨抛光的方法,其中晶粒渐变层从非晶硅生长为含有柱状晶粒的多晶硅,隔离层为二氧化硅,功能薄膜层为铌酸锂,功能薄膜层直接与隔离层键合,然后研磨抛光制得。

实施例3(离子注入法结合键合分离法)

1)准备单晶硅衬底,并采用RCA湿式化学清洗法清洗。

2)将步骤1)中清洗后的单晶硅衬底放置低压气相沉积炉中,加热至550℃。

3)通入SiH

4)在晶粒均匀层上生长氮氧化硅,对生长后的氮氧化硅进行研磨抛光,形成隔离层。

5)准备与单晶硅衬底相同尺寸的铌酸锂晶圆,采用离子注入的方法,将氦离子(He+)注入铌酸锂晶片中,氦离子的注入能量为200KeV,剂量为4×10

6)采用等离子体键合的方法将离子注入后的铌酸锂晶圆的薄膜层与硅晶圆衬底的氮氧化硅层(隔离层)进行键合,形成键合体;然后将键合体放入加热设备内在高温下进行保温,直至余料层从键合体上分离下来形成铌酸锂单晶薄膜。保温工艺在真空环境下或在氮气及惰性气体中至少一种气体形成的保护气氛下进行,保温温度为400℃,保温时间3h。

7)之后对铌酸锂单晶薄膜进行抛光减薄至100nm,得到具有纳米级厚度的铌酸锂单晶薄膜。

可见,实施例3是采用离子注入结合键合分离的方法,其中晶粒渐变层和晶粒均匀层形成多晶层;隔离层为氮氧化硅,功能薄膜层为铌酸锂,功能薄膜层是离子注入后,再与隔离层键合分离制得。

实施例4(键合法结合研磨抛光法)

1)准备单晶硅衬底,并采用RCA湿式化学清洗法清洗。

2)将步骤1)中清洗后的单晶硅衬底放置低压气相沉积炉中,加热至550℃。

3)通入SiH

4)在晶粒均匀层上生长氮氧化硅,对生长后的氮氧化硅进行研磨抛光,形成隔离层。

5)准备与单晶硅衬底相同尺寸的铌酸锂晶圆,对工艺面进行清洗,采用等离子体键合的方法将清洗后的铌酸锂晶圆的工艺面与步骤4)制备的氮氧化硅层(隔离层)进行键合,形成键合体;然后将键合体放入加热设备内在高温下进行保温,保温工艺在真空环境下或在氮气及惰性气体中至少一种气体形成的保护气氛下进行,保温温度为400℃,保温时间3h,此环节可以提升键合力大于10MPa。

6)之后对铌酸锂单晶薄膜采用机械研磨的方式减薄至22μm,然后抛光至20μm,得到具有微米级厚度的铌酸锂单晶薄膜。

可见,实施例4是采用直接键合结合研磨抛光的方法,其中晶粒渐变层从非晶硅生长为含有柱状晶粒的多晶硅,隔离层为氮氧化硅,功能薄膜层为铌酸锂,功能薄膜层直接与隔离层键合,然后研磨抛光制得。

另外,在上述实施例的基础上,还可以衍生其他的实施例,例如:在各实施例的基础上,将实施例中的功能薄膜层替换为钽酸锂、砷化镓、石英、或者硅,其他工艺参数均可以不用改变或者根据需要改变;也就是说,本领域技术人员可以根据上述实施例自行组合替换材料以及工艺参数,本申请不做具体限定。

上述实施例1和3是采用离子注入结合键合分离的方法制备,可得到具有纳米级厚度的铌酸锂单晶薄膜;实施例2和4是采用直接键合结合研磨抛光的方法制备,得到具有微米级厚度的铌酸锂单晶薄膜。

以上结合具体实施方式和范例性实例对本申请进行了详细说明,不过这些说明并不能理解为对本申请的限制。本领域技术人员理解,在不偏离本申请精神和范围的情况下,可以对本申请技术方案及其实施方式进行多种等价替换、修饰或改进,这些均落入本申请的范围内。本申请的保护范围以所附权利要求为准。

- 复合衬底、复合薄膜及其制备方法,及射频声表面波器件

- 一种复合衬底、复合薄膜及其制备方法,及射频滤波器