基于集成DPU多核异构的神经网络计算加速方法及装置

文献发布时间:2023-06-19 11:29:13

技术领域

本发明涉及深度学习领域,具体涉及基于集成DPU多核异构的神经网络计算加速方法即装置。

背景技术

随着深度学习领域理论和技术的发展,深度神经网络模型已经成为解决部分计算机领域复杂的机器学习任务的最优选择,如计算机视觉、语音的识别和搜索、图像特征编码、图像的分类和划分、文本的语义分析、音频处理以及信息检索等等。虽然利用广而深的神经网络模型可以在很多实际问题上获得极好的效果,但是深度神经网络模型有着一个较为明显的缺陷,即上千万甚至上亿的学习参数,这导致神经网络对计算机的内存和计算资源消耗巨大。而现阶段的嵌入式设备又无法提供如此高性能的计算能力和内存容量,所以加速深度神经网络的训练和推断过程,减少计算量的技术需求很迫切。

发明内容

针对上述现有技术存在的问题,本发明提供了一种基于集成DPU多核异构的神经网络计算加速方法及装置,该技术方案如下:

第一方面,提供了基于集成DPU多核异构的神经网络计算加速方法,包括如下步骤:

检测待计算神经网络的卷积核候选冗余数据,所述候选冗余数据包括网络拓扑结构和卷积核参数;

根据候选冗余数据对神经网络进行优化缩减并进行重新训练,获取优化网络;

基于优化网络进行待处理数据的计算;

所述重新训练过程以及待处理数据的计算过程采用基于DPU多核异构处理器系统进行。

在一种可能的实现方式中,所述根据候选冗余数据对神经网络进行优化缩减并进行重新训练,包括:

对不同网络层裁剪不同数量的重要性低的卷积核,并对神经网络进行重新训练;

对网络层的卷积核参数进行关于比特数的减小处理,并对神经网络进行重新训练。

在一种可能的实现方式中,所述对不同网络层裁剪不同数量的重要性低的卷积核,包括:

根据同一网络层上的不同卷积核的重要度大小,获得同一网络层上不同卷积核的裁剪优先度,所述重要度采用至少两种重要性分析结果的融合重要度;

根据不同网络层对于神经网络准确率的关联性大小确定不同网络层的裁剪数量。

在一种可能的实现方式中,所述获得同一网络层上不同卷积核的裁剪优先度,包括:

基于不同卷积核输出和网络输出的损失信息大小,确定不同卷积核重要度;

基于卷积核输出值与剩余卷积核输出值间的相关度,计算卷积核与整个网络的相关度,确定不同卷积核重要度;

基于卷积核权值矩阵的L1范数大小,确定不同卷积核重要度;

基于对于同一卷积核的不同种类重要度排序号获取融合排序号。

在一种可能的实现方式中,所述根据不同网络层对于神经网络准确率的关联性大小确定不同网络层的裁剪数量,包括:

基于预设值单独对每层网络剪除相同数量的卷积核,并获取对单层网络进行剪枝后的网络模型精度的损失量;

基于单层网络剪枝后的网络模型精度损失量的不同数值,调节每层网络实际需要剪除的卷积核数量,以使单层网络剪枝后的网络模型精度损失量一致。

在一种可能的实现方式中,所述对网络层的卷积核参数进行关于比特数的减小处理,包括:

将网络层所有卷积核权重参数组成矩阵A,将矩阵A分解为A=B*C,其中,B是共享权值矩阵,C是线性组合系数矩阵;

基于目标函数进行迭代学习获得矩阵B和C;

基于矩阵C的参数进行量化、编码以缩减网络权重参数。

在一种可能的实现方式中,所述基于目标函数进行迭代学习获得矩阵B和C,包括:

基于初始化矩阵B,通过正交匹配追踪法求解矩阵C的每一列数据,获得矩阵C;

通过K奇异值分解更新矩阵B;

迭代矩阵C和B直至收敛,所述更新过程中的目标函数为:

在一种可能的实现方式中,所述基于矩阵C的参数进行量化、编码以缩减网络权重参数,包括:

基于矩阵C中的不为0的元素重新组合矩阵C1,并获得不为0的元素位置矩阵D;

基于矩阵C1中的元素进行量化编码。

第二方面,提供了一种基于集成DPU多核异构的神经网络计算加速装置,包括:

神经网络数据检测单元,用于检测待计算神经网络的卷积核候选冗余数据,所述候选冗余数据包括网络拓扑结构和卷积核参数;

神经网络优化单元,用于根据候选冗余数据对神经网络进行优化缩减并进行重新训练,获取优化网络;

神经网络计算单元,用于基于优化网络进行待处理数据的计算,所述重新训练过程以及待处理数据的计算过程采用基于DPU多核异构处理器系统进行。

第三方面,提供了一种电子设备,所述电子设备包括:

存储器,用于存储可执行指令;

处理器,用于运行所述存储器存储的可执行指令时,实现上述的神经网络计算加速方法。

本发明的一种基于集成DPU多核异构的神经网络计算加速方法,具备如下有益效果:

1、对于神经网络计算加速,从网络模型本身和网络模型计算架构两方面结合,通过软件优化设计与硬件加速运算的协同作用,实现神经网络的推理过程加速。

2、在软件优化方面,通过多种重要性分析方法获得卷积核的融合重要性,避免一种参数重要性分析结果对于网络的卷积核重要性判断存在片面性,同时,对于多种重要性分析方法的融合采用基于排序序号相加进行融合,不需要考虑不同重要性判断方法后的重要度区间差异以及不同网络层之间的重要度数值区间差异,使得对于卷积核的重要性判断更为准确。

3、在软件优化方面,通过对网络层权重参数分解为共享权重矩阵和线性系数矩阵,并且通过对于线性系数矩阵中的非零项进行(0,1)区间映射和整数转换,结合编码过程缩减网络模型的计算量。

附图说明

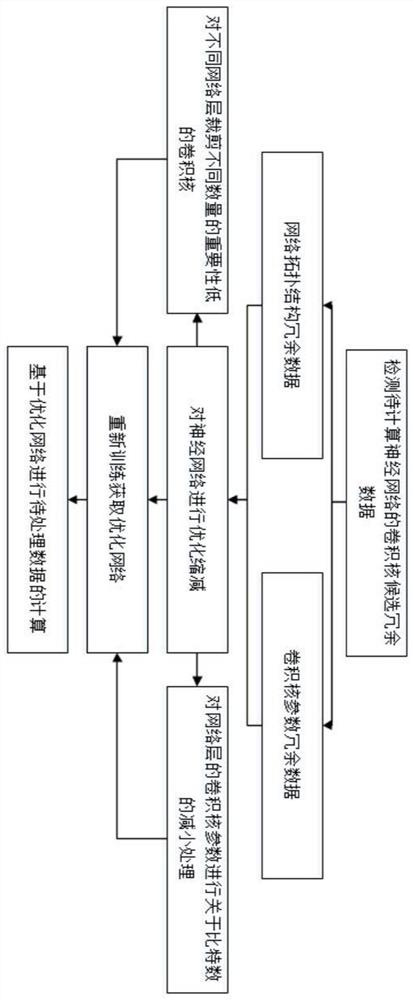

图1是本发明的基于集成DPU多核异构的神经网络计算加速方法的流程框图;

图2是本发明的基于集成DPU多核异构的神经网络计算加速装置的结构框图。

具体实施方式

为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作进一步地详细描述,所描述的实施例不应视为对本发明的限制,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

本实施例提供的基于集成DPU多核异构的神经网络计算加速方法,包括如下步骤:

检测待计算神经网络的卷积核候选冗余数据,所述候选冗余数据包括网络拓扑结构和卷积核参数,一般来说,训练后的神经网络模型包括网络拓扑结构和神经网络参数数据;

根据候选冗余数据对神经网络进行优化缩减并进行重新训练,获取优化网络;

基于优化网络进行待处理数据的计算;

所述重新训练过程以及待处理数据的计算过程采用基于DPU多核异构处理器系统进行。

本实施例中,对于神经网络计算加速,从网络模型本身和网络模型计算架构两方面结合,通过软件优化设计与硬件加速运算的协同作用,实现神经网络的推理过程加速。

具体的,硬件加速运算方面,采用基于CPU+FPGA的多核异构DPU处理系统架构,其中,FPGA芯片,用于实现可编程逻辑计算,包括神经网络的卷积层、池化层和全连接层的数据计算,CPU用于执行裸机程序,其中CPU和FPGA之间通过数据传输单元进行数据和指令的传输;

在软件优化方面,通过对网络模型的候选冗余数据对神经网络进行优化缩减并进行重新训练,获得优化后的网络模型,具体的,该步骤包括:

首先在网络结构上进行缩减以减小网络模型的规模,即对不同网络层裁剪不同数量的重要性低的卷积核,并对神经网络进行重新训练;

其次对网络层的权重参数进行缩小以减小计算量,即对网络层的卷积核参数进行关于比特数的减小处理,并对神经网络进行重新训练。

上述对不同网络层裁剪不同数量的重要性低的卷积核,包括:

根据同一网络层上的不同卷积核的重要度大小,获得同一网络层上不同卷积核的裁剪优先度,其中重要度采用至少两种重要性分析结果的融合重要度,基于多种重要性分析方法,主要是为了避免一种参数重要性分析结果对于网络的卷积核重要性判断存在片面性。

根据不同网络层对于神经网络准确率的关联性大小确定不同网络层的裁剪数量,不同的网络层对于神经网络准确率的关联性大小不同,一般来说,神经网络层越靠近输出层,则其需要裁剪的卷积核越少。

上述获得同一网络层上不同卷积核的裁剪优先度,包括:

基于不同卷积核输出和网络输出的损失信息大小,确定不同卷积核重要度,该损失信息大小基于交叉熵函数计算获取,损失信息

基于卷积核输出值与剩余卷积核输出值间的相关度,计算卷积核与整个网络的相关度,确定不同卷积核重要度,该相关度为

基于卷积核权值矩阵的L1范数大小,确定不同卷积核重要度,值得说明的是,考虑到卷积层一般跟BN层结合,所以该卷积核权值矩阵的L1范数,包括BN层的缩放系数和平移系数;

基于对于同一卷积核的不同种类重要度排序号获取融合排序号,考虑到上述三种方法计算出来的损失信息大小、卷积核输出值与剩余卷积核输出值间的相关度、卷积核权值矩阵的L1范数大小的数值差异,不能采用直接将同一卷积核的三个重要性结果相加,而是对其三种重要性排序的序号进行融合,获得融合重要性排序,若排序从大到小排列,则在下述的裁剪过程中,排序靠后的卷积核为优选裁剪项。

上述根据不同网络层对于神经网络准确率的关联性大小确定不同网络层的裁剪数量,包括:

基于预设值单独对每层网络剪除相同数量的卷积核,并获取对单层网络进行剪枝后的网络模型精度的损失量;

基于单层网络剪枝后的网络模型精度损失量的不同数值,调节每层网络实际需要剪除的卷积核数量,以使单层网络剪枝后的网络模型精度损失量一致。

基于上述方法,不需要逐层进行裁剪进行网络模型重新训练,减小了对网络模型裁剪过程的计算量以及处理时间,而且能够获取准确的每个网络层需要裁剪的卷积核数量,避免一些网络层裁剪的卷积核过多造成严重的精度损失,减小网络在裁剪后网络模型的精度损失。

基于对网络结构进行缩减后,接下来对网络权重参数进行优化,该步骤包括:

将网络层所有卷积核权重参数组成矩阵A,将矩阵A分解为A=B*C,其中,B是共享权值矩阵,C是线性组合系数矩阵,具体的,矩阵A的组成方法为:

先基于每个网络层的参数矩阵a

基于目标函数进行迭代学习获得矩阵B和C,该目标函数为:

矩阵B和C的迭代更新完成后,基于矩阵C的参数进行量化编码以缩减网络权重参数,基于矩阵C中的不为0的元素重新组合矩阵C1,并获得不为0的元素位置矩阵D,基于矩阵C1中的元素进行量化编码,该量化方式可以通过将其映射到(0,1)区间,然后进行取整。

本实施例还提供了基于集成DPU多核异构的神经网络计算加速装置,包括:

神经网络数据检测单元,用于检测待计算神经网络的卷积核候选冗余数据,所述候选冗余数据包括网络拓扑结构和卷积核参数;

神经网络优化单元,用于根据候选冗余数据对神经网络进行优化缩减并进行重新训练,获取优化网络;

神经网络计算单元,用于基于优化网络进行待处理数据的计算,所述重新训练过程以及待处理数据的计算过程采用基于DPU多核异构处理器系统进行。

具体的,神经网络优化单元包括:网络拓扑优化单元和卷积核参数优化单元,其中网络拓扑优化单元,用于对不同网络层裁剪不同数量的重要性低的卷积核,并对神经网络进行重新训练;卷积核参数优化单元,用于对对网络层的卷积核参数进行关于比特数的减小处理,并对神经网络进行重新训练。

本实施例还提供了一种电子设备,所述电子设备包括:

存储器,用于存储可执行指令;

处理器,用于运行所述存储器存储的可执行指令时,实现上述的神经网络计算加速方法。

本实施例提供的神经网络计算加速装置可以采用软硬件结合的方式,直接体现为由集成DPU多核异构处理器系统执行的软件模块组合,软件模块可以位于存储介质中,存储介质位于存储器,集成DPU多核异构处理器系统读取存储器中软件模块包括的可执行指令,结合必要的硬件完成本实施例提供的神经网络计算加速方法。

本发明不局限于上述具体的实施方式,本领域的普通技术人员从上述构思出发,不经过创造性的劳动,所做出的种种变换,均落在本发明的保护范围之内。

- 基于集成DPU多核异构的神经网络计算加速方法及装置

- 基于数据流结构的低精度神经网络计算装置及加速方法