多晶粒封装

文献发布时间:2023-06-19 19:18:24

技术领域

本发明申请是关于包含动态随机存取内存(Dynamic Random Access Memory,DRAM)的多晶粒封装架构。

背景技术

目前的半导体封装技术可以将多个晶粒(die)整合在单个封装中,以减少在印刷电路板(Printed Circuit Board,PCB)上的走线和面积。举例来说,传统上DRAM与处理器分别属于两个芯片/封装,所以需要在印刷电路板上设计多个走线和接点以连接这两个芯片,而若是处理器和DRAM被整合在单一封装中以使得处理器可以通过封装内部的走线和接点来存取DRAM,则可以减少上述印刷电路板上的走线和接点。

然而,若是在单一封装内设置处理器和DRAM,由于封装内的晶粒无法再增加,所以会使得DRAM的容量只能维持在一开始的设计值,而缺乏可扩充性。换句话说,若是设计者需要设计应用在多个不同产品的处理器和DRAM,且这些不同产品所需要的DRAM容量也不完全相同,则设计者会需要针对多个不同DRAM容量来进行芯片设计,因而增加设计和制造成本。

发明内容

因此,本发明的目的之一在于提出一种多晶粒封装架构,其可以允许对DRAM容量进行扩充,以解决先前技术中所述的问题。

在本发明的一个实施例中,揭露一种多晶粒封装,其包含主晶粒、内存晶粒、第一组引脚以及第二组引脚,其中该主晶粒包含内存控制器、第一组接点、第二组接点以及第三组接点,该内存晶粒耦接于该主晶粒的该第一组接点和该第二组接点,该第一组引脚耦接于该主晶粒的该第三组接点,以及该第二组引脚耦接于该主晶粒的该第二组接点。此外,该内存控制器通过该第一组接点和该第二组接点来存取该内存晶粒,并通过该第二组接点和该第三组接点存取位于该多晶粒封装外的内存芯片。

有关本发明的特征、实际操作和功效,将结合附图作实施例详细说明如下。

附图说明

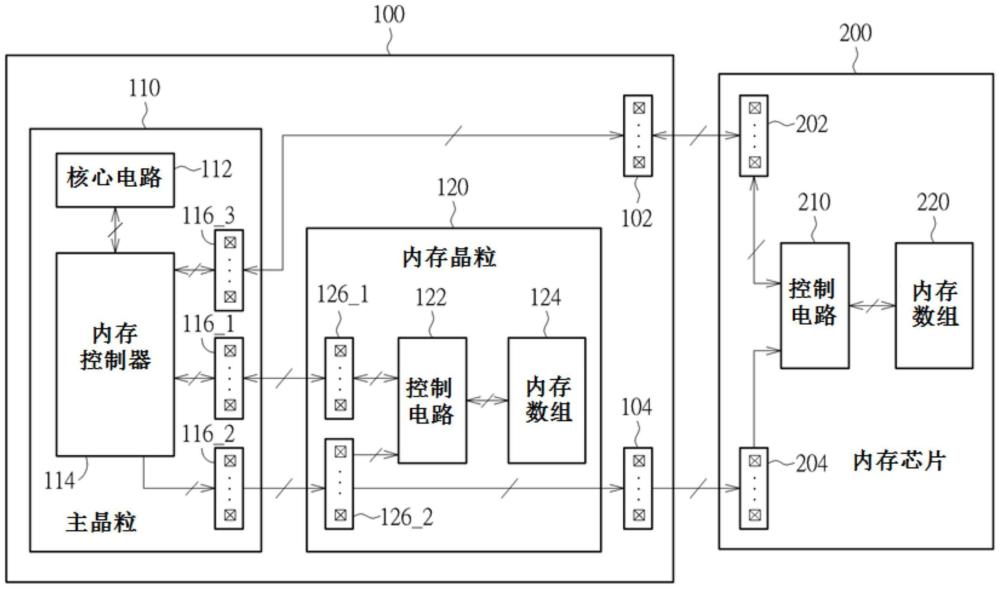

图1为根据本发明一个实施例的多晶粒封装的示意图。

图2为根据本发明一个实施例的多晶粒封装和内存芯片的示意图。

符号说明

100:多晶粒封装

102:多晶粒封装的第一组引脚

104:多晶粒封装的第二组引脚

110:主晶粒

112:核心电路

114:内存控制器

116_1:主晶粒的第一组接点

116_2:主晶粒的第二组接点

116_3:主晶粒的第三组接点

120:内存晶粒

122:控制电路

124:内存数组

126_1:内存晶粒的第一组接点

126_2:内存晶粒的第二组接点

200:内存芯片

202:内存芯片的第一组引脚

204:内存芯片的第二组引脚

210:控制电路

220:内存数组

具体实施方式

在下文更详细地描述本发明的实施例。然而,应了解,本发明提供了可在广泛、多种特定场景中体现的许多适用的概念。所述实施例仅用于说明,但是并不限制本发明申请的范畴。

图1为根据本发明一个实施例的多晶粒封装100的示意图。如图1所示,多晶粒封装100包含主晶粒110、内存晶粒120以及多组引脚(在本实施例中仅绘出相关的第一组引脚102和第二组引脚104),其中第一组引脚102和第二组引脚104均包含多个引脚。在本实施例中,主晶粒110可以是处理器,例如中央处理器(Central Processing Unit,CPU),且主晶粒110包含核心电路112、内存控制器114以及多组接点(在本实施例中仅绘出相关的第一组接点116_1、第二组接点116_2和第三组接点116_3),其中第一组接点116_1、第二组接点116_2和第三组接点116_3中的每一者均包含多个接点;此外,内存晶粒120包含控制电路122、内存数组124以及多组接点(在本实施例中仅绘出相关的第一组接点126_1和第二组接点126_2)。此外,在本实施例中,内存晶粒120系为DRAM晶粒,而主晶粒110中的内存控制器114系为DRAM控制器,但本发明并不以此为限。

在本实施例中,主晶粒110的第一组接点116_1是数据接点,其用来通过内存晶粒120的第一组接点126_1来将数据传送至内存晶粒120,和/或接收来自内存晶粒120的数据,亦即主晶粒110的第一组接点116_1与内存晶粒120的第一组接点126_1是通过多个连接线连接,其中所述多个连接线至少用于发送多个双向(bi-directional)数据信号(DataSignal,DQ)、一个或多个双向数据选通信号(Data Strobe Signal,DQS)…等等。主晶粒110的第二组接点116_2是控制信号接点,其用来将频率信号、控制信号和地址信号传送至内存晶粒120的第二组接点126_2以供内存晶粒120使用,且也通过第二组引脚104将控制信号和地址信号传送至多晶粒封装100外的组件,其中上述的频率信号、控制信号和地址信号包含读取命令/写入命令、写入致能(write enable)、列地址信号(row address strobe)、行地址信号(column address strobe)…等等。主晶粒110的第三组接点116_3是数据接点,其用来通过第一组引脚102将数据传送至多晶粒封装100外的组件,和/或自外部组件接收数据,亦即主晶粒110的第一组接点116_1和多晶粒封装100外的组件系通过多个连接线连接,其中所述多个连接线至少用于发送多个双向数据信号(DQ)、一个或多个双向数据选通信号(DQS)…等等。在本实施例中,内存控制器110通过第三组接点116_3和第一组引脚102来存取多晶粒封装100外的组件的路径不会经过内存晶粒120。

在多晶粒封装100的一般操作中,内存控制器114可以从核心电路112接收请求,并通过第一组接点116_1和第二组接点116_2来发送数据信号、数据选通信号、多个命令信号及频率信号中的一部分来存取内存晶粒120。具体来说,内存控制器114中可以包含相关的电路,例如地址译码器、处理电路、写/读缓冲器,控制逻辑以及仲裁器等,以供产生数据信号、数据选通信号、多个命令信号及频率信号至内存晶粒120。此外,在内存晶粒120中,控制电路122可包括读/写控制器、行译码器和列译码器,且控制电路124自第一组接点126_1和第二组接点126_2接收来自内存控制器的数据信号、数据选通信号、多个命令信号及频率信号以对内存数组124进行存取。

在以上的实施例中,由于多晶粒封装100中的内存晶粒120的容量是固定的,因此,当多晶粒封装100需要应用至对内存容量和效能需求较高的电子产品时,内存晶粒120的容量便不足以应付需求。因此,本实施例的多晶粒封装100可以通过外接另一个内存芯片,以提升内存容量和效能。具体来说,参考图2,其包含多晶粒封装100和内存芯片200,其中内存芯片200包含控制电路210、内存数组220以及多组引脚(在本实施例中仅绘出相关的第一组引脚202和第二组引脚204)。此外,在本实施例中,内存芯片200是DRAM芯片,多晶粒封装100和内存芯片200系设置于印刷电路板上,且多晶粒封装100的第一组引脚102和第二组引脚104系通过印刷电路板上的连接线与内存芯片200的第一组引脚202和第二组引脚204彼此连接。

在图2所示的多晶粒封装100和内存芯片200的操作中,内存控制器114可以从核心电路112接收请求,并通过第二组接点116_2来发送多个命令信号至内存晶粒120和内存芯片200,以对内存晶粒120和内存芯片200中的至少其一来进行存取。具体来说,当核心电路112所执行的应用程序只需要使用较低的内存访问速度和效能时(例如,较低的带宽),内存控制器114可以从核心电路112接收请求,并通过第一组接点116_1和第二组接点116_2发送数据信号、数据选通信号、多个命令信号及频率信号中的一部分来存取内存晶粒120,以读取内存数组124中的数据,或是将数据写入至内存数组124;此时,由于内存控制器114不需要存取内存芯片200,所以内存芯片200中的控制电路210可以忽略自第二组引脚204所接收的多个命令信号,和/或内存芯片200可以进入至省电模式。在另一实施例中,当核心电路112所执行的应用程序只需要使用较低的内存访问速度和效能时,内存控制器114也可以从核心电路112接收请求,并通过第二组接点116_2和第三组接点116_3发送数据信号、数据选通信号、多个命令信号及频率信号中的一部分来存取内存芯片200,以读取内存数组220中的数据,或是将数据写入至内存数组220;此时,由于内存控制器114不需要存取内存晶粒120,所以内存晶粒120中的控制电路122可以忽略自第二组接点126所接收的多个命令信号,和/或内存晶粒120可以进入至省电模式。

当核心电路112所执行的应用程序需要使用较高的内存访问速度和效能时(例如,较高的带宽),内存控制器114可以从核心电路112接收请求,并通过第二组接点116_2发送多个命令信号来同时存取内存晶粒120和内存芯片200。具体来说,内存控制器114通过第二组接点116_2所发送的多个命令信号可以包含写入命令和内存数组124的地址以及内存数组220的地址,而此时内存控制器114将第一组数据通过第一组接点116_1传送至内存晶粒120以写入至内存数组124的对应地址中,且同时地,内存控制器114将第二组数据通过第三组接点116_3传送至内存芯片200以写入至内存数组220的对应地址中。此外,内存控制器114通过第二组接点116_2所发送的多个命令信号可以包含读取命令和内存数组124的地址以及内存数组220的地址,而此时内存晶粒120中的控制电路122会根据所接收到的地址以自内存数组124读取第一组数据,并将第一组数据通过第一组接点126_1传送至内存控制器114;同时地,内存芯片200中的控制电路210会根据所接收到的地址以自内存数组220读取第二组数据,并将第二组数据通过第一组引脚202传送至内存控制器114。

在一实施例中,主晶粒110中用来传送或接收第一组数据的第一组接点116_1的带宽可以与用来传送或接收第二组数据的第三组接点116_3的带宽相同,例如上述第一组数据和第二组数据的带宽可以是16位;而多晶粒封装100可以根据是否链接至内存芯片200,或是根据是否需要同时存取内存晶粒120和内存数组220来决定要采用16位的带宽或是32位的带宽。在另一实例中,上述第一组数据和第二组数据的带宽可以是8位,而多晶粒封装100可以根据是否链接至内存芯片200,或是根据是否需要同时存取内存晶粒120和内存数组220来决定要采用8位的带宽或是16位的带宽。

简要归纳本发明,在本发明的多晶粒封装100,通过相关接点/引脚的设计,可以简单地通过在外部连接内存芯片200来达到扩展内存容量和速度的效果,且多晶粒封装100也可以适用于多种对于内存带宽需求不同的电子产品中,以降低设计上的成本。

以上所述仅为本发明的较佳实施例,凡依本发明申请上述公开内容所做的均等变化和修饰,都应属于本发明的保护范围之内。