具有包括堆叠式SRAM的片上系统(SoC)集成电路部件的人工现实系统

文献发布时间:2023-06-19 19:33:46

技术领域

本公开总体上涉及人工现实系统(例如,增强现实系统、混合现实系统和/或虚拟现实系统)、以及用于这些电子系统和其他电子系统的半导体设备和半导体工艺。

背景技术

人工现实系统在诸如计算机游戏、健康与安全、工业以及教育等许多领域中的应用正变得越来越普遍。作为几个示例,人工现实系统正被结合到移动设备、游戏控制台、个人计算机、电影院和主题公园中。通常,人工现实是在呈现给用户之前已经以某种方式进行了调整的现实形式,该现实形式例如可以包括虚拟现实(virtual reality,VR)、增强现实(augmented reality,AR)、混合现实(mixed reality)、混合现实(hybrid reality)或它们的某种组合和/或衍生物。

典型的人工现实系统包括用于渲染内容并向用户显示内容的一个或多个设备。作为一个示例,人工现实系统可以包含头戴式显示器(head-mounted display,HMD),该头戴式显示器由用户佩戴且被配置为向用户输出人工现实内容。人工现实内容可以完全包括由系统生成的内容,或者可以包括与所采集的内容(例如,真实世界视频和/或图像)相结合的所生成的内容。在操作期间,用户通常与人工现实系统交互,以选择内容、启动应用、配置系统、以及通常体验人工现实环境。一些人工现实系统利用通常称为片上系统(System on aChip,SoC)的专用集成电路,该专用集成电路具有用于聚集和处理传感器数据的复杂功能。

发明内容

总体上,本公开描述了一种或多种三维集成电路部件,三维集成电路部件包括呈竖直堆叠布置的、片上系统(SoC)晶粒和单独的静态随机存取存储器(static random-access memory,SRAM)子部件。本公开还描述了用于制造这种堆叠式SoC/SRAM集成电路部件的半导体制造方法。本公开还描述了多种设备和多种系统,例如人工现实(包括虚拟现实、增强现实和混合现实)设备和系统,在这些人工现实设备和系统中,这种堆叠式SoC/SRAM集成电路部件可以形成用于渲染人工现实图像的系统的一部分。

在一些示例中,SoC晶粒和SRAM子部件以竖直堆叠布置面对面地接合。此外,如所描述的,形成在SoC的有源电路外缘周围的非功能区中的多个硅通孔(through-siliconvias,TSV)用于将输入/输出(Input/Output,I/O)从SoC的有源侧引到相对侧。这些TSV可以形成为,从SoC的背侧到达SoC前侧上的多个焊盘。

通过将SRAM与SoC晶粒堆叠,与具有片上SRAM(on-die SRAM)的传统SoC相比,堆叠式SoC/SRAM集成电路部件的物理尺寸(例如,长度和宽度)可以显著减小。此外,与传统的片上SRAM相比,堆叠式SRAM子部件的物理尺寸可以增加。因此,堆叠式SRAM子部件可以提供足够的存储器容量,以执行传统SoC部件所需的片上SRAM和高速本地存储器两者的功能,从而消除对单独的高速本地存储器子部件的需求。本文所描述的堆叠式SoC/SRAM集成电路部件、以及所描述的用于制造该堆叠式SoC/SRAM集成电路部件的方法可以为片上SRAM的小型化问题提供技术解决方案,且还可以由于周边TSV所提供的信号路径的长度的减小而使得减少寄生效应并降低功耗。如本文所描述的,在非功能区中使用多个TSV也可以由于这些TSV不位于SoC晶粒的有源电路内而增加设计灵活性。此外,本文所描述的技术使SoC/SRAM堆叠的制造和多个TSV的形成能够根据需要而在多个单独的设施处进行,从而增加了制造灵活性并降低了成本。

在一个示例中,本公开针对一种人工现实系统,该人工现实系统包括被配置为输出人工现实内容的头戴式显示器(HMD),该HMD包括至少一个堆叠式集成电路部件,其中该至少一个堆叠式集成电路部件包括:SoC晶粒,该SoC晶粒具有前侧和背侧,其中SoC晶粒的前侧包括有源区,该有源区包括一个或多个有源元件,并且其中,SoC晶粒的前侧还包括位于有源区外侧的至少一个非有源区;静态随机存取存储器(SRAM)子部件,该SRAM子部件以面对面的竖直堆叠布置接合到SoC晶粒;以及多个硅通孔(TSV),该多个TSV形成为从SoC晶粒的背侧到达SoC晶粒的前侧,该多个TSV形成在该至少一个非有源区中。该至少一个非有源区可以位于有源区的外缘周围。该多个TSV可以形成在有源区的外缘周围的该至少一个非有源区中。该多个TSV可以形成为,在该至少一个非有源区中从SoC晶粒的背侧到达被图案化在SoC晶粒的前侧上的或前侧附近的多个焊盘。该系统还可以包括被图案化在SoC晶粒的背侧上的多个导电凸块。该系统还可以包括被图案化在SoC晶粒的背侧上的多个再分布层(redistribution layers,RDL)。

该系统还可以包括多个传感器,该多个传感器被配置为输出表示用户的运动的运动数据,其中SoC对接收到的来自多个传感器中的一个或多个传感器的、表示用户的运动的运动数据进行处理。该多个传感器可以包括至少一个惯性测量单元。该系统还可以包括一个或多个图像采集设备,该一个或多个图像采集设备被配置为输出表示与HMD的观察视角相对应的物理环境的图像数据,SoC对接收到的来自多个图像采集设备中的一个或多个图像采集设备的、表示物理环境的图像数据进行处理。SRAM子部件可以包括单个SRAM晶粒,或者可以包括多个SRAM晶粒的堆叠。

在另一示例中,本公开针对一种集成电路部件,该集成电路部件包括:SoC晶粒,该SoC晶粒具有前侧和背侧,其中SoC晶粒的前侧包括有源区,该有源区包括一个或多个有源元件,并且其中SoC晶粒的前侧还包括位于有源区外侧的至少一个非有源区;静态随机存取存储器(SRAM)子部件,该SRAM子部件以面对面的竖直堆叠布置接合到SoC晶粒;以及多个硅通孔(TSV),该多个TSV形成为从SoC晶粒的背侧到达SoC晶粒的前侧,该多个TSV形成在该至少一个非有源区中。

该至少一个非有源区可以位于有源区的外缘周围。该多个TSV可以形成在有源区的外缘周围的该至少一个无源区中。该多个TSV可以形成为,在该至少一个非有源区中从SoC晶粒的背侧到达被图案化在SoC晶粒的前侧上的或前侧附近的多个焊盘。SRAM子部件可以包括单个SRAM晶粒,或者可以包括多个SRAM晶粒的堆叠。集成电路部件还可以包括被图案化在SoC晶粒的背侧上的多个焊接凸块。集成电路部件还可以包括被图案化在SoC晶粒的背侧上的多个再分布层(RDL)。

在另一示例中,本公开针对一种方法,该方法包括:提供片上系统(SoC)晶粒,该SoC晶粒具有前侧和相对的背侧;以面对面的竖直堆叠布置将SoC晶粒的前侧接合到静态随机存取存储器(SRAM)子部件的前侧,其中,SoC晶粒的前侧包括有源区,该有源区包括一个或多个有源元件,并且其中,SoC晶粒的前侧还包括位于有源区外侧的至少一个非有源区;将SoC晶粒从第一厚度减薄到第二厚度,其中,第一厚度相对大于第二厚度,并且其中,该减薄包括从SoC晶粒的背侧减薄SoC晶粒;从SoC晶粒的背侧到SoC晶粒的前侧形成多个硅通孔(TSV),该多个TSV形成在该至少一个非有源区中;以及,从SoC晶粒的背侧到SoC晶粒的前侧金属化对该多个TSV金属化。

以面对面的竖直堆叠布置将SoC晶粒的有源侧接合到SRAM子部件的有源侧可以在第一制造设施处执行,并且将SoC晶粒从第一厚度减薄到第二厚度,从SoC晶粒的背侧到SoC晶粒的前侧形成多个硅通孔、以及从SoC晶粒的背侧对多个TSV金属化可以在第二不同制造设施处执行。

减薄SoC晶粒可以包括:在SoC晶粒的背侧上执行机械研磨工艺。可以通过后钻孔(via-last)硅通孔技术形成多个TSV。减薄SoC晶粒可以包括:将SoC晶粒的背侧从约775微米(micrometers,μm)的厚度减薄到约25μm至200μm范围内的厚度。减薄SoC晶粒可以包括:将SoC晶粒的背侧减薄到第二厚度,使得可以在不需要TSV显露工艺的情况下,从SoC晶粒的背侧到SoC晶粒的前侧上的多个焊盘形成多个TSV。将SoC晶粒从第一厚度减薄到第二厚度并且从SoC晶粒的背侧到SoC晶粒的前侧形成多个硅通孔(TSV)是在以面对面的竖直堆叠布置将SoC晶粒的前侧接合到静态随机存取存储器(SRAM)子部件的前侧之前进行的。

至少一个非有源区可以位于有源区的外缘周围。对多个TSV金属化还可以包括在至少一个非有源区中从SoC晶粒的背侧到被图案化在SoC晶粒的前侧上的多个焊盘对多个TSV金属化。SRAM子部件可以包括单个SRAM晶粒,或者可以包括多个SRAM晶粒的堆叠。

附图说明

图1是描绘了根据本公开所描述技术的包括集成电路(integrated circuit,IC)部件的示例人工现实系统的图示,该IC部件包括呈堆叠配置的SoC晶粒和SRAM子部件。

图2A是描绘了根据本公开所描述技术的包括IC部件的示例HMD的图示,该IC部件包括呈堆叠配置的SoC晶粒和SRAM子部件。

图2B是描绘了根据本公开所描述技术的包括IC部件的另一示例HMD的图示,该IC部件包括呈堆叠配置的SoC晶粒和SRAM子部件。

图3是显示了根据本公开所描述技术的、图1的人工现实系统的控制台和HMD的示例实施方式的框图。

图4是描绘了根据本公开所描述技术的图1的人工现实系统的示例HMD的框图。

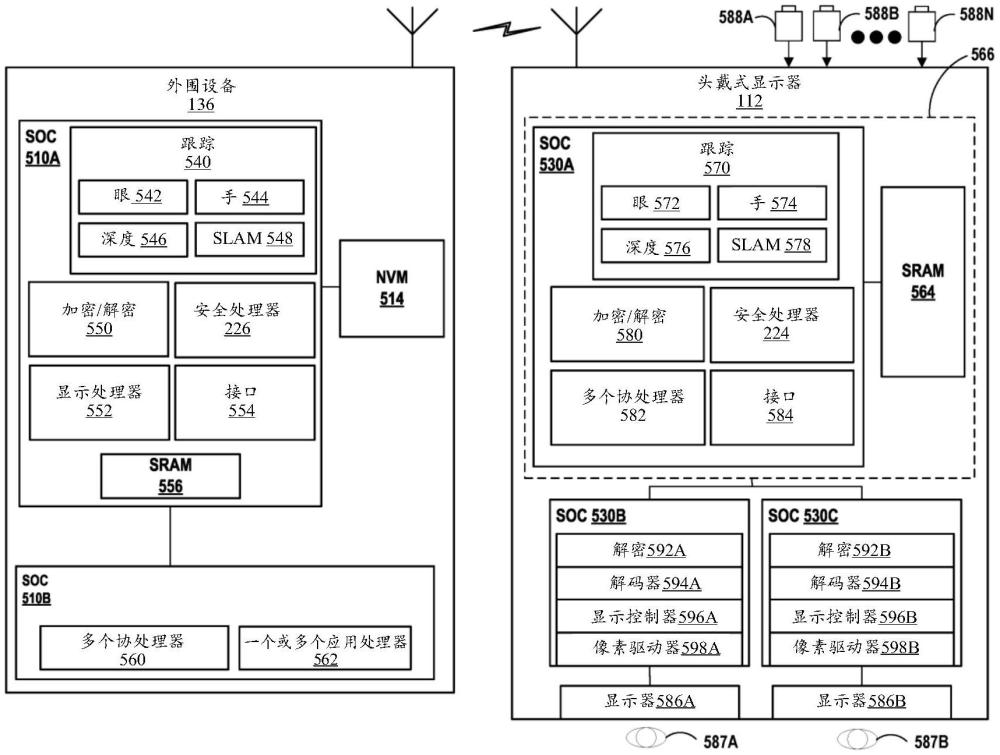

图5是示出了根据本公开技术的多设备人工现实系统的分布式架构的示例实施方式的框图,在该多设备人工现实系统中,一个或多个设备使用各设备内的一个或多个片上系统(SoC)集成电路来实现,并且该多设备人工现实系统具有无线通信系统。

图6是传感器聚集系统的框图,该传感器聚集系统可以包含根据本公开所描述技术的堆叠式SoC/SRAM集成电路部件。

图7A是根据本公开所描述技术的示例堆叠式SoC/SRAM集成电路部件沿图7B的线A-A'而截取的截面示意图。

图7B是从图7A的示例堆叠式SoC/SRAM集成电路部件中的SoC晶粒的正面俯视的示意图。

图8是根据本公开所描述技术的制造堆叠式SoC/SRAM集成电路部件的示例方法的流程图。

图9是根据本公开所描述技术的堆叠式SoC/SRAM部件的制造的示意图,该示意图说明了图8中的多个方法步骤。

具体实施方式

总体上,本公开描述了一种或多种三维集成电路(IC)部件,三维集成电路部件包括呈竖直堆叠布置的片上系统(SoC)晶粒和静态随机存取存储器(SRAM)子部件。本公开还描述了用于制造这种堆叠式SoC/SRAM集成电路部件的半导体制造方法。本公开还描述了多种设备,例如人工现实(包括虚拟现实、增强现实和混合现实)设备,在这些设备中,这种堆叠式SoC/SRAM集成电路部件可以形成用于渲染人工现实图像的系统的一部分。堆叠式SoC晶粒/SRAM部件可以与其它数字和模拟电路集成为一体,以形成小型化的显示封装,所述其他数字和模拟电路例如为主处理器、一个或多个传感器、显示器等。

在从AR/VR到自动驾驶和边缘人工智能(AI-at-the-edge)的各种系统中,通常被称为片上系统(SoC)的IC部件通常用于对传感器数据进行聚集和处理。在许多示例实施方式中,SoC典型地与主处理器和物理驱动系统通信。这种IC部件的内部结构通常包括SoC晶粒、高速本地存储器、和用于存储校准数据的可选非易失性存储器。此外,SoC晶粒本身具有片上SRAM,该片上SRAM用作高速缓冲存储器或者以其他方式实现SoC所执行的高速计算操作。传统的SoC集成电路部件包括具有片上SRAM的晶粒、以及与SoC及其片上SRAM分开或在SoC及其片上SRAM的外部的高速本地存储器子部件(例如,动态随机存取存储器(dynamicrandom-access memory,DRAM)),该片上SRAM典型地占据该晶粒的物理面积的30%至40%。然而,随着半导体工艺的进步不断实现了越来越小的最小特征尺寸,SRAM的物理尺寸却并没有相应地按比例缩小。因此,片上SRAM会限制这种传统SoC部件的小型化。

本公开描述了一种或多种三维集成电路部件,三维集成电路部件包括呈竖直堆叠布置的SoC晶粒和SRAM子部件。在一些示例中,SoC晶粒和SRAM子部件是面对面接合的。形成在SoC的有源电路的外缘周围的硅通孔(TSV)用于将输入/输出(Input/Output,I/O)从SoC的有源侧引到相对侧。这些TSV可以形成为,从SoC的背侧到达SoC前侧上的多个焊盘。

SRAM子部件可以是单个SRAM晶粒、或多个SRAM晶粒的小型堆叠(在本文中被称为“SRAM立方体”)。“SRAM立方体”样式可以有助于扩展SRAM的存储器容量,从而更容易消除对本地存储器(DRAM)的需求。

如本文所描述的,这些技术实现了根据具有第一阶段和第二阶段的多阶段工艺来制造堆叠式SoC/SRAM部件的制造工艺。该制造工艺的第一阶段包括对SoC晶粒和SRAM子部件进行面对面接合。可以在第一位置处执行该第一阶段,例如在第一半导体制造厂或代工厂处执行该第一阶段。在面对面接合期间,SoC I/O焊盘在没有中间的再分布层(RDL)布线的情况下直接连接到SRAM I/O焊盘,这以较低的功耗实现了较高的带宽和性能。该制造工艺的第二阶段包括在SoC有源电路的外缘周围形成多个TSV。该多个TSV可以形成为从SoC晶粒的背侧到达SoC晶粒的前侧上的多个焊盘。该制造工艺的第二阶段还包括对多个TSV的金属化、以及对SoC晶圆的背侧上的多个再分布层(RDL)的图案化。

在一些示例中,可以在第一位置处执行该制造工艺的第二阶段。在其它示例中,可以在第二不同位置处执行该制造工艺的第二阶段,例如在一不同的半导体制造和/或封装设施处执行该制造工艺的第二阶段。在与第一阶段不同的位置处执行该制造工艺的第二阶段的那些示例中,第二阶段还可以包括在形成该多个TSV之前将SoC晶粒减薄到期望的厚度。在那些示例中,在制造工艺的第一阶段期间生产的SoC晶粒的厚度可大于完成第二阶段之后的SoC晶粒的最终厚度,以有助于在第一位置和第二位置之间的装运和运输。因此,第二阶段可以包括对SoC晶粒进行减薄,例如通过将SoC晶片的背侧从第一厚度研磨到相对小于第一厚度的第二厚度。以这种方式,经减薄的SoC晶粒具有以下厚度尺寸:在该厚度尺寸中,可以在无需TSV显露工艺的情况下,从SoC晶粒的背侧到SoC晶粒的前侧上的多个焊盘形成该多个TSV。

通过将SRAM与SoC晶粒分开、并改为将SRAM作为堆叠配置中单独的子部件与SoC晶粒一起放置,与传统SoC(其中,SRAM与SoC电路一起形成在片上)相比,堆叠式SoC/SRAM部件的物理尺寸(例如,长度和/或宽度)可以显著减小。此外,与传统的片上SRAM相比,堆叠式SRAM子部件的物理尺寸可以增加。因此,堆叠式SRAM子部件可以提供足够的存储器容量来执行传统SoC部件所需的片上SRAM和高速本地存储器两者的功能,从而消除了对单独的高速本地存储器子部件的需求。堆叠式SoC/SRAM部件可以有助于解决片上SRAM的小型化问题,并且还可以由于凭借SRAM与SoC之间非常短的面对面互连以及TSV的短长度减小了所提供的信号路径的长度,而使得减少寄生效应并降低功耗。在非功能区中使用多个TSV还可以由于这些TSV不位于SoC晶粒的有源电路内而增加设计灵活性。此外,SoC/SRAM堆叠的制造以及多个TSV的形成可以在多个单独的设施处执行,从而增加了制造灵活性并降低了成本。

图1是描绘了根据本公开所描述技术的示例人工现实(AR)系统的图示,在该AR系统中,一个或多个堆叠式SoC/SRAM集成电路部件可以形成用于渲染人工现实图像的系统的一部分。该人工现实系统可以是虚拟现实系统、增强现实系统或混合现实系统。在图1的示例中,人工现实系统100包括头戴式显示器(HMD)112、一个或多个控制器114A和114B(统称为“一个或多个控制器114”),并且在一些示例中,人工现实系统100可以包括一个或多个外部的传感器90、和/或控制台106。

HMD 112典型地由用户110佩戴,并且包括用于向用户110呈现人工现实内容122的电子显示器和光学组件。另外,HMD 112包括用于跟踪HMD 112的运动的一个或多个传感器(例如,加速度计),并且可以包括用于采集周围物理环境的图像数据的一个或多个图像采集设备138(例如,摄像头、行扫描仪)。尽管被示出为头戴式显示器,但AR系统100可以替代地或附加地包括用于向用户110呈现人工现实内容122的眼镜或其他显示设备。

一个或多个控制器114中的每个控制器是一输入设备,用户110可以使用该输入设备来向控制台106、HMD 112、或AR系统100的另一部件提供输入。控制器114可以包括一个或多个存在敏感(presence-sensitive)表面,该一个或多个存在敏感表面用于通过检测触摸该存在敏感表面的多个位置的或悬停在该存在敏感表面的多个位置上方的一个或多个对象(例如,手指、手写笔)的存在,来检测用户输入。在一些示例中,一个或多个控制器114可以包括输出显示器,该输出显示器可以是存在敏感显示器。在一些示例中,一个或多个控制器114可以是智能电话、平板计算机、个人数据助理(personal data assistant,PDA)、或其他手持设备。在一些示例中,一个或多个控制器114可以是智能手表、智能戒指、或其他可穿戴设备。一个或多个控制器114还可以是自助服务终端(kiosk)的一部分、或其它静止或移动系统的一部分。替代地或附加地,一个或多个控制器114可以包括用于使用户能够与由AR系统100呈现给用户100的人工现实内容122的各方面进行交互、和/或使用户能够对该人工现实内容122的各方面进行控制的其他用户输入机构,例如,一个或多个按钮、一个或多个触发器、一个或多个控制杆、或一个或多个方向键(D-Pad)等。

在该示例中,控制台106被示出为单个计算设备,例如游戏控制台、工作站、台式计算机或膝上型计算机。在其他示例中,控制台106可以分布在多个计算设备上,例如分布在分布式计算网络、数据中心、或云计算系统上。如该示例中所示,控制台106、HMD 112和传感器90可以经由网络104而通信耦接,该网络104可以是有线网络或无线网络,例如Wi-Fi、网状网络或短距离无线通信介质、或它们的组合。尽管HMD 112在该示例中被显示为与控制台106通信(例如,有线连接到该控制台106或与该控制台106无线通信),但在一些实施方式中,HMD 112作为独立的移动AR系统来运行,并且AR系统100可以省略控制台106。

总体上,AR系统100渲染人工现实内容122,以供在HMD 112处向用户110显示。在图1的示例中,用户110观看由在HMD 112和/或控制台106上执行的人工现实应用程序所构建和渲染的人工现实内容122。在一些示例中,人工现实内容122可以是完全人工的,即,与用户110所处的环境不相关的图像。在一些示例中,人工现实内容122可以包括用于生成混合现实和/或增强现实的、真实世界图像(例如,用户110的手、一个或多个控制器114、用户110附近的其他环境对象)和虚拟对象120的混合。在一些示例中,可以将虚拟内容项目映射(例如,固定、锁定、放置)到人工现实内容122内的特定位置,例如人工现实内容122内相对于真实世界图像的特定位置。虚拟内容项目例如相对于墙壁或地球中的一者的位置可以是固定的。虚拟内容项目例如相对于一个或多个控制器114或用户的位置可以是可变化的。在一些示例中,虚拟内容项目在人工现实内容122内的特定位置与真实世界物理环境内的位置(例如,在物理对象的表面上的位置)相关联。

人工现实应用程序在运行期间,通过跟踪和计算参照系(frame of reference)的姿势信息(典型地是HMD 112的观察视角),来构造向用户110显示的人工现实内容122。人工现实应用程序使用HMD 112作为参照系并且基于通过HMD 112的当前估计姿势而确定的当前视场角,来渲染三维(3D)人工现实内容,在一些示例中,该3D人工现实内容可以至少部分地覆盖在用户110的真实世界3D物理环境上。在该过程期间,人工现实应用程序使用接收到的来自HMD 112和/或控制器114的感测数据(例如,移动信息和用户命令)、以及在一些示例中的来自任何外部传感器90(例如,外部摄像头)的数据,来采集真实世界物理环境内的3D信息,例如用户110的运动和/或与用户110有关的特征跟踪信息。人工现实应用程序基于该感测数据确定HMD 112的参照系的当前姿势,并根据当前姿势来渲染人工现实内容122。

AR系统100可以基于可通过用户的实时注视跟踪或其他条件而确定的用户110的当前视场角130,来触发对虚拟内容项目的生成和渲染。更具体地,HMD 112的图像采集设备138采集表示真实世界物理环境中的处于图像采集设备138的视场角130内的对象的图像数据。视场角130典型地与HMD 112的观察视角相对应。在一些示例中,人工现实应用程序呈现包括混合现实和/或增强现实的人工现实内容122。人工现实应用程序可以对例如人工现实内容122内的、与虚拟对象120一起位于视场角130内的真实世界对象的图像进行渲染,上述真实世界对象例如为,外围设备的多个部分、用户110的手、和/或用户110的手臂。在其他示例中,人工现实应用程序可以对人工现实内容122内的、位于视场角130内的外围设备的多个部分、用户110的手、和/或用户110的手臂的虚拟表示进行渲染(例如,将真实世界对象渲染为虚拟对象120)。在任一示例中,用户110能够观看到人工现实内容122内的以下中的多个部分:其手、其手臂、外围设备和/或位于视场角130内的任何其他真实世界对象。在其他示例中,人工现实应用程序可以不对用户110的手或手臂的表示进行渲染。

为了单独提供虚拟内容、或提供与场景中的真实世界对象叠加的虚拟内容,HMD112可以包括显示系统。例如,显示器可以包括投影仪和波导,该波导被配置为将投影仪输出的图像转移到用户的一只眼睛或两只眼睛可观看到的位置。投影仪可以包括显示器和投影仪透镜。波导可以包括用于将来自投影仪的光重定向到该波导中的输入光栅耦合器,并且该波导可以经由全内反射(total internal reflection,TIR)“困住(trap)”光。例如,显示器可以包括红色LED阵列、绿色LED阵列和蓝色LED阵列。在一些示例中,可以通过通过组合器对来自红色LED阵列、绿色LED阵列和蓝色LED阵列中的每一者的红色光、绿色光及蓝色光进行组合来形成彩色图像。波导可以包括用于将光例如朝向眼动范围(eyebox)而重定向到该波导之外的输出光栅。在一些示例中,投影仪透镜可以对来自显示器的光进行准直,例如,该显示器可以大体上位于投影仪透镜的焦点处。光栅耦合器可以将来自显示器的经准直的光重定向到波导中,并且该光可以经由波导的表面处的TIR而在该波导内传播。波导可以包括用于将来自该波导的光重定向到用户的眼睛的输出结构,该输出结构例如为,多个孔、多个凸块、多个点状物、全息光学元件(holographic optical element,HOE)、衍射光学元件(diffractive optical element,DOE)等,用户的眼睛将来自投影仪的显示器的经准直的光聚焦在用户的视网膜上,从而在用户的视网膜上重建显示图像。在一些示例中,波导的TIR起到镜子的作用并且不会显著影响显示器的图像质量,例如,用户对显示器的观看等同于观看镜子中的显示器。

如本文所进一步描述的,人工现实系统100的一个或多个设备(例如,HMD 112、多个控制器114、和/或控制台106)可以包括一个或多个SoC集成电路。此外,多个SoC中的一个SoC可以包括根据本文所描述技术的以竖直堆叠布置而布置和互连的SoC晶粒和SRAM子部件。

图2A是描绘了根据本公开所描述技术的、包括堆叠式SoC/SRAM集成电路部件的示例HMD 212A的图示。图2A中的HMD 212A可以是图1中的HMD 112的示例。如图2A所示,HMD212A可以采用眼镜的形式。HMD 212A可以是人工现实系统(例如,图1的AR系统100)的一部分,或者可以作为被配置为实现本文所描述技术的独立移动人工现实系统来运行。

在该示例中,HMD 212A是包括前框架的眼镜,该前框架包括允许HMD 212A停留在用户的鼻子上的鼻梁架、和延伸到用户的耳朵上以将HMD 212A固定到用户的眼镜腿(或“臂”)。此外,图2A中的HMD 212A包括一个或多个波导203A和203B(统称为“波导203”)、以及一个或多个波导输出结构205A和205B(统称为“波导输出结构205”),该一个或多个波导输出结构被配置为将光重定向到波导205A和205B外。在所示的示例中,投影仪148A和148B(统称为“投影仪248”)可以经由光栅耦合器(未示出)将光(例如,经准直的光)输入到波导203A和203B中,该光栅耦合器将来自投影仪248的光重定向到波导203中,使得经由该波导内的全内反射(TIR)“困住”该光。例如,投影仪248A和248B可以包括显示器和投影仪透镜。在一些示例中,波导203可以是透明的,并且替代地,波导203在下文中可以被称为“窗口203”。在一些示例中,当根据HMD 212A和用户的当前观察视角来跟踪HMD 212A的位置和方位、以用于渲染人工现实内容时,窗口203相对于HMD 212A的前框架的已知方位和位置被用作参照系,也称为本地原点。在一些示例中,投影仪248可以提供用于向用户的每只眼睛提供单独的图像的立体显示。

在所示的示例中,波导输出结构205覆盖窗口203的一部分,从而与视场角230的、用户通过窗口203可见的部分相对。在其他示例中,波导输出结构205可以覆盖窗口203的其他部分,或者窗口205的整个区域。

如图2A进一步所示,在该示例中,HMD 212还包括一个或多个运动传感器206、一个或多个集成的图像采集设备238A和238B(统称为“图像采集设备238”)、内部控制单元210,该内部控制单元210可以包括内部电源和一个或多个印刷电路板,该一个或多个印刷电路板具有一个或多个处理器、存储器和硬件,以提供用于执行可编程操作的操作环境,从而对感测数据进行处理并在波导输出结构205上呈现人工现实内容。根据本公开,内部控制单元210可以包括根据本公开的堆叠式SoC/SRAM集成电路部件,该堆叠式SoC/SRAM集成电路部件接收来自一个或多个传感器206中的一个或多个传感器、图像采集设备238、一个或多个控制器(例如,图1所示的一个或多个控制器114)和/或其它传感器的信息,并且形成计算系统的一部分,以对感测数据进行处理并在波导输出结构205上呈现人工现实内容。

图2B是描绘了包括多功能DOE的另一示例HMD的图示。HMD 212B可以是人工现实系统(例如,图1中的人工现实系统100)的一部分,或者可以作为被配置为实现本文所描述技术的独立的移动人工现实系统来运行。

在该示例中,HMD 212B包括前部刚性体和用于将HMD 212B固定到用户的带。另外,HMD 212B包括波导203(或者替代地,窗口203),该波导被配置为经由波导输出结构205向用户呈现人工现实内容。在所示的示例中,投影仪248可以经由输入光栅耦合器(未示出)将光(例如,经准直的光)输入到波导203中,该输入光栅耦合器将来自一个或多个投影仪248的光重定向到波导203中,使得经由波导203内的全内反射(TIR)“困住”该光。例如,投影仪248可以包括显示器和投影仪透镜。在一些示例中,当根据HMD 212B和用户的当前观察视角跟踪HMD 212B的位置和方位、以用于渲染人工现实内容时,波导203相对于HMD 212B的前部刚性体的已知方位和位置被用作参照系,也称为本地原点。在其他示例中,HMD 212B可以采用其他可穿戴头戴式显示器的形式,例如眼镜或护目镜。

图3是显示了根据本公开所描述技术的、包括控制台106和HMD 112的人工现实系统的示例实施方式的框图。在图3的示例中,控制台106基于感测数据(例如,接收到的来自HMD 112和/或外部传感器的运动数据和图像数据),来执行姿势跟踪、手势检测、以及HMD112的用户界面生成和渲染。

在该示例中,HMD 112包括一个或多个处理器302、和存储器304,在一些示例中,该一个或多个处理器和存储器提供用于执行操作系统305的计算机平台,该操作系统可以是例如嵌入式实时多任务操作系统或其他类型的操作系统。继而,操作系统305提供用于执行一个或多个软件构件307的多任务操作环境,该一个或多个软件构件包括应用程序引擎340。如关于图2A和图2B的示例所论述的,处理器302耦接到电子显示器303、运动传感器206、图像采集设备138,并且在一些示例中,该处理器302耦接到光学系统306。在一些示例中,处理器302和存储器304可以是单独的分立部件。在其它示例中,存储器304可以是与处理器302并置在单个集成电路内的片上(on-chip)存储器。在一些示例中,处理器302和/或存储器304用于对感测数据进行聚集和处理的功能可以被实现为根据本公开制造和布置的堆叠式SoC/SRAM集成电路部件。

在一些示例中,光学系统306可以包括如以上关于图2A和图2B所描述的、用于向用户呈现虚拟内容的投影仪和波导。例如,光学系统306可以包括投影仪,该投影仪包括电子显示器303和投影透镜。

通常,控制台106是计算设备,该计算设备对接收到的来自图像采集设备138的图像和跟踪信息进行处理,以执行手势检测和HMD 112的用户界面和/或虚拟内容生成。在一些示例中,控制台106是单个计算设备,例如工作站、台式计算机、膝上型计算机、或游戏系统。在一些示例中,控制台106的至少一部分(例如,处理器312和/或存储器314)可以分布在云计算系统上、数据中心上,或者可以分布在网络上,该网络例如为互联网、另一个公共或专用通信网络,该另一公共或专用通信网络例如为宽带、蜂窝、Wi-Fi、和/或用于在计算系统、服务器和计算设备之间传输数据的其他类型的通信网络。

在图3的示例中,控制台106包括一个或多个处理器312和存储器314,在一些示例中,该一个或多个处理器和存储器提供用于执行操作系统316的计算机平台,该操作系统可以是例如嵌入式实时多任务操作系统或其他类型的操作系统。继而,操作系统316提供用于执行一个或多个软件构件317的多任务操作环境。处理器312耦接到一个或多个I/O接口315,该一个或多个I/O接口315提供用于与多个外部设备通信的一个或多个I/O接口,这些外部设备例如为键盘、一个或多个游戏控制器、一个或多个显示设备、一个或多个图像采集设备、一个或多个HMD、一个或多个外围设备等。此外,该一个或多个I/O接口315可以包括用于与网络(例如,网络104)通信的一个或多个有线或无线网络接口控制器(networkinterface controller,NIC)。

控制台106的软件应用程序317运行以提供整体的人工现实应用程序。在该示例中,软件应用程序317包括应用程序引擎320、渲染引擎322、手势检测器324、姿势跟踪器326和用户界面(user interface,UI)引擎328。

总体上,应用程序引擎320包括提供和呈现人工现实应用程序的功能,该人工现实应用程序例如为电话会议应用程序、游戏应用程序、导航应用程序、教育应用程序、训练或模拟应用程序等。应用程序引擎320例如可以包括用于在控制台106上实现人工现实应用程序的一个或多个软件包、一个或多个软件库、一个或多个硬件驱动器、和/或一个或多个应用程序接口(Application Program Interface,API)。渲染引擎322响应于应用程序引擎320的控制,生成用于供HMD 112的应用程序引擎340向用户显示的3D人工现实内容。

应用程序引擎320和渲染引擎322根据如由姿势跟踪器326确定的参照系的当前姿势信息(典型地是HMD 112的观察视角),来构建用于向用户110显示的人工内容。渲染引擎322基于当前观察视角,构建3D人工现实内容,在一些情况下,该3D人工现实内容可以至少部分地覆盖在用户110的真实世界3D环境上。在该过程期间,姿势跟踪器326对接收到的来自HMD 112的感测数据(例如,移动信息和用户命令)进行操作、以及在一些示例中对来自任何外部传感器90(图1)(例如,外部摄像头)的数据进行操作,以采集真实世界环境内的3D信息,该3D信息例如为用户110的动作和/或与用户110有关的特征跟踪信息。姿势跟踪器326基于感测数据,确定HMD 112的参照系的当前姿势,并且根据当前姿势,来构建用于经由一个或多个I/O接口315传送到HMD 112、以用于向用户110显示的人工现实内容。

姿势跟踪器326可以确定HMD 112的当前姿势,并根据当前姿势来触发与任何渲染虚拟内容相关联的某些功能(例如,将虚拟内容项目放置到虚拟表面上、操纵虚拟内容项目、生成和渲染一个或多个虚拟标识、生成和渲染激光指示器)。在一些示例中,姿势跟踪器326检测HMD 112是否接近与虚拟表面(例如,虚拟钉板(virtual pinboard))相对应的物理位置,以触发对虚拟内容的渲染。

用户界面引擎328被配置为生成用于在人工现实环境中渲染的虚拟用户界面。用户界面引擎328生成包括一个或多个虚拟用户界面元素329的虚拟用户界面,该一个或多个虚拟用户界面元素例如为虚拟绘图界面、可选择菜单(例如,下拉菜单)、虚拟按钮、方向键(directional pad)、键盘,或者其他用户可选的用户界面元素、字形、显示元素、内容、用户界面控件等。

控制台106可以经由通信信道向HMD 112输出该虚拟用户界面和其他人工现实内容,以用于在HMD 112处显示。

手势检测器324基于来自图像采集设备138或其他传感器设备中的任何的感测数据,对所跟踪的控制器114和/或用户110的对象(例如,手、手臂、手腕、手指、手掌、拇指)的运动、布局、位置和/或方位进行分析,以识别用户110执行的一个或多个手势。更具体地,手势检测器324对在由HMD 112的图像采集设备138、和/或传感器90和外部摄像头102采集的图像数据内识别出的对象进行分析,以识别一个或多个控制器114、和/或用户110的手和/或手臂,并跟踪一个或多个控制器114、手和/或手臂相对于HMD 112的移动,从而识别由用户110执行的手势。在一些示例中,手势检测器324可以基于所采集的图像数据来跟踪一个或多个控制器114、手、手指和/或手臂的移动(包括位置和方位的变化),并且将这些对象的动作向量与手势库330中的一个或多个条目进行比较,以检测由用户110执行的一种手势或多种手势的组合。在一些示例中,手势检测器324可以接收由一个或多个控制器114的一个或多个存在敏感表面检测到的多个用户输入,并对这些用户输入进行处理,以检测由用户110相对于一个或多个控制器114执行的一个或多个手势。

图4是描绘了HMD 112是独立人工现实系统的示例的框图。在该示例中,与图3类似,HMD 112包括一个或多个处理器302、和存储器304,在一些示例中,该一个或多个处理器和存储器提供用于执行操作系统305的计算机平台,该操作系统可以是例如嵌入式实时多任务操作系统或其他类型的操作系统。继而,操作系统305提供用于执行一个或多个软件构件417的多任务操作环境。此外,一个或多个处理器302耦接到一个或多个电子显示器203、一个或多个变焦光学系统205、多个运动传感器206、以及多个图像采集设备138。在一些示例中,处理器302和/或存储器304用于对感测数据进行聚集和处理的功能可以被实现为根据本公开制造和布置的堆叠式SoC/SRAM集成电路部件。

在一些示例中,光学系统306可以包括如以上关于图2A和图2B所描述的、用于向用户呈现虚拟内容的投影仪和波导。例如,光学系统306可以包括投影仪,投影仪包括电子显示器303和投影透镜。该投影透镜还可以包括多功能DOE,该多功能DOE既用作用于将光重定向到波导中的光栅耦合器,又用作改善投影仪透镜的成像质量的透镜元件。

在图4的示例中,软件构件417运行以提供整体的人工现实应用程序。在该示例中,软件应用程序417包括应用程序引擎440、渲染引擎422、手势检测器424、姿势跟踪器426和用户界面引擎428。在各个示例中,软件构件417类似于图3中的控制台106的对应构件(例如,应用程序引擎320、渲染引擎322、手势检测器324、姿势跟踪器326、以及用户界面引擎328)来运行,以构建覆盖在用于向用户110显示的人工内容上、或作为该人工内容的一部分的虚拟用户界面。

与关于图3所描述的示例类似,手势检测器424基于来自以下中任何部件的感测数据:图像采集设备(例如,图像采集设备138、238或102)、一个或多个控制器114和/或其他传感器设备,对所跟踪的一个或多个控制器114和/或用户的对象(例如,手、手臂、手腕、手指、手掌、拇指)的运动、布局、位置和/或方位进行分析,以识别由用户110执行的一个或多个手势。

图5是示出了多设备人工现实系统的分布式架构的更详细的示例实施方式的框图,在该多设备人工现实系统中,一个或多个设备(例如,外围设备136和HMD 112)使用各设备内的一个或多个SoC集成电路来实现。图5示出了HMD 112结合外围设备136运行的示例。外围设备136代表具有一表面的物理真实世界设备,多设备人工现实系统(例如,系统100)将虚拟内容覆盖在该表面上。外围设备136可以包括具有一个或多个存在敏感表面的接口554,该一个或多个存在敏感表面用于通过检测触摸存在敏感表面的多个位置的或悬停在存在敏感表面的多个位置上方的一个或多个对象(例如,手指、手写笔等)的存在,来检测用户输入。在一些示例中,外围设备136可以具有类似于智能电话、平板计算机、个人数字助理(PDA)或其他手持设备中的任何的形状因子。在其他示例中,外围设备136可以具有智能手表、所谓的“智能戒指”或其他可穿戴设备的形状因子。外围设备136也可以是自助服务终端的一部分、或其他静止或移动系统的一部分。接口554可以包含用于向屏幕输出视觉内容的输出部件,例如一个或多个显示设备。如以上所描述的,HMD 112被设计且配置为使能够执行人工现实应用程序。

在该示例中,HMD 112包括多个SoC 530,且外围设备136包括多个SoC 510,该多个SoC 530和该多个SoC 510表示多个专用集成电路的集合,该多个专用集成电路的集合呈分布式架构布置、且被配置为提供人工现实应用程序的运行环境。作为示例,多个SoC集成电路可以包括作为协应用(co-application)处理器、传感器聚合器、加密/解密引擎、安全处理器、手/眼/深度跟踪和姿势计算元件、视频编码和渲染引擎、显示控制器和通信控制部件来运行的专用功能块。图5仅仅是多个SoC集成电路的一个示例布置。多设备人工现实系统的分布式架构可以包括多个SoC集成电路的任何集合和/或布置。

在图5的示例中,HMD 112包括根据本公开技术的堆叠式SoC/SRAM集成电路部件566。特别地,堆叠式SoC/SRAM集成电路部件566包括SoC 530A和SRAM 568。SRAM 568与SoC530A中的一个或多个处理器及其它片上电路分开,或者位于该一个或多个处理器及其它片上电路的外部(例如,不在片上)。在这个示例中,外围设备136使用传统的SoC架构来实现,在该传统的SoC架构中,SoC 510A包括片上SRAM 556和外部(片外(off-die))非易失性本地存储器(non-volatile local memory,NVM)514。相比之下,根据本公开的技术,SoC 530A不包括外部非易失性本地存储器;而是,堆叠式SoC/SRAM集成电路部件566的SRAM 568具有足够的存储器容量来执行传统片上SRAM(例如,SRAM 556)和外部非易失性本地存储器(例如,NVM 514)这两者的功能。

头戴式显示器(例如,如本文所描述的AR/VR系统中所使用的HMD 112)可以受益于堆叠式SoC/SRAM集成电路部件566所提供的减小的尺寸、增加的处理速度和降低的功耗。例如,由根据本公开技术的堆叠式SoC/SRAM集成电路部件566所提供的益处可以使得增加佩戴者的舒适度并使得具有更完全沉浸和逼真的AR/VR体验。

此外,应理解的是,SoC 510和/或SoC 530中的任何都可以使用根据本公开技术的堆叠式SoC/SRAM集成电路部件来实现,并且本公开不限于这一方面。SoC 510和/或SoC 530中的任何可以受益于由堆叠式SoC/SRAM集成电路部件566所提供的减小的尺寸、增加的处理速度和降低的功耗。此外,由根据本公开技术的堆叠式SoC/SRAM部件所提供的益处不但对AR/VR系统是有利的,而且在许多应用中也是有利的,这些应用例如为自动驾驶、基于边缘的人工智能、物联网、以及需要基于对来自大量传感器输入的数据的分析而进行的高响应、实时决策能力的其它应用。

在该示例中,HMD 112的SoC 530A包括多个功能块,这些功能块包括安全处理器224、跟踪570、加密/解密580、协处理器582以及接口584。跟踪570提供用于眼跟踪572(“眼572”)、手跟踪574(“手574”)、深度跟踪576(“深度576”)和/或同步定位与地图构建(Simultaneous Localization and Mapping,SLAM)578(“SLAM 578”)的功能块。例如,HMD112可以接收来自一个或多个加速度计(也称为惯性测量单元或“IMU”)、GPS传感器、雷达或声纳、或其他传感器的输入,该一个或多个加速度计输出指示HMD 112的当前加速度的数据,该GPS传感器输出指示HMD 112的位置的数据,该雷达或声纳输出指示HMD 112距各个对象的距离的数据,该其他传感器提供对HMD 112或物理环境内的其他对象的位置或方位的指示。HMD 112还可以接收来自一个或多个图像采集设备588A至588N(统称为“图像采集设备588”)的图像数据。图像采集设备可以包括被配置为输出表示物理环境的图像数据的、摄像头、激光扫描仪、多普勒雷达扫描仪、深度扫描仪等。更具体地,图像采集设备采集表示物理环境中在图像采集设备的视场角内的对象(包括外围设备136和/或手)的图像数据,该视场角典型地对应于HMD 112的观察视角。跟踪570基于感测数据和/或图像数据,例如确定HMD 112的参照系的当前姿势,并根据当前姿势来渲染人工现实内容。

SoC 530A的加密/解密580是用于加密向外围设备136或安全服务器传送的传出数据、且解密从外围设备136或安全服务器传送的传入数据的功能块。协应用处理器582包括用于执行多个指令的一个或多个处理器,该一个或多个处理器例如为视频处理单元、图形处理单元、数字信号处理器、编码器和/或解码器、和/或其他。

SoC 530A的接口584是包括一个或多个接口的功能块,该一个或多个接口用于连接到SoC 530B和/或SoC 530C的功能块。作为一个示例,接口584可以包括外围组件快速互连(peripheral component interconnect express,PCIe)插槽。SoC 530A可以使用接口584与SoC 530B、SoC 530C连接。SoC 530A可以使用接口584与通信设备(例如,无线电发射器)连接,以用于与其它设备(例如,外围设备136)通信。

HMD 112的SoC 530B和SoC 530C各自表示用于在相应显示器(例如,显示器586A、显示器586B(统称为“显示器586”))上输出人工现实内容的显示控制器。在该示例中,SoC530B可以包括用于供显示器568A为用户的左眼587A输出人工现实内容的显示控制器。例如,SoC 530B包括用于在显示器586A上输出人工现实内容的、解密块592A、解码器块594A、显示控制器596A和/或像素驱动器598A。类似地,SoC 530C可以包括用于供显示器568B为用户的右眼587B输出人工现实内容的显示控制器。例如,SoC 530C包括用于生成并在显示器586B上输出人工现实内容的、解密592B、解码器594B、显示控制器596B和/或像素驱动器598B。显示器568可以包括发光二极管(LED)显示器、有机LED(Organic LED,OLED)、量子点LED(Quantum dot LED,QLED)、电子纸(Electronic paper,E-ink)显示器、液晶显示器(Liquid Crystal Display,LCD)、或用于显示AR内容的其它类型的显示器。

在该示例中,外围设备136包括被配置为支持人工现实应用的SoC 510A和SoC510B。在这个示例中,SoC 510A包括多个功能块,这些功能块包括安全处理器226、跟踪540、加密/解密550、显示处理器552和接口554。跟踪540是提供眼跟踪542(“眼542”)、手跟踪544(“手544”)、深度跟踪546(“深度546”)、和/或同步定位与地图构建(SLAM)548(“SLAM 548”)的功能块。例如,外围设备136可以接收来自一个或多个加速度计(也称为惯性测量单元或“IMU”)、GPS传感器、雷达或声纳、或其他传感器的输入,该一个或多个加速度计输出指示外围设备136的当前加速度的数据,GPS传感器输出指示外围设备136的位置的数据,雷达或声纳输出指示外围设备136距各个对象的距离的数据,该其他传感器提供对外围设备136或物理环境内的其他对象的位置或方位的指示。在一些示例中,外围设备136还可以接收来自被配置为输出表示物理环境的图像数据的一个或多个图像采集设备的图像数据,该一个或多个图像采集设备例如为摄像头、激光扫描仪、多普勒雷达扫描仪、深度扫描仪等。跟踪块540基于感测数据和/或图像数据,例如确定外围设备136的参照系的当前姿势,并根据当前姿势向HMD 112渲染人工现实内容。

SoC 510A的加密/解密550对向HMD 112或安全服务器传送的传出数据进行加密,并且对从HMD 112或安全服务器传送的传入数据进行解密。加密/解密550可以支持对称密钥加密以使用会话密钥(例如,秘密对称密钥)来加密/解密数据。SoC 510A的显示处理器552包括用于向HMD 112渲染人工现实内容的一个或多个处理器,该一个或多个处理器例如为视频处理单元、图形处理单元、编码器和/或解码器、和/或其他。SoC 510A的接口554包括用于连接到SoC 510A的多个功能块的一个或多个接口。作为一个示例,接口584可以包括外围组件快速互连(peripheral component interconnect express,PCIe)插槽。SoC 510A可以使用接口584与SoC 510B连接。SoC 510A可以使用接口584与一个或多个通信设备(例如,无线电发射器)连接,以用于与其他设备(例如,HMD 112)通信。

外围设备136的SoC 510B包括协应用处理器560和应用处理器562。在该示例中,协应用处理器560包括各种处理器,例如视觉处理单元(vision processing unit,VPU)、图形处理单元(graphics processing unit,GPU)和/或中央处理单元(central processingunit,CPU)。应用处理器562可以执行一个或多个人工现实应用程序,例如以生成和渲染人工现实内容、和/或检测和解释用户相对于外围设备136执行的手势。

图6是另一示例系统(即,该示例中的传感器聚集系统600)的框图,该示例系统可以包含根据本公开的堆叠式SoC/SRAM集成电路部件。在该示例中,传感器聚集系统600包括主处理器604、聚集引擎602、可选的控制电路606、传感器610和物理驱动系统608。在该示例中,聚集引擎602可以使用根据本公开的堆叠式SoC/SRAM集成电路部件来实现。这种传感器聚集系统600的多个示例包括AR/VR系统、自动驾驶系统和基于边缘的人工智能(artificial intelligence,AI)系统。这种应用需要基于对来自大量传感器输入的数据的分析而进行的高响应、通常是实时的决策能力。此外,通常期望减小这种系统的电子部件的尺寸和/或重量。这种小型化可以使得提高佩戴者的舒适度(例如,如在本文所描述的AR/VR系统的情况下)、提高处理速度和/或降低功耗。

在AR/VR应用(例如,图1至图5所描述的那些)中,一个或多个传感器610可以包括一个或多个惯性测量单元(IMU),每个IMU包括一个或多个加速计和/或陀螺仪,该一个或多个加速度计和/或陀螺仪用于跟踪佩戴在用户头部上的HMD的运动、和/或用于跟踪被保持或附接到用户的手的一个或多个控制器的运动。一个或多个传感器610还可以包括用于采集周围物理环境的图像数据的一个或多个图像采集设备,例如摄像头或行扫描仪。驱动系统608包括显示部件(例如,HMD),该显示部件显示如由主处理器604确定的增强现实内容或虚拟现实内容。聚集引擎602将从一个或多个传感器610接收到的原始传感器数据聚集成供主处理器604分析的形式。主处理器604对经聚集的传感器数据进行分析,并基于该分析生成待由驱动系统608显示的人工现实内容。在该示例中,聚集引擎602可以用根据本公开所描述技术的堆叠式SoC/SRAM集成电路部件来实现。

图7A是根据本公开所描述技术的示例堆叠式SoC/SRAM集成电路部件沿图7B的线A-A'截取的截面示意图。图7B是从图7A的示例堆叠式SoC/SRAM集成电路部件的SoC晶粒的正面俯视的示意图。堆叠式SoC/SRAM集成电路部件700包括以竖直堆叠布置面对面接合的SoC晶粒702和SRAM子部件712。SoC晶粒702包括有源侧704和相对的非有源侧706。SRAM子部件712类似地包括有源侧714和相对的非有源侧716。为了形成面对面接合(由互连点730表示),SoC晶粒702的有源侧704上的多个I/O焊盘在没有中间的再分布层(RDL)布线的情况下、被直接连接到SRAM子部件712的有源侧712上的多个I/O焊盘。互连点可以是形成在SoC或SRAM上的导电凸块(例如,铜(Cu)或焊料)、或由介电层(例如,氧化物、氮化物或碳化物)包围的导电焊盘(例如,Cu);并且这些互连可以通过焊料回流工艺、热压接合工艺或混合电介质到电介质接合工艺来形成。SoC晶粒702与SRAM子部件712之间的这种面对面接合以较低的功耗实现了较高的带宽和性能。

SRAM子部件可以是单个SRAM晶粒、或在本文中被称为“SRAM立方体”的多个SRAM晶粒的小型堆叠。“SRAM立方体”样式可以帮助扩展SRAM子部件的存储器容量,从而使得更容易消除对本地存储器(动态随机存取存储器(DRAM))的需求。因此,尽管SRAM子部件被显示为单个SRAM晶粒,但应理解的是,本公开并不限于这一方面。

堆叠式SoC/SRAM部件700还包括多个TSV,例如TSV 720A和720B,TSV 720A和720B在本文中统称为TSV 720。TSV 720用于将输入/输出(I/O)从SoC晶粒702的有源侧704引出到相对的非有源侧706。沿着晶粒的周边可以布置一行或多行TSV,以构成应用所需的、所需数量的I/O。例如,在图7A和图7B中,沿着晶粒周边的每一侧有两行TSV。这些TSV不一定是按比例示出的,而是仅用于说明性目的。应理解的是,可以使用任何合适行数的TSV或TSV的其他布置,并且每侧可以根据应用的需要而包括不同布置的TSV,且本公开不限于这一方面。

SoC晶粒702的有源侧704包括由虚线表示的有源区(在本文中也被称为功能区)708。有源区708包括形成在SoC晶粒702的有源侧704上的一个或多个有源元件(例如,晶体管)。SoC晶粒702的有源侧704还包括大体上位于有源区708的外缘周围的多个非有源区或非功能区710。非有源区710在其不包括任何有源元件的意义上是非功能性的。在这个示例中,多个TSV形成为,从SoC晶粒702的非功能区710中的背侧到达SoC晶粒702的前侧上的焊盘。这些焊盘可以位于侧702的前侧上、或者稍微凹入或嵌入在前侧之下。SoC晶粒702的背侧706包括多个再分布层(RDL)、和多个导电凸块或焊盘740,这些导电凸块或焊盘用于将堆叠式SoC/SRAM部件700连接到其它集成电路部件,以形成完整系统。例如,堆叠式SoC/SRAM集成电路部件700可以连接到其它集成电路部件,以形成用于渲染人工现实图像的系统的一部分。

图8和图9示出了制造堆叠式SoC/SRAM集成电路部件(例如,如图7A和图7B所示的堆叠式SoC/SRAM集成电路部件)的示例方法;将同时对图8和图9进行描述。图8是根据本公开所描述技术的制造堆叠式SoC/SRAM集成电路部件的示例方法的流程图。图9是根据本公开所描述技术的堆叠式SoC/SRAM部件的制造的示意图,该示意图示出了图8中的多个方法步骤。

堆叠式SoC/SRAM部件的示例制造工艺(800)可以包括第一阶段(820)和第二阶段(840)。制造工艺(800)的第一阶段(820)包括对SoC晶粒和SRAM子部件的面对面接合(802)。第一阶段可以在第一位置处执行,该第一位置例如为第一半导体制造厂或代工厂。在面对面接合期间,SoC I/O焊盘在没有中间的再分布层(RDL)布线的情况下而直接连接到SRAMI/O焊盘,这以较低的功耗实现了较高的带宽和性能。

该制造工艺的第二阶段(840)包括在SoC有源电路的外缘周围的非功能区中形成多个TSV(806)。该多个STV可以形成为,从SoC晶粒的背侧到达SoC晶粒的前侧上的多个焊盘。在一些示例中,可以使用所谓的后钻孔硅通孔技术来形成该多个TSV。该制造工艺的第二阶段(840)还包括对该多个TSV的金属化和对SoC晶粒的背侧上的再分布层(RDL)的图案化(808)。

在一些示例中,可以在第一位置处执行制造工艺(800)的第二阶段(840)。在其它示例中,可以在第二不同位置(例如,一不同的半导体制造和/或封装设施)处执行第二阶段(840)。在与第一阶段不同的位置处执行制造工艺的第二阶段(840)的那些示例中,第二阶段(840)还可以包括在形成该多个TSV之前将SoC晶粒减薄到所期望的厚度(804)。在那些示例中,从制造工艺的第一阶段(820)产生的SoC晶粒的厚度可以相对大于SoC晶粒的最终厚度,以有助于在第一位置和第二位置之间的装运和运输。对SoC晶粒的减薄(804)可以包括将SoC晶圆的背侧从第一厚度向下研磨(或背侧研磨)到第二厚度,其中第一厚度相对大于第二厚度。在一些示例中,第二厚度使得经减薄的SoC晶粒具有如下厚度尺寸:在该厚度尺寸中,可以在无需TSV显露工艺的情况下、从SoC晶粒的背侧到SoC晶粒的前侧上的多个焊盘形成多个TSV。在一个示例中,第一厚度可以是约775微米(μm),第二厚度可以在约25μm至200μm的范围内。然而,应理解的是,本公开不限于本文所描述的特定厚度,并且可以使用任何合适的厚度来完成制造工艺(800)。

在一些示例中,TSV的尺寸可以是直径约30μm、且高度约150μm、且间距约100μm的量级(TSV的高度大致等于硅晶粒的厚度)。沿着晶粒的周边可以布置一行或多行TSV,以构成应用所需的、所需数量的IO。对于典型的AR/VR应用,以晶粒每单位面积的IO数表示的归一化TSV密度可以在每平方毫米(mm

如图9所示,堆叠式SoC/SRAM部件的示例制造工艺可以包括由附图标记920所指示的第一阶段和由附图标记940所指示的第二阶段。制造工艺的第一阶段920包括对SoC晶粒702和SRAM子部件704的面对面接合。第一阶段可以在第一位置(例如,第一半导体制造厂或代工厂)处执行。在面对面接合(由焊接凸块730表示)期间,SoC晶粒702的有源侧704上的I/O焊盘直接连接到SRAM子部件704的有源侧714上的I/O焊盘。

制造工艺的第二阶段940可以包括对SoC晶粒702的减薄。减薄可以通过将SoC晶粒从由附图标记732所指示的第一厚度背侧研磨到由附图标记734所指示的第二厚度来完成。第一厚度732相对大于第二厚度734。在一个示例中,第一厚度732可以是约775微米(μm),且第二厚度734可以在约25μm至200μm的范围内。

第二阶段940包括在SoC有源电路708的外缘周围的非功能区710中形成多个TSV720。在这个示例中,从SoC晶粒的背侧706到SoC晶粒的前侧704上的焊盘形成多个TSV 720。在减薄过程期间,可以选择第二厚度,使得可以在无需TSV显露工艺的情况下、在SoC晶粒中形成多个TSV 720。制造工艺的第二阶段940还包括对多个TSV 720的金属化和对SoC晶粒702的背侧706上的再分布层(RDL)和导电凸块或焊盘730的图案化。

在一些示例中,制造工艺的第一阶段920和第二阶段940均可以在第一位置(例如,第一半导体制造厂或代工厂)处执行。在那些示例中,第二阶段不一定需要包括将SoC晶粒从第一厚度732减薄到第二厚度734。例如,如果在完成第一阶段920之后、第一厚度734使得可以在无需TSV显露工艺的情况下、在SoC晶粒702的非功能区中形成多个TSV,则可以省略减薄步骤。在其他示例中,第二阶段940可以在第二不同位置(例如,第二不同半导体制造和/或封装设施)处执行。在与第一阶段不同的位置处执行制造工艺的第二阶段940的那些示例中,第二阶段940可以包括在形成多个TSV 720之前将SoC晶粒从第一厚度732减薄到第二厚度734。例如,完成第一阶段920之后的第一厚度可以被选择为帮助装运和运输面对面接合的SoC晶粒702和SRAM子部件704。

例如,在一些AR/VR应用中,堆叠式SoC/SRAM部件的I/O密度使得可以在有源SoC电路外缘周围的非功能区中形成多个TSV 720,从而允许在与制造工艺的第一阶段920不同的设施和/或位置处完成制造工艺的第二阶段940。TSV设计和制造通常是保密的且是在特定代工厂进行的,并且如果多个TSV被插入到SoC晶粒的有源区内,则TSV设计和制造还会影响SoC有源电路的布局。本公开的技术使制造工艺的第二阶段940(TSV制造)能够与第一阶段920(SoC晶粒制造和/或面对面接合)分开执行,这意味着堆叠式SoC/SRAM集成电路部件的SoC设计更容易从一个代工厂转移到另一个代工厂。此外,在非功能区中使用TSV还可以由于周边TSV所提供的信号路径的长度减小而使得减少寄生效应并降低功耗。

通过将SRAM与SoC晶粒堆叠,与具有片上SRAM的传统SoC相比,堆叠式SoC/SRAM集成电路部件的物理尺寸(例如,长度和宽度)可以显著减小。此外,与传统的片上SRAM相比,堆叠式SRAM子部件的物理尺寸可以增加。堆叠式SRAM子部件由此可以提供足够的存储器容量,来执行传统SoC部件所需的片上SRAM及高速本地存储器这两者的功能,从而消除对单独的高速本地存储器子部件的需求。本文所描述的堆叠式SoC/SRAM集成电路部件、以及所描述的用于制造该堆叠式SoC/SRAM集成电路部件的方法可以为片上SRAM的小型化问题提供技术解决方案,并且还可以由于周边TSV所提供的信号路径的长度减小而使得减少寄生效应并降低功耗。如本文所描述的、在非功能区中使用TSV也可以由于TSV不位于SoC晶粒的有源电路内而增加设计灵活性。此外,本文所描述的技术使SoC/SRAM堆叠的制造和多个TSV的形成能够根据需要而在多个单独的设施处执行,从而增加了制造灵活性并降低了成本。

以下可以对与具有片上SRAM的传统SoC相比、堆叠式SoC/SRAM子部件对所得到的集成电路部件的物理尺寸和存储器容量的影响的示例进行描述。具有片上SRAM的传统SoC的物理尺寸可以是约25mm

再次参考图8和图9,在另一示例中,制造工艺的第一阶段820和920以及第二阶段840和940可以在远离制造SoC晶粒和SRAM子部件的一个或多个位置处执行。在该示例中,制造工艺的第一阶段820和920(SoC晶粒和SRAM子部件的面对面接合)以及第二阶段840和940(TSV的形成)可以例如在封装设施中执行,该封装设施的位置不同于制造SoC和SRAM子部件本身的晶圆制造厂或代工厂。在这种情况下,由于不涉及装运到一不同的位置,因此第一阶段820和920以及第二阶段840和940的顺序可以颠倒(即,首先进行TSV形成,然后进行面对面接合)。

如本文通过各种示例所描述的,本公开的技术可以包括人工现实系统或结合人工现实系统来实现。如所描述的,人工现实是在呈现给用户之前已经以某种方式进行了调整的现实形式,该现实形式例如可以包括虚拟现实(VR)、增强现实(AR)、混合现实(MR)、混合现实(hybrid reality)、或它们的某种组合和/或衍生物。人工现实内容可以包括完全生成的内容、或与采集的内容(例如,真实世界照片或视频)相结合的生成的内容。人工现实内容可以包括视频、音频、触觉反馈或它们的某种组合,并且以上中的任何可以在单个通道或多个通道(例如,向观看者产生三维效果的立体视频)中呈现。另外,在一些示例中,人工现实可以与应用、产品、配件、服务或它们的某种组合相关联,应用、产品、配件、服务或它们的某种组合例如用于在人工现实中创建内容和/或在人工现实中使用(例如,在人工现实中执行活动)。提供人工现实内容的人工现实系统可以在各种平台上实现,这些平台包括连接到主计算机系统的HMD、独立HMD、移动设备或计算系统、或能够向一位或多位观看者提供人工现实内容的任何其他硬件平台。

本公开所描述的技术可以至少部分地以硬件、软件、固件或它们的任何组合来实现。例如,所描述的技术的各个方面可以在一个或多个处理器内实现,该一个或多个处理器包括一个或多个微处理器、一个或多个数字信号处理器(DSP)、一个或多个专用集成电路(specific integrated circuit,ASIC)、一个或多个现场可编程门阵列(fieldprogrammable gate array,FPGA)、或任何其它等效集成电路或分立逻辑电路、以及这些部件的任何组合。术语“处理器”或“处理电路”一般可以指单独的前述逻辑电路、或与其它逻辑电路相结合的前述逻辑电路、或任何其它等效电路中的任何。包括硬件的控制单元也可以执行本公开的多种技术的一种或多种。

这种硬件、软件和固件可以在支持本公开所描述的各种操作和功能的同一设备内或多个分开的设备内实现。另外,所描述的多个单元、多个模块或多个部件中的任何可以一起实现、或单独地实现为多个分立但可互操作的逻辑设备。将不同特征描述为模块或单元旨在强调不同的功能方面,并不一定暗指这些模块或单元必须由单独的硬件或软件构件来实现。而是,与一个或多个模块或单元相关联的功能可以由单独的硬件或软件构件执行,或者可以集成在共同的或单独的硬件或软件构件内。

本公开所描述的技术也可以在包含多个指令的计算机可读介质(例如,计算机可读存储介质)中体现或编码。在计算机可读存储介质中体现或编码的多个指令可以使得可编程处理器或其他处理器例如在执行多个指令时来执行该方法。计算机可读存储介质可以包括随机存取存储器(random access memory,RAM)、只读存储器(read only memory,ROM)、可编程只读存储器(programmable read only memory,PROM)、可擦除可编程只读存储器(erasable programmable read only memory,EPROM)、电子可擦除可编程只读存储器(electronically erasable programmable read only memory,EEPROM)、闪存、硬盘、紧凑型光盘只读存储器(CD-ROM)、软盘、盒式磁带、磁介质、光介质、或其它计算机可读介质。